可改良感测放大时序适应性的存储模块的制作方法

- 国知局

- 2024-07-31 19:12:05

本发明涉及一种可改良感测放大时序适应性的存储模块,且特别涉及一种可使感测放大器使能的时间长短适应输出入数目及/或感测放大器供应电压的存储模块。

背景技术:

1、存储模块,例如嵌入式静态随机存取存储模块,是集成电路(半导体芯片)的重要基础构筑方块。

2、存储模块中设有多个存储单元与多个感测放大器;这些感测放大器受控于一使能信号。当使能信号被激发时,各感测放大器会使能而运行;当使能信号被停止激发时,各感测放大器便会失能而不运行。

3、当存储模块要在一读取回合(read cycle)中读出一存储单元中存储的数据时,该存储单元对应的位元线会被导通至一对应的感测放大器,然后使能信号会被激发,使该感测放大器使能以感测该对应位元线的电压,并据以判断该存储单元存储的数据;之后,使能信号会被停止激发,使该感测放大器失能而停止感测,该读取回合也就此结束。在各读取回合中,感测放大器使能运行的时间长短取决于使能信号被激发的时间长短,也就是使能信号的脉宽。若使能信号的脉宽不足,感测放大器使能运行的时间就会不足,数据读取的正确性也会连带受影响。

4、在现有技术中,现有存储模块会设置固定数目个串接的反相器,使能信号的脉宽就取决于这些串接反相器的门延迟(gate delay)总和。因此,在现有技术中,使能信号的脉宽缺乏弹性,难以适应各种存储模块的不同需求。并且,这些串接反相器也会占用不少布局面积。

技术实现思路

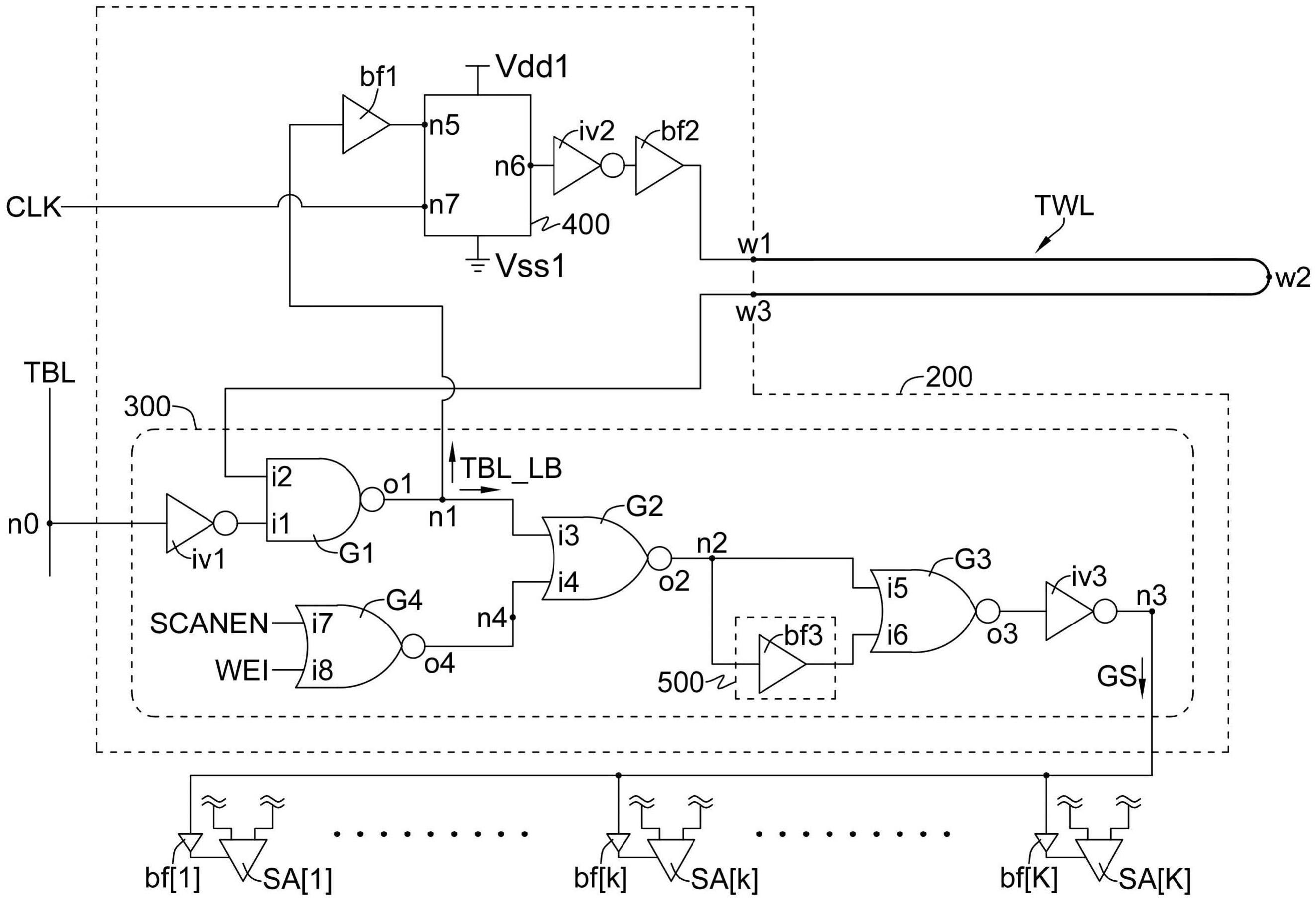

1、本发明的目的之一是提供一种可改良感测放大时序适应性的存储模块(例如100,图1),包含至少一位元线(例如bl[q])、至少一字元线(例如wl[p])、一追随位元线(例如tbl)、一追随字元线(例如twl)、至少一存储单元(例如c[p,q])、至少一追随单元(例如tc[p])、至少一感测放大器(例如sa[k])与一脉宽控制器(例如300,图4)。该追随字元线包含一前节点(例如w1)与一后节点(例如w3),且于该前节点与该后节点间的长度正相关于各该字元线的长度。各该存储单元耦接该至少一位元线的其中之一以及该至少一字元线的其中之一。各该追随单元耦接该追随位元线。各该感测放大器耦接该至少一位元线的其中之一,并接收一使能信号(例如gs);各该感测放大器在该使能信号被激发(activated)时受控使能,并在该使能信号被停止激发时失能。脉宽控制器耦接于该追随位元线、该前节点与该后节点,并提供该使能信号。其中,当该追随位元线的电压(例如vtbl,图5)改变至一预设电压时(例如vt0,在时点t3,图5),该脉宽控制器激发该使能信号(例如在时点t6,图5),并使该前节点的电压(例如vw1,图5)改变(例如在时点t7开始由电压v4切换至电压v3,图5)。当该前节点的电压改变,该追随字元线在一第一延迟时间(例如d1,图5)后使该后节点的电压(例如vw3,图5)改变(例如在时点t8开始由电压v4切换至电压v3,图5)。当该后节点的电压改变,该脉宽控制器在一第二延迟时间(例如d2,图5)后停止激发该使能信号(例如在时点t12,图5)。

2、一实施例中(例如图6),该脉宽控制器有一部分(例如逻辑门g1,图6)由一第一供应电压(例如vdd1,图6)供电,各该感测放大器(例如sa[k],图6)至少有一部分(例如s2[k],图6)由一第二供应电压(例如vdd2,图6)供电。一实施例中,该第一供应电压与该第二供应电压相异,且该第二延迟时间的长短负相关于该第二供应电压的大小。

3、一实施例中(例如图6),该脉宽控制器有两部分(例如逻辑门g1与延迟电路500,图6)分别由两相异供应电压(例如vdd1与vdd2,图6)供电,且该第二延迟时间的长短负相关于该两相异供应电压的其中之一(例如vdd2,图6)。

4、一实施例中(例如图4),该脉宽控制器包含一第一逻辑门(例如g1,图4)。该第一逻辑门包含一第一输入端(例如i1)、一第二输入端(例如i2)与一第一输出端(例如o1),分别耦接该追随位元线、该后节点与一第一节点(例如n1)。该脉宽控制器于一第三节点(例如n3)形成该使能信号,该第三节点耦接该至少一感测放大器。当该存储模块进行数据读取时,该第三节点的电压受控于该第一节点的电压。当该脉宽控制器激发该使能信号时,使该使能信号由一第一电平(例如v1,图5)切换至一第二电平(例如v2,图5);当该脉宽控制器停止激发该使能信号时,使该使能信号由该第二电平切换回该第一电平。一实施例中(例如图4),该脉宽控制器还包含一第一反相器(例如iv1,图4),耦接于该追随位元线与该第一输入端之间。一实施例中(例如图4),该第一逻辑门是一与非门。

5、一实施例中(例如图4),该脉宽控制器还包含一第三逻辑门(例如g3,图4)与一延迟电路(例如500,图4)。该第三逻辑门包含一第五输入端(例如i5)、一第六输入端(例如i6)与一第三输出端(例如o3)。该第五输入端耦接一第二节点(例如n2),该延迟电路耦接于该第二节点与该第六输入端之间,且该第三输出端耦接该第三节点。当该存储模块进行数据读取时,该第二节点的电压受控于该第一节点的电压。一实施例中(例如图4),该脉宽控制器还包含一第三反相器(例如iv3,图4),耦接于该第三输出端与该第三节点之间。

6、一实施例中(例如图6),该第一逻辑门与该延迟电路分别由一第一供应电压(例如vdd1,图6)与一第二供应电压供电(例如vdd2,图6),且该第一供应电压与该第二供应电压相异。一实施例中(例如图6),各该感测放大器至少有一部分(例如s2[k],图6)由该第二供应电压供电。

7、一实施例中(例如图4),该脉宽控制器还包含一第二逻辑门(例如g2,图4)。该第二逻辑门包含一第三输入端(例如i3)、一第四输入端(例如i4)与一第二输出端(例如o2),分别耦接该第一节点,一第四节点(例如n4)与该第二节点。

8、一实施例中(例如图4),该脉宽控制器还包含一第四逻辑门(例如g4,图4)。该第四逻辑门包含一第七输入端(例如i7)、一第八输入端(例如i8)与一第四输出端(例如o4),分别耦接一第一指示信号(例如scanen)、一第二指示信号(例如wei)与该第四节点。一实施例中(例如图4),该第二逻辑门、该第三逻辑门与该第四逻辑门均是或非门。

9、一实施例中(例如图4),该存储模块还包含一有限状态机电路(例如400,图4),耦接于该脉宽控制器与该前节点之间。当该脉宽控制器使该前节点的电压改变时,使该有限状态机电路改变该前节点的电压。

10、一实施例中(例如图4),该有限状态机电路包含一第五节点(例如n5,图4)与一第六节点(例如n6,图4);其中,该第五节点耦接该第一节点,且该六节点耦接该前节点。

11、一实施例中(例如图4),该有限状态机电路还包含一第七节点(例如n7),耦接于一时钟(例如clk)。一实施例中(例如图4),该存储模块还包含一第二反相器(例如iv2,图4),耦接于该第六节点与该前节点之间。

12、本发明的目的之一是提供一种可改良感测放大时序适应性的存储模块(例如100,图1),其可包含至少一位元线(例如bl[q])、至少一字元线(例如wl[p])、一追随位元线(例如tbl)、一追随字元线(例如twl)、至少一存储单元(例如c[p,q])、至少一追随单元(例如tc[p])、至少一感测放大器(例如sa[k])与一第一逻辑门(例如g1,图4)。该追随字元线由一前节点(例如w1)延伸至一后节点(例如w3),且于该前节点至该后节点的长度正相关于各该字元线的长度。各该存储单元耦接该至少一位元线的其中之一以及该至少一字元线的其中之一。各该追随单元耦接该追随位元线。各该感测放大器耦接该至少一位元线的其中之一,并更耦接于一第三节点(例如n3)。各该感测放大器在该第三节点的电压为一第一电平(例如v1,图6)时失能,并在该第三节点的电压为一第二电平(例如v2,图6)时受控使能。该第一逻辑门包含一第一输入端(例如i1,图4)、一第二输入端(例如i2,图4)与一第一输出端(例如o1,图4),分别耦接该追随位元线、该后节点与该前节点。当该存储模块进行数据读取时,该第三节点的电压受控于该第一输出端的电压。

13、一实施例中(图4),该存储模块还包含一第三逻辑门(例如g3,图4)与一延迟电路(例如500,图4)。该第三逻辑门包含一第五输入端(例如i5)、一第六输入端(例如i6)与一第三输出端(例如o3);该第五输入端耦接一第二节点(例如n2),该延迟电路耦接于该第二节点与该第六输入端之间,该第三输出端耦接该第三节点,且该第二节点耦接该第一输出端。一实施例中(例如图6),该第一逻辑门与该延迟电路分别由两相异供应电压(例如vdd1与vdd2,图6)供电。

14、为了对本发明的上述及其他方面有更佳的了解,下文特举实施例,并配合说明书附图详细说明如下:

本文地址:https://www.jishuxx.com/zhuanli/20240731/181831.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 YYfuon@163.com 举报,一经查实,本站将立刻删除。

下一篇

返回列表