一种基于FPGA的存储器阵列测试系统

- 国知局

- 2024-07-31 19:27:06

本发明属于半导体集成电路器件测试,更具体地,涉及一种基于fpga的存储器阵列测试系统。

背景技术:

1、随着计算机应用的不断扩大和发展,人们对存储器的要求也越来越高,而传统的闪存、动态随机存储器(dram)和静态随机存储器(sram)等存储器存在着各种不足和限制。不同的新一代存储器具有各自的优势与特点,其测试需求量庞大。目前,新型非易失性存储领域较为成熟的技术路线主要有相变存储器(pcm)、磁变存储器(mram)以及阻变存储器(rram)3种。pcm通过相变材料相态的变化获得不同的电阻值,主要用于独立式存储;mram通过磁性材料中磁畴的方向变化改变电阻,主要用于嵌入式存储;rram则利用阻变材料中导电通道的产生或关闭实现电阻变化。

2、在存储器中,1t1r(one transistor one resistor)是一种存储单元的配置。它由一个晶体管和一个电阻器组成。1t1r结构通常用于二维平面结构非易失性存储器技术,如阻变存储器或相变存储器等。这种配置的存储单元由一个晶体管作为选择器和一个电阻器作为存储元件组成。晶体管为三端器件,用于控制存储单元的读取和写入操作。它可以选择要访问的特定存储单元,并通过控制电流或电压来实现读取或写入操作。电阻器则用于存储信息。通过在电阻器中施加电压或电流,可以改变其电阻状态,从而表示存储的数据值。1t1r结构相对简单且具有较小的面积,因此在一些新型存储器技术中得到广泛应用。它具有较低的功耗、较高的密度和较快的读写速度,使得其在新一代存储器技术中具有潜在的优势和应用前景。

3、1s1r(one selector one resistance)阵列是一种存储体系结构,其中每个存储单元由一个存储器件和一个选择器件组成,常用于三维存储器架构。存储器件可以使用磁存储器、阻变存储器、相变存储器、铁电存储器等,选通器件为两端器件,可以使用双向阈值选通管(ots)。为防止pcm阵列泄漏电流,ots被引入到pcm中。ots是一种基于奥弗辛斯基阈值导通理论的两端器件,当其两端电压达到阈值电压(uth)时,ots进入导通状态,阻值迅速降低;当导通状态的ots电压高于保持电压(uhold),ots会保持低阻导通状态。

4、关于阵列形态,现多采取纵横式交叉(crossbar)的形式,即通过字线与位线选择阵列当中的存储单元。该形态需注意选中单元产生的泄露电流对周围单元的串扰。

5、对于在实验室中还未封装以及没有外围电路的存储器阵列,研究人员一般使用探针台进行测试,探针台通常有4根探针,用于放置在电极上,与测试设备进行电属性连接。然而,4根探针对于具有多根字线与位线的存储器来说数量过少,且一次测试只能测试少量的存储单元,此种测试方法效率过慢,需反复抬放探针。

6、如今各类新型存储器技术发展逐渐迅猛,产业化的趋势也逐渐明显,无论是工厂生产还是实验室研发,都需要对存储器阵列进行一定特性的测试,再加上目前市面上的集成测试系统也存在着价格高昂、效率不高、国外进口、开发周期长等问题,因此研发一款国产、低成本、高性能的基于fpga的存储器阵列测试系统,对新型存储器产业化、实验室科研与早期产品质量检测具有重要促进作用。

技术实现思路

1、针对现有技术的缺陷,本发明的目的在于提供一种基于fpga的存储器阵列测试系统,从而在没有外围电路的晶圆上,正确选择阵列中的存储器单元,并能对其进行读擦写操作。

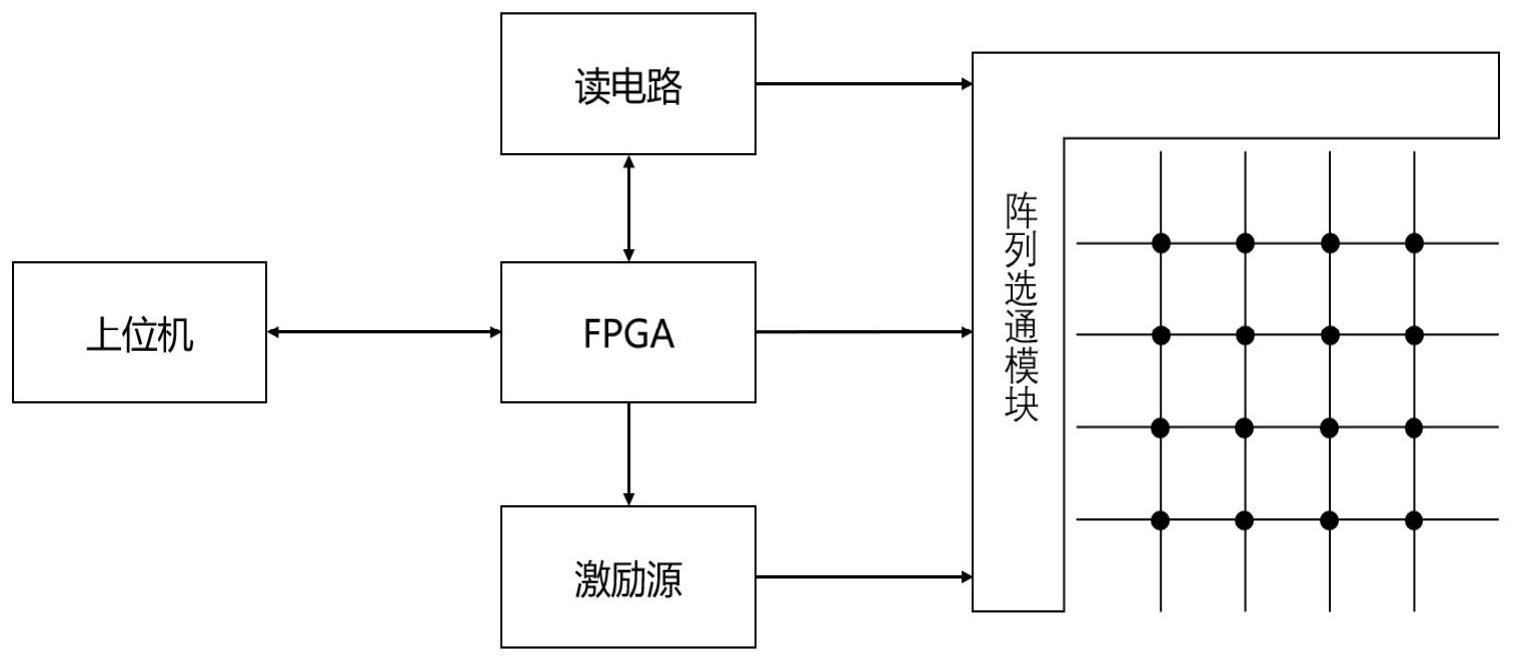

2、本发明提供了一种基于fpga的存储器阵列测试系统,用于对还未封装且未添加外围电路的存储器进行测试,包括:

3、fpga,其第一输入端连接至上位机的输出端,第二输入端连接至读电路的输出端,第一输出端连接至激励源的输入端,第二输出端连接至读电路的第一输入端,第三输出端连接至阵列选通模块的第一输入端,作为本测试系统的核心控制单元,用于输出对其他模块中模数转换器adc、数模转换器dac、模拟开关与多路复用选择器的数字控制信号,接收并分析来自模数转换器adc的数据,且能与上位机进行数据通讯;

4、激励源,其输出端连接至阵列选通模块的第二输入端,用于根据上位机设置的参数输出对存储器单元的操作电压与偏置电压;

5、读电路,其第二输入端连接至阵列选通模块的输出端,用于根据阵列选通模块所选择的路径读取选中存储单元的电阻值;

6、阵列选通模块,用于根据控制信号将读写擦操作电压分配到所选择的字线中,将所选择的位线连接读电路,并将偏置电压分配到所有未选择的字线与位线中;

7、上位机,用于根据用户操作输出对脉冲电压的脉宽与幅值,扫描电压的步进时间、步进电压与扫描点数,所选中存储单元的字线与位线的控制信号,并将接收来自fpga的电阻数据以图表形式呈现。

8、更进一步地,激励源产生的脉冲电压能够达到ns级,分辨率为5ns,脉冲上升沿下降沿时间约15ns,幅值与脉宽都可调整。

9、更进一步地,激励源包括:数模转换器dac和单刀双掷模拟开关;数模转换器dac的输入端作为激励源的输入端,用于接收fpga输出设定的电压幅值信息;单刀双掷模拟开关的一端s2连接至数模转换器dac的输出端,另一端s1接地,用于根据fpga产生的电压脉冲波形输出激励信号。

10、更进一步地,阵列选通模块包括:行选通电路和列选通电路;行选通电路用于与阵列中的字线连接,并将读擦写电压分配到上位机所选择的字线中,偏置电压分配到所有未选择的字线中;列选通电路用于与阵列中的位线连接,并将读电路端口或地连接到上位机所选择的位线中,偏置电压分配到所有未选择的位线中。

11、更进一步地,行选通电路和列选通电路均包括多路复用选择器和模拟开关;多路复用选择器用于根据对字线与位线的控制信号,将读写擦操作电压分配到所选择的字线中,并将所选择的位线连接到读电路输入端或接地;模拟开关用于根据所述对字线与位线的控制信号,将偏置电压分配到所有未选择的字线与位线中。

12、更进一步地,多路复用选择器的通道数量与所述阵列中的字线和位线数量相匹配,所述模拟开关的接口数量与所述阵列中的字线和位线数量相匹配。

13、更进一步地,读电路包括:依次连接的采样电阻、运算放大器、低通滤波器和adc;工作时,采集采样电阻上电压,并经运算放大器放大该电压值,后续经低通滤波器滤除噪声,最后将此电压连接到adc的输入口,读取得到的数字信号传回给fpga进行处理。

14、其中,采样电阻的阻值可以设置为100ω。

15、更进一步地,存储器通过引线键合与pcb印刷电路板进行电气属性连接,所述存储阵列选通测试系统搭建在所述pcb印刷电路板上。

16、更进一步地,上位机使用rs232串口与fpga进行数据通讯。

17、通过本发明所构思的以上技术方案,与现有技术相比,由于现有探针台的测试方案价格昂贵、效率低。而fpga具有布线资源丰富,可重复编程和集成度高,本发明基于fpga进行测试系统的搭建,对未封装的晶圆不需反复抬放探针,直接使用引线键合技术使多个电极与外部pcb连接,且能对不同的阵列形态选择是否对未选择的字线与位线增加偏置电压,因此本发明能够取得低成本,高效率,且能对1t1r、1s1r不同阵列形态的存储阵列进行测试的有益效果。本发明适用于各类未添加外围集成电路的存储器阵列的测试,包括但不限于相变存储器、磁随机存储器、忆阻器、铁电存储器等。

本文地址:https://www.jishuxx.com/zhuanli/20240731/182553.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 YYfuon@163.com 举报,一经查实,本站将立刻删除。