一种抗双节点翻转加固的SRAM存储单元的制作方法

- 国知局

- 2024-07-31 19:29:16

本发明属于集成电路抗辐照,涉及航天设备用sarm,具体涉及一种抗双节点翻转加固的sram存储单元。

背景技术:

1、随着集成电路的不断发展,静态随机存储器(sram)在高性能集成电路中发挥着越来越关键的作用。当应用于人造卫星、宇宙飞船、运载火箭等航天设备时,sram往往容易受到高能粒子的影响产生单粒子翻转效应,使存储单元敏感存储节点上的数据产生错误,进而导致系统失效。

2、由于cmos工艺尺寸的不断减小,半导体器件的集成度不断提高,工作电压越来越低,这导致存储节点的临界电荷也越来越小,单粒子翻转效应越来越容易发生。同时,一次单粒子入射所产生的电子和空穴对可以覆盖同一存储单元中的多个存储节点,使得同一存储单元内部多个存储节点同时收集电荷并产生翻转。

3、近年来我国航天事业高速发展,空间任务对高性能、高可靠集成电路的需求不断增加,存储单元作为电子控制系统中各基本指令的存储器件,其抗辐射性能严重影响着电子器件的空间应用。上述单粒子入射产生的多节点翻转将导致原来已加固的能够抵抗单粒子单节点翻转的存储单元丧失抗单粒子翻转的能力,因此,进一步加固存储单元以满足抗单粒子多节点翻转的加固需求十分迫切。

技术实现思路

1、为解决上述相关现有技术不足,本发明提供一种抗双节点翻转加固的sram存储单元,实现对内部6个节点单节点单粒子翻转全部免疫和15对双节点敏感对中14对节点对单粒子翻转免疫,显著提高sram存储单元抗单粒子翻转能力。

2、为了实现本发明的目的,拟采用以下方案:

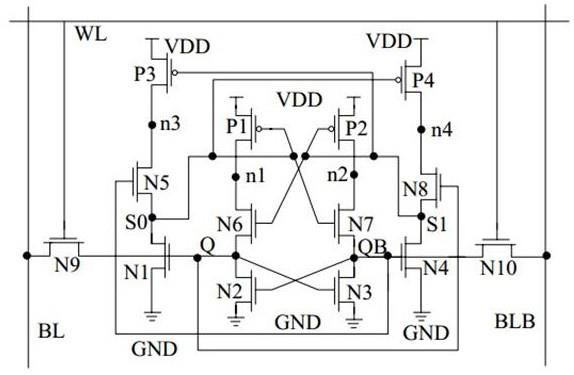

3、一种抗双节点翻转加固的sram存储单元,其电路包括4个pmos晶体管和10个nmos晶体管,具体电路连接关系如下:

4、pmos晶体管p1,其源极与vdd相连,栅极与存储节点s0相连,漏极与存储节点n1相连;

5、pmos晶体管p2,其源极与vdd相连,栅极与存储节点s1相连,漏极与存储节点n2相连;

6、pmos晶体管p3,其源极与vdd相连,栅极与存储节点s1相连,漏极与存储节点n3相连;

7、pmos晶体管p4,其源极与vdd相连,栅极与存储节点s0相连,漏极与存储节点n4相连;

8、nmos晶体管n1,其源极与gnd相连,栅极与存储节点q相连,漏极与存储节点s0相连;

9、nmos晶体管n2,其源极与gnd相连,栅极与存储节点qb相连,漏极与存储节点q相连;

10、nmos晶体管n3,其源极与gnd相连,栅极与存储节点q相连,漏极与存储节点qb相连;

11、nmos晶体管n4,其源极与gnd相连,栅极与存储节点qb相连,漏极与存储节点s1相连

12、nmos晶体管n5,其源极与s0相连,栅极与存储节点qb相连,漏极与存储节点n3相连;

13、nmos晶体管n6,其源极与q相连,栅极与存储节点s1相连,漏极与存储节点n1相连;

14、nmos晶体管n7,其源极与qb相连,栅极与存储节点s0相连,漏极与存储节点n2相连;

15、nmos晶体管n8,其源极与s1相连,栅极与存储节点q相连,漏极与存储节点n4相连;

16、nmos晶体管n9,其源极与位线bl相连,栅极与字线wl相连,漏极与存储节点q相连;

17、nmos晶体管n10,其源极与位线blb相连,栅极与字线wl相连,漏极与存储节点qb相连。

18、本发明的有益效果:

19、相比于现有技术的其他加固结构,本发明实现了对内部6个节点单节点单粒子翻转全部免疫和15对双节点敏感对中14对节点对单粒子翻转免疫,显著提高了sram存储单元的抗单粒子翻转能力。

技术特征:1.一种抗双节点翻转加固的sram存储单元,其特征在于,其电路包括:

2.根据权利要求1所述的抗双节点翻转加固的sram存储单元,其特征在于,nmos晶体管n9和nmos晶体管n10为读写管;

3.根据权利要求1所述的抗双节点翻转加固的sram存储单元,其特征在于,读写过程为:

4.根据权利要求1所述的抗双节点翻转加固的sram存储单元,其特征在于,抗单节点翻转包括:当nmos晶体管n2的漏极遭受重离子轰击时,存储节点q的电平由高变低,q=0,存储节点s0、qb和s1变为高阻态;此时,由于pmos晶体管p1、nmos晶体管n6仍保持导通状态,存储节点q的电平将会在重离子入射干扰结束后恢复到高电平。

5.根据权利要求1所述的抗双节点翻转加固的sram存储单元,其特征在于,抗单节点翻转包括:当nmos晶体管n4的漏极遭受重离子轰击时,存储节点s1的电平由高变低,s1=0,存储节点q变为高阻态;此时,由于pmos晶体管p4、nmos晶体管n8仍保持导通状态,存储节点s1的电平将会在重离子入射干扰结束后恢复到高电平。

6.根据权利要求1所述的抗双节点翻转加固的sram存储单元,其特征在于,抗双节点翻转包括:当nmos晶体管n2和nmos晶体管n6的漏极遭受重离子轰击时,存储节点q和存储节点n1的电平由高变低,n1=0不会对其他晶体管的状态有影响;q=0,存储节点s0和存储节点s1维持原电平状态不变,存储节点q和存储节点n1的电平将会通过pmos晶体管p1和nmos晶体管n6恢复。

7.根据权利要求1所述的抗双节点翻转加固的sram存储单元,其特征在于,抗双节点翻转包括:当nmos晶体管n4和nmos晶体管n7的漏极遭受重离子轰击时,存储节点s1和存储节点n2的电平由高变低,n2=0不会对其他晶体管的状态有影响;s1=0,存储节点s0和存储节点q维持原电平状态不变,存储节点s1和存储节点n2的电平将会通过pmos晶体管p4、nmos晶体管n8和pmos晶体管p2恢复。

技术总结一种抗双节点翻转加固的SRAM存储单元,包括4个PMOS晶体管和10个NMOS晶体管,PMOS晶体管P1、P2、P3和P4与VDD相连,NMOS晶体管N1、N2、N3和N4与GND相连,NMOS晶体N9、N10为读写管;插入4个NMOS晶体管N5、N6、N7和N8后,存储单元中的存储节点Q、QB、S0和S1全部由NMOS晶体管包围;Q通过N9连接到BL,QB通过N10连接到BLB,N9和N10由WL控制。通过引入冗余存储节点和减少存储单元中敏感节点种类的方式,提高SRAM存储单元的抗单粒子翻转能力,实现对内部6个节点单节点单粒子翻转全部免疫和15对双节点敏感对中14对节点对单粒子翻转免疫。技术研发人员:刘鸿瑾,祁首冰,李天文,周泽鹏,张绍林,杜易展,高鹤,贺冬云,赵钰恺,杨林,张智京受保护的技术使用者:北京轩宇空间科技有限公司技术研发日:技术公布日:2024/1/15本文地址:https://www.jishuxx.com/zhuanli/20240731/182722.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 YYfuon@163.com 举报,一经查实,本站将立刻删除。

下一篇

返回列表