掉电检测电路的制作方法

- 国知局

- 2024-07-31 19:29:29

本发明涉及一种半导体集成电路,特别是涉及一种掉电检测(lvd)电路。

背景技术:

1、如图1所示,是现有擦写控制电路的示意图;在闪存(flash)中包括擦写控制电路301,擦除控制电路301的电源端连接电源电压vdd,会输出信号prog和信号erase,信号prog是编程命令信号以及erase是擦除命令信号。当掉电时,电源电压vdd会降低,电源电压vdd过低会误触发信号prog/erase命令。为了防止这种情形发生,一般会加掉lvd即电检测电路进行检测,当电源电压vdd低于一定值时,产生一个信号,把类似于信号prog/erase等关键信号复位。

2、如图2所示,是现有第一种掉电检测电路的电路图;现有第一种掉电检测电路包括:

3、由电阻r101和r102组成的分压电路,形成电源电压vdd的分压并输入到比较器101的一个输入端如正输入端,比较器101的另一个输入端即负输入端接参考电压vref,通过电源电压vdd的分压和vref的比较确定比较器101的输出端输出的掉电检测信号lvd_out101的状态,当电源电压vdd降低到一定值时,掉电检测信号lvd_out101会由高电平转换到低电平,这就检测到掉电的发生。图2中还包括nmos管mn101,nmos管mn101和分压电路串联且栅极连接使能信号en,用于对整个第一种掉电检测电路进行使能。

4、如图3所示,是现有第二种掉电检测电路的电路图;现有第二种掉电检测电路包括:

5、由电阻r201和r202组成的分压电路,形成电源电压vdd的分压并输入到nmos管mn202的栅极;nmos管mn202的源极接地,nmos管mn202的漏极通过电阻r203上拉到电源电压vdd且nmos管mn202的漏极连接到反相器201的输入端,反相器201的输出端输出掉电检测信号lvd_out201。图3中还包括nmos管mn201,nmos管mn201和分压电路串联且栅极连接使能信号en,用于对整个第二种掉电检测电路进行使能。图3中,当电源电压vdd的分压大于等于nmos管mn202的阈值电压时,nmos管mn202导通;当电源电压vdd的分压小于nmos管mn202的阈值电压时,nmos管mn202截止。两种状态下掉电检测信号lvd_out201会产生翻转,从而实现对掉电检测。

6、现有第一种和第二种掉电检测电路都具有相应的缺点,从而会影响lvd的精度。其中,图2所示的现有第一种掉电检测电路的检测精度比较依赖于参考电压vref,而参考电压vref通常是由带隙基准(bandgap)源提供,在电源电压vdd较小的情况下,带隙基准源不一定能正常工作,从而使得影响参考电压vref的大小并影响lvd的精度。而图3所示的现有第一种掉电检测电路的检测精度则比较依赖于nmos管mn202的阈值电压,nmos管mn202的阈值电压则会受到工艺影响,这会使得lvd精度受限。

技术实现思路

1、本发明是提供一种掉电检测电路,能对掉电检测精度进行准确调节并提高掉电检测精度。

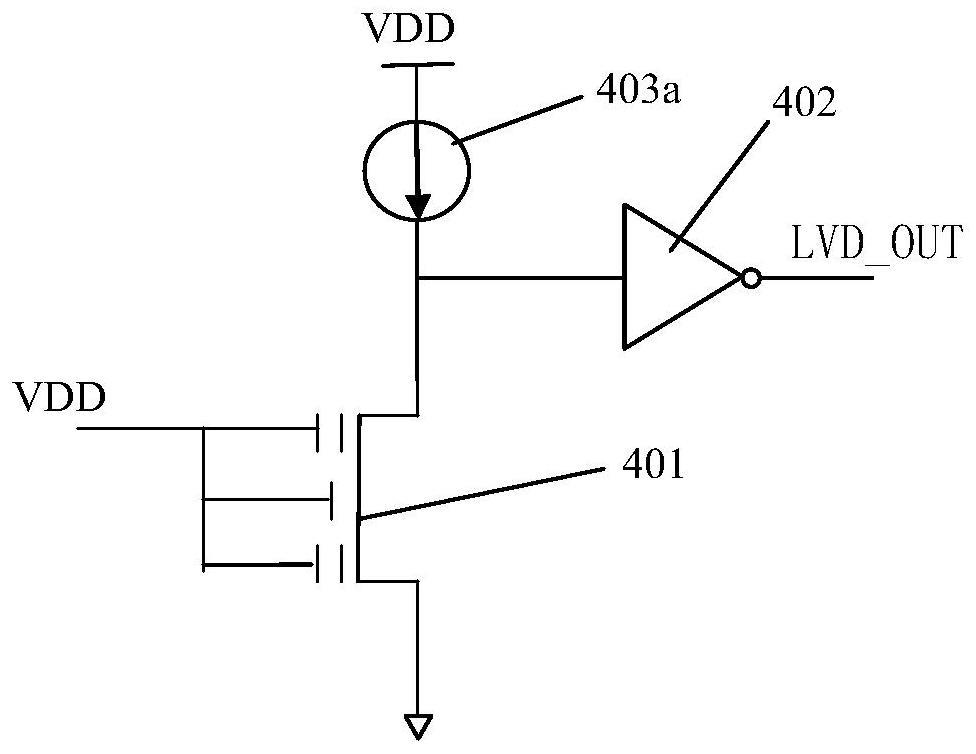

2、本发明提供的掉电检测电路包括:第一晶体管,上拉路径和反相器。

3、所述第一晶体管采用非挥发性存储器件。

4、所述第一晶体管的漏极连接所述反相器的输入端。

5、所述第一晶体管的源极接地。

6、所述上拉路径连接在所述第一晶体管的漏极和电源电压之间。

7、所述反相器的输出端输出掉电检测信号。

8、所述第一晶体管的栅极结构中具有浮栅和控制栅,所述第一晶体管的浮栅经过编程并使所述第一晶体管的栅极结构具有第一阈值电压。

9、所述第一晶体管的栅极结构连接所述电源电压,当所述电源电压低于所述第一阈值电压时,所述掉电检测信号产生跳变并实现掉电检测。

10、进一步的改进是,所述上拉路径采用第一电流源。

11、进一步的改进是,所述上拉路径采用第一电阻。

12、进一步的改进是,掉电检测电路用于对闪存的所述电源电压进行掉电检测。

13、进一步的改进是,所述闪存的存储单元采用非挥发性存储器件,所述第一晶体管的结构和所述存储单元的结构相同。

14、进一步的改进是,所述非挥发性存储器件采用分离栅浮栅器件。

15、所述分离栅浮栅器件包括:对称设置的第一源漏区和第二源漏区,位于所述第一源漏区和所述第二源漏区之间的多个分离的具有浮栅的第一栅极结构,位于所述第一栅极结构之间的第二栅极结构;所述第一栅极结构中具有位于所述浮栅顶部的控制栅;每一个所述浮栅作为一个存储位。

16、进一步的改进是,所述分离栅浮栅器件为双分离栅浮栅器件,所述第一栅极结构的数量为两个。

17、进一步的改进是,所述分离栅浮栅器件为n型器件,所述第一源漏区和所述第二源漏区都由n+区组成。

18、p型掺杂的沟道区位于所述第一源漏区和所述第二源漏区之间且被各所述第一栅极结构和所述第二栅极结构所覆盖,各所述第一栅极结构和所述第二栅极结构分别控制所覆盖的所述沟道区的区域段。

19、进一步的改进是,各所述第一栅极结构由隧穿介质层、所述浮栅、控制栅介质层和所述控制栅叠加而成。

20、所述第二栅极结构由字线栅介质层和字线栅叠加而成。

21、进一步的改进是,所述浮栅为多晶硅浮栅;所述控制栅采用多晶硅栅,所述字线栅采用多晶硅栅。

22、所述隧穿介质层的材料为氧化层,所述控制栅介质层的材料为氧化层,所述字线栅介质层的材料为氧化层。

23、进一步的改进是,所述第一晶体管的各所述存储位对应的阈值电压都小于等于所述第一阈值电压且至少一个所述存储位编程到具有所述第一阈值电压。

24、进一步的改进是,所述第一晶体管的栅极结构中的各所述第一栅极结构的所述控制栅以及各所述第二栅极结构都连接到所述电源电压。

25、进一步的改进是,阈值电压小于所述第一阈值电压的各所述存储位保持为擦除状态。

26、进一步的改进是,在晶圆测试中实现对所述第一晶体管的各所述存储位的阈值电压的调节。

27、进一步的改进是,所述第一电流源的电流大小为数na至数十na。

28、现有技术中通过电源电压的分压和参考电压或mos晶体管的阈值电压进行比较来实现掉电检测不同,其中参考电压需要采用带隙(bandgap)基准源提供,带隙基准源在电源电压较低时不一定工作正常,从而使得参考电压不一定准确;而mos晶体管的阈值电压受工艺影响也不是很精确,这都使得掉电检测精度受到影响;而本发明则是采用非挥发性存储器件组成的第一晶体管来实现电源电压的掉电检测,利用非挥发性存储器件的阈值电压能通过编程来精确调节的特征,使第一晶体管的第一阈值电压能根据需要实现精确设置,这样当电源电压大于等于第一阈值电压时第一晶体管导通,而当电源电压小于第一阈值电压时第一晶体管就会截止,由此就能实现对电源电压掉电的准确检测且掉电检测精度可调,掉电检测信号通过上拉路径和反相器实现输出,所以本发明能对掉电检测精度进行准确调节并提高掉电检测精度。

本文地址:https://www.jishuxx.com/zhuanli/20240731/182749.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 YYfuon@163.com 举报,一经查实,本站将立刻删除。

上一篇

一种计算机硬盘磁头结构

下一篇

返回列表