高速缓存线数据保护的制作方法

- 国知局

- 2024-07-31 19:30:26

本公开大体上涉及半导体存储器及方法,且更特定来说,涉及用于高速缓存线数据保护的设备、系统及方法。

背景技术:

1、存储器装置通常作为计算机或其它电子系统中的内部半导体集成电路系统提供。存在许多不同类型的存储器,其包含易失性及非易失性存储器。易失性存储器可需要电力来维持其数据(例如,主机数据、错误数据等)且包含随机存取存储器(ram)、动态随机存取存储器(dram)、静态随机存取存储器(sram)、同步动态随机存取存储器(sdram)及晶闸管随机存取存储器(tram)等。非易失性存储器可通过在未通电时留存所存储数据来提供持久数据并且可包含nand快闪存储器、nor快闪存储器、铁电随机存取存储器(feram)及电阻可变存储器(例如相变随机存取存储器(pcram))、电阻式随机存取存储器(rram)及磁阻式随机存取存储器(mram),例如自旋力矩转移随机存取存储器(stt ram)等。

2、存储器装置可耦合到主机(例如,主机计算装置),以存储数据、命令及/或指令供主机在计算机或电子系统操作时使用。举例来说,在计算或其它电子系统的操作期间,可在主机与存储器装置之间传送数据、命令及/或指令。控制器可用于管理主机与存储器装置之间的数据、命令及/或指令的传送。

技术实现思路

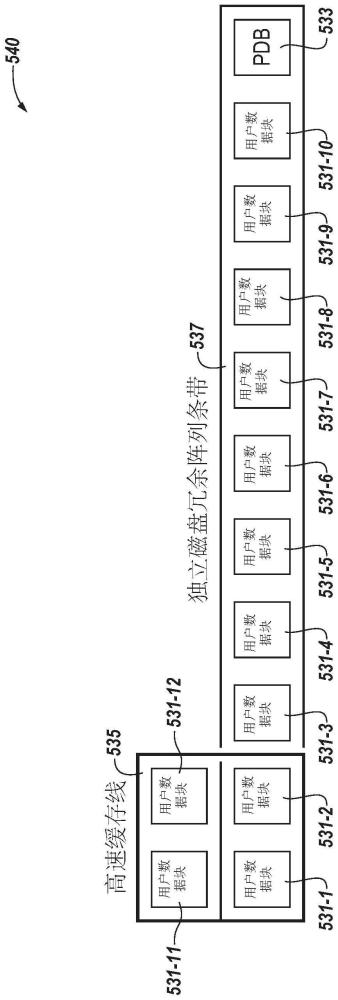

1、一方面,本公开涉及一种用于高速缓存线数据保护的设备,其包括:数个存储器装置;及存储器控制器,其耦合到所述数个存储器装置,所述存储器控制器经配置以:接收对应于高速缓存线的多个用户数据块(udb),其中所述多个udb属于相应不同条带;共同基于对应于所述高速缓存线的所述多个udb而产生错误检测信息;共同基于对应于所述高速缓存线的所述多个udb而产生错误校正信息;及将所述多个udb连同所述错误检测信息及错误校正信息一起写入到所述数个存储器装置。

2、另一方面,本公开涉及一种用于高速缓存线数据保护的设备,其包括:数个存储器装置;及存储器控制器,其耦合到所述数个存储器装置,所述存储器控制器经配置以:从所述数个存储器装置接收对应于高速缓存线的多个用户数据块(udb),其中所述多个udb属于相应不同条带;使用共同基于所述多个udb产生的错误校正信息,对所述多个udb共同执行第一错误校正操作,以校正所述多个udb内的一定数量的位错误;及使用共同基于所述多个udb产生的错误检测信息,对所述多个udb共同执行第一错误检测操作,以确定是否对所述多个udb执行一或多个第二错误校正操作。

3、另一方面,本公开涉及一种高速缓存线数据保护的方法,其包括:从数个存储器装置传送对应于高速缓存线的多个用户数据块(udb),其中所述多个udb属于相应不同条带;使用共同基于所述多个udb产生的第一错误校正信息,对所述多个udb执行第一错误校正操作,以校正一定数量的错误或检测比所述一定数量的错误更多的错误;在所述第一错误校正操作之后且使用共同基于所述多个udb产生的第一错误检测信息,对所述多个udb执行第一错误检测操作以确定所述多个udb是否仍然含有一或多个位错误;及响应于所述第一错误检测操作指示所述多个udb仍然含有所述一或多个错误,通过进一步传送以下各者而对所述多个udb执行一或多个第二错误校正操作:对应于每一条带的一组相应其它udb;及对应于每一条带的相应奇偶校验数据块。

技术特征:1.一种用于高速缓存线数据保护的设备,其包括:

2.根据权利要求1所述的设备,其中所述存储器控制器进一步经配置以:

3.根据权利要求1所述的设备,其中:

4.根据权利要求1到3中任一权利要求所述的设备,其中每一条带是独立磁盘冗余阵列raid存取的单元。

5.根据权利要求1到3中任一权利要求所述的设备,其中所述多个udb被接收为不同写入命令的部分。

6.根据权利要求1到3中任一权利要求所述的设备,其中对应于高速缓存线的所述多个udb包含来自所述条带中的每一者的至少两个udb。

7.根据权利要求1到3中任一权利要求所述的设备,其中所述错误检测信息对应于循环冗余校验crc数据。

8.一种用于高速缓存线数据保护的设备,其包括:

9.根据权利要求8所述的设备,其中所述存储器控制器经配置以在所述一或多个第二错误校正操作中的相应者之后执行一或多个第二错误检测操作。

10.根据权利要求8所述的设备,其中所述存储器控制器经配置以:

11.根据权利要求8到10中任一权利要求所述的设备,其中所述存储器控制器经配置以致使所述数个存储器装置:

12.根据权利要求8到10中任一权利要求所述的设备,其中所述存储器控制器经配置以响应于所述第一错误检测操作指示所述多个udb中的某一量的位错误来执行所述一或多个第二错误校正操作,以恢复所述多个udb中的一或多个udb。

13.根据权利要求12所述的设备,其中对应于高速缓存线的所述多个udb包含来自所述条带中的每一者的至少两个udb。

14.根据权利要求13所述的设备,其中所述控制器经配置以对所述多个udb中的每一udb个别地执行所述一或多个第二错误校正操作中的相应者。

15.根据权利要求13所述的设备,其中所述控制器经配置以对所述多个udb的每一子集共同地执行数个第二错误校正操作(652-1、…、652-8)中的相应者,其中每一子集包含来自每一条带的一个udb。

16.一种高速缓存线数据保护的方法,其包括:

17.根据权利要求16所述的方法,其中执行所述一或多个第二错误校正操作进一步包括对所述多个udb中的每一者及所述多个udb的每一子集执行所述一或多个第二错误校正操作中的相应者,其中所述多个udb的每一子集包含来自所述不同条带中的每一条带的一个udb。

18.根据权利要求16所述的方法,其进一步包括:

技术总结本公开涉及高速缓存线数据保护。能在高速缓存线基础上提供具有错误校正/检测能力的数据保护。当在高速缓存线基础上提供以共同保护高速缓存线数据时,与在所述高速缓存线数据的子集上个别地提供相同错误校正/检测能力相比,能用较少数目的位(例如,错误校正码ECC及/或循环冗余校验CRC位)来提供错误校正/检测能力。技术研发人员:M·斯福尔津,P·阿马托受保护的技术使用者:美光科技公司技术研发日:技术公布日:2024/1/5本文地址:https://www.jishuxx.com/zhuanli/20240731/182818.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 YYfuon@163.com 举报,一经查实,本站将立刻删除。

下一篇

返回列表