一种高速半导体激光器芯片及其制备方法与流程

- 国知局

- 2024-07-31 19:02:22

本发明涉及半导体激光器,具体涉及一种高速半导体激光器芯片及其制备方法。

背景技术:

1、随着5g时代的到来,各国都在大力发展5g以及推进数据中心的建设。高速率光模块是5g通信和数据中心建设的主要部件,其中的核心元件是25gb/s及以上速率的dfb半导体激光器芯片。在解决芯片带宽和传输速率瓶颈技术上,除了进行量子阱的匹配优化设计以外,当前国内外主流厂商普遍采用缩短谐振腔腔长技术,比如25gb/s dfb芯片将腔长缩短至160μm以下,50gb/s dfb芯片将腔长缩短至140μm以下,以降低谐振腔光子寿命以及降低芯片寄生电容,从而实现高带宽。

2、然而,缩短腔长技术会带来一系列的问题。第一,短腔长芯片的散热问题,光芯片在极限工作条件下结温会达到130℃以上,没有良好的散热会极大的影响芯片可靠性;第二,短腔长芯片的bar条解离问题,芯片腔长小于200μm时极易出现划裂偏差、歪斜、崩角、高应力量子阱层薄膜剥落等失效情况,大大降低了产品的良率;第三,短腔长芯片的端面失效问题,原因主要来自于量子阱层的大应力和端面高光功率密度。目前业界主流的方法,是通过butt-joint对接生长技术,生长ingaasp无源波导区域来延长芯片长度,该对接工艺非常复杂,需要四次外延生长以及解决butt-joint对接界面氧化带来的缺陷问题,butt-joint工艺对于高速率芯片的稳定量产同样具有极大的挑战。因此,设计出一种结构更简单、制备更容易、能够实现稳定量产的25gb/s以上速率dfb半导体激光器芯片是很有必要的。

技术实现思路

1、本发明第一方面的目的在于提供高速半导体激光器芯片的制备方法,只用一次外延同时生长出有源区和无源区结构,具有结构简单、生长制备容易、能够实现稳定量产的优点。

2、本发明解决的第一问题是简化激光器芯片制备流程,减少外延生长的次数,为此提供了以下技术方案:

3、一种高速半导体激光器芯片的制备方法,包括以下步骤:

4、步骤1,在衬底上划分ar无源区、有源区、hr无源区,在有源区区域生长氧化硅掩膜层,但ar无源区区域和hr无源区区域不生长氧化硅掩膜层;

5、步骤2,通过蚀刻制程在氧化硅掩膜层形成区域性掩膜条图形,掩膜条图形的长度与有源区长度保持一致;

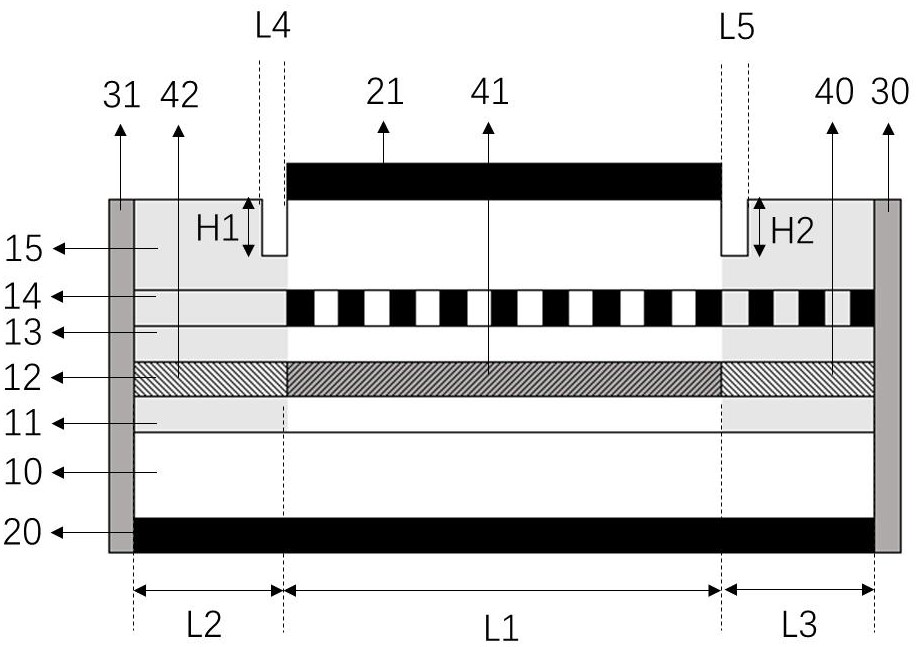

6、步骤3,通过金属有机化学气相沉积在ar无源区、有源区、hr无源区同时形成一次外延结构,包括下波导层、有源层、上波导层、光栅薄膜层。

7、上述方案中,通过在衬底上划分ar无源区、有源区、hr无源区,可以实现最终的芯片结构为三段式结构,相比常规单段式有源区结构,可以增加激光器芯片长度,有效提升芯片散热能力和可靠性,同时实现芯片高带宽、高速率传输。通过在有源区生长氧化硅掩膜,由于氧化硅掩膜对mocvd膜层生长速率的影响,使掩膜生长区材料量子阱层和上下波导层厚度相比无掩膜生长区产生一个增量,且增量值可以通过掩膜层厚度和宽度进行调控,从而在一次外延过程中可以实现对无源区和有源区增益峰值波长的调控,无需多次外延生长,简化了制备流程,缩短了制备周期,便于批量生产。

8、进一步优化的方案中,步骤1中通过调整氧化硅掩膜层的厚度与宽度,实现ar无源区和hr无源区的增益峰值波长比有源区的增益峰值波长小至少30nm,ar无源区和hr无源区的量子阱厚度比有源区的量子阱厚度小至少30å。

9、上述方案中,通过调整氧化硅掩膜层的厚度与宽度,实现在无源区可以引入更薄的量子阱,减少量子阱的应力累积效应,改善芯片端面可靠性,同时有源区激光不会在无源区被吸收,继而避免影响激光出射光功率。

10、本发明解决的第二问题是提高hr无源区端面可靠性,为此提供了以下技术方案:

11、在步骤3之后还包括以下步骤:

12、步骤4,同时在有源区和hr无源区通过蚀刻形成光栅结构,但ar无源区保留光栅薄膜层。

13、上述方案中,通过同时在有源区和hr无源区通过蚀刻形成光栅结构,可以实现在hr无源区光栅薄膜层引入与有源区激射波长λ相匹配的均匀光栅结构,与hr高反射膜层共同作用,起到分布反射光的作用,缓解hr端面光功率密度,从而改善芯片端面可靠性。

14、本发明解决的第三问题是如何避免电流干扰,简化工艺流程,为此提供了以下技术方案:

15、在步骤4之后还包括以下步骤:

16、步骤5,去除氧化硅掩膜层,在光栅薄膜层通过金属有机化学气相沉积形成二次外延结构,包括inp包覆层和ingaas接触层;

17、步骤6,在二次外延结构上通过蚀刻制程形成ar无源区与有源区之间的隔离区、有源区与hr无源区之间的隔离区,以及位于有源区的脊波导区;

18、步骤7,在脊波导区形成氧化硅保护膜层,并采用蚀刻工艺在氧化硅保护膜层开窗,通过磁控溅射形成p面金属层;

19、步骤8,在衬底背面进行掩膜抛光后通过磁控溅射形成n面金属层;

20、步骤9,bar条解离,分别在ar无源区的端面和hr无源区的端面形成ar减反射膜层、hr高反射膜层。

21、上述方案中,通过在有源区和无源区之间形成隔离区,可以实现在有源区独立注入电流,而无源区无电流注入,实现电隔离,继而简化芯片制备流程。

22、本发明的第二目的在于提供一种根据任一项所述的高速半导体激光器芯片的制备方法所制备而得的半导体激光器芯片。

23、与现有技术相比,使用本发明提供的一种高速半导体激光器芯片及其制备方法,优点显著:

24、第一,引入ar无源区、有源区和hr无源区三段式结构,相比常规单段式有源区结构,可以增加激光器芯片长度,解决短腔长芯片的bar条解离难点,有效提升芯片散热能力和可靠性,同时实现芯片高带宽、高速率传输。

25、第二,采用选择区域外延技术,一次外延可以对无源区和有源区增益峰值波长进行分别调控,相比butt-joint对接无源波导技术,结构工艺简单,生长制备容易,能够实现稳定量产,有利于降低高速率dfb半导体激光器芯片制造成本,便于批量量产导入。

26、第三,通过对选择区域掩膜层厚度和宽度进行调控,相比有源区,在无源区可以引入更薄的量子阱,减少量子阱的应力累积效应,解决25gb/s及以上速率芯片需要在有源区引入大应力量子阱层的矛盾,改善由于量子阱层应力累积引发的端面失效问题。

27、第四,在hr无源区光栅薄膜层引入与有源区激射波长λ相匹配的均匀光栅结构,起到分布反射光的作用,相比常规在hr端面集中反射光的结构,可以缓解hr端面光功率密度,从而改善芯片端面可靠性。

技术特征:1.一种高速半导体激光器芯片的制备方法,其特征在于,包括以下步骤:

2.根据权利要求1所述的高速半导体激光器芯片的制备方法,其特征在于,步骤1中通过调整氧化硅掩膜层的厚度与宽度,实现ar无源区和hr无源区的增益峰值波长比有源区的增益峰值波长小至少30nm,ar无源区和hr无源区的量子阱厚度比有源区的量子阱厚度小至少30å。

3.根据权利要求1所述的高速半导体激光器芯片的制备方法,其特征在于,有源区的长度为100μm~200μm。

4.根据权利要求1所述的高速半导体激光器芯片的制备方法,其特征在于,ar无源区的长度为0μm~60μm,hr无源区的长度为0μm~60μm。

5.根据权利要求1所述的高速半导体激光器芯片的制备方法,其特征在于,掩膜条图形的宽度为5μm~100μm,间隔为5μm~100μm。

6.根据权利要求1所述的高速半导体激光器芯片的制备方法,其特征在于,氧化硅掩膜层由氮化硅掩膜层代替。

7.根据权利要求1-6任一项所述的高速半导体激光器芯片的制备方法,其特征在于,在步骤3之后还包括以下步骤:

8.根据权利要求7所述的高速半导体激光器芯片的制备方法,其特征在于,在步骤4之后还包括以下步骤:

9.根据权利要求8所述的高速半导体激光器芯片的制备方法,其特征在于,步骤6中隔离区的深度为300~1500nm,宽度大于5um。

10.根据权利要求1-9任一项所述的高速半导体激光器芯片的制备方法所制备而得的半导体激光器芯片。

技术总结本发明涉及半导体技术领域,尤其涉及一种高速半导体激光器芯片及其制备方法,该制备方法包括以下步骤:步骤1,在衬底上划分AR无源区、有源区、HR无源区,在有源区区域生长氧化硅掩膜层,但AR无源区区域和HR无源区区域不生长氧化硅掩膜层;步骤2,通过蚀刻制程在氧化硅掩膜层形成区域性掩膜条图形,掩膜条图形的长度与有源区长度保持一致;步骤3,通过金属有机化学气相沉积在AR无源区、有源区、HR无源区同时形成一次外延结构,包括下波导层、有源层、上波导层、光栅薄膜层。本发明针对25Gb/s及以上速率半导体激光器芯片,制备工艺简单,同时实现芯片高带宽、高速率传输,降低高速半导体激光器芯片制造成本,便于批量量产导入。技术研发人员:章曙东,陈鸿翔,张林建,王陈受保护的技术使用者:江苏索尔思通信科技有限公司技术研发日:技术公布日:2024/7/29本文地址:https://www.jishuxx.com/zhuanli/20240731/181442.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 YYfuon@163.com 举报,一经查实,本站将立刻删除。

下一篇

返回列表