以高速缓存行粒度跟踪存储器修改的制作方法

- 国知局

- 2024-07-31 19:17:51

本公开的实施例大体上涉及存储器子系统,更特定来说,涉及在与主机系统的高速缓存一致性协议协作的同时以高速缓存行层级自动跟踪对存储器的改变的方法。

背景技术:

1、动态随机存取存储器(dram)装置包含分组为存储体群组的多个存储体,例如,分组为四个存储体群组的十六个存储器存储体。每一存储器存储体是包含多个存储器单元的存储器阵列,使得每一存储器单元能够取决于存储器单元类型而存储一或多个信息位。

技术实现思路

1、本公开的一方面提供一种系统,其包括:存储器装置;及处理装置,其可操作地与所述存储器装置耦合,以执行包括以下的操作:接收物理存储器区域的基地址;接收空日志存储器缓冲器的列表;响应于确定所述物理存储器区域中的高速缓存行处于经修改状态,将所述经修改高速缓存行及与所述经修改高速缓存行相关联的元数据存储在由所述空日志存储器缓冲器的列表所引用的有效日志存储器缓冲器中;确定所述有效日志存储器缓冲器已满;及将旗标与所述有效日志存储器缓冲器相关联,从而将所述有效日志存储器缓冲器指示为已满的日志存储器缓冲器。

2、本公开的另一方面提供一种方法,其包括:接收物理存储器区域的基地址;接收空日志存储器缓冲器的列表;响应于确定所述物理存储器区域中的高速缓存行处于经修改状态,将所述经修改高速缓存行及与所述经修改高速缓存行相关联的元数据存储在由所述空日志存储器缓冲器的列表所引用的有效日志存储器缓冲器中;确定所述有效日志存储器缓冲器已满;及将旗标与所述有效日志存储器缓冲器相关联,从而将所述有效日志存储器缓冲器指示为已满的日志存储器缓冲器。

3、本公开的另一方面提供一种包括指令的非暂时性计算机可读存储媒体,所述指令在由处理装置执行时致使所述处理装置执行包括以下的操作:接收物理存储器区域的基地址;接收空日志存储器缓冲器的列表;接收启动消息以启动差量日志记录会话;将会话标识符与所述物理存储器区域的所述差量日志记录会话相关联;读取所述物理存储器区域内的一或多个高速缓存行的状态;响应于确定所述物理存储器区域中的高速缓存行处于经修改状态,将所述经修改高速缓存行及与所述经修改高速缓存行相关联的元数据存储在由所述空日志存储器缓冲器的列表所引用的有效日志存储器缓冲器中;确定所述有效日志存储器缓冲器已满;及将旗标与所述有效日志存储器缓冲器相关联,从而将所述有效日志存储器缓冲器指示为已满的日志存储器缓冲器。

技术特征:1.一种系统,其包括:

2.根据权利要求1所述的系统,其中所述操作进一步包括:

3.根据权利要求1所述的系统,其中所述操作进一步包括:

4.根据权利要求1所述的系统,其中所述元数据包括指示所述高速缓存行是否处于经修改状态的高速缓存行状态旗标及所述经修改高速缓存行的存储器地址。

5.根据权利要求1所述的系统,其中所述操作进一步包括:

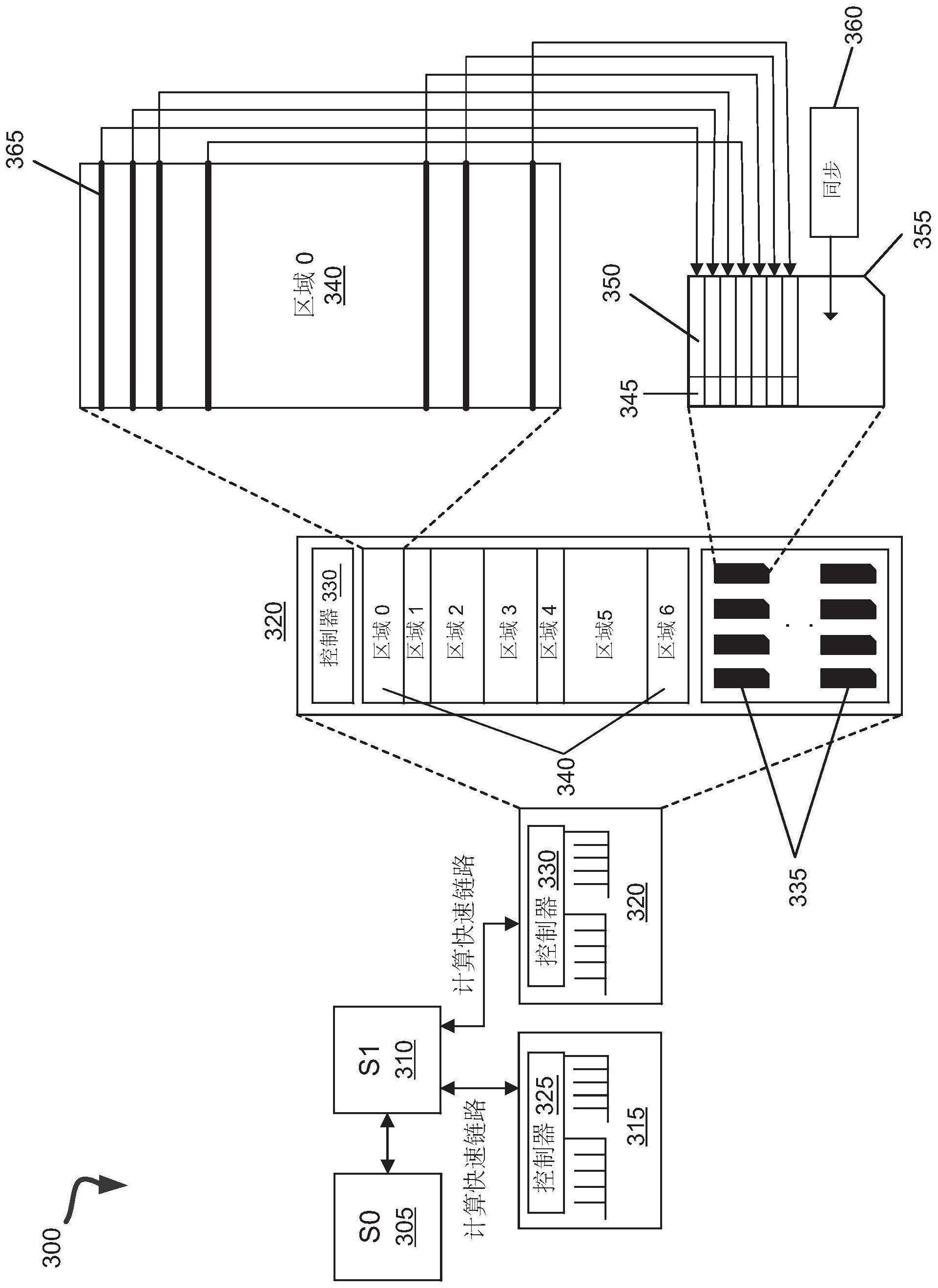

6.根据权利要求1所述的系统,其中所述系统包括计算快速链路cxl装置且其中所述处理装置是所述cxl装置的存储器控制器。

7.根据权利要求1所述的系统,其中所述cxl装置包括动态随机存取存储器dram、同步动态随机存取存储器sdram、铁电随机存取存储器feram、磁随机存取存储器mram及电阻式随机存取存储器rram中的一者。

8.根据权利要求1所述的系统,其中所述处理装置可操作地耦合到所述主机处理器,且所述主机处理器与所述处理装置之间的接口包括允许高速缓存行粒度更新且与所述处理装置共享一致性控制的计算快速链路cxl接口或通信链路。

9.一种方法,其包括:

10.根据权利要求9所述的方法,其进一步包括:

11.根据权利要求9所述的方法,其进一步包括:

12.根据权利要求9所述的方法,其中所述元数据包括指示所述高速缓存行是否处于经修改状态的高速缓存行状态旗标及所述经修改高速缓存行的存储器地址。

13.根据权利要求9所述的方法,其进一步包括:

14.一种包括指令的非暂时性计算机可读存储媒体,所述指令在由处理装置执行时致使所述处理装置执行包括以下的操作:

15.根据权利要求14所述的非暂时性计算机可读存储媒体,所述操作进一步包括:

16.根据权利要求14所述的非暂时性计算机可读存储媒体,所述操作进一步包括:

17.根据权利要求14所述的非暂时性计算机可读存储媒体,其中所述元数据包括指示所述高速缓存行是否处于经修改状态的高速缓存行状态旗标及所述经修改高速缓存行的存储器地址。

18.根据权利要求14所述的非暂时性计算机可读存储媒体,其中所述操作进一步包括:存储已满的日志存储器缓冲器的列表,其中所述列表对主机处理器可见。

19.根据权利要求14所述的非暂时性计算机可读存储媒体,其中所述处理装置是cxl装置的存储器控制器,所述cxl装置包括动态随机存取存储器dram、同步动态随机存取存储器sdram、铁电随机存取存储器feram、磁随机存取存储器mram及电阻式随机存取存储器rram中的一者。

技术总结本公开涉及以高速缓存行粒度跟踪存储器修改。一种方法包含:接收物理存储器区域的基地址;接收与差量日志记录会话相关联的空日志存储器缓冲器的列表;及响应于确定与所述物理存储器区域相关联的高速缓存行可能处于经修改状态,将所述经修改高速缓存行及与所述经修改高速缓存行相关联的元数据存储在由所述空日志存储器缓冲器的列表所引用的有效日志存储器缓冲器中。所述方法还包含确定所述有效日志存储器缓冲器已满,并将旗标附加到所述有效日志存储器缓冲器,从而将所述有效日志存储器缓存器标记为已满的日志存储器缓冲器。所述方法还包含存储已满的日志存储器缓冲器的列表,其中所述列表对主机处理器可见。技术研发人员:D·博尔斯受保护的技术使用者:美光科技公司技术研发日:技术公布日:2024/1/16本文地址:https://www.jishuxx.com/zhuanli/20240731/182238.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 YYfuon@163.com 举报,一经查实,本站将立刻删除。

下一篇

返回列表