改善NOR型闪存存储器耐受力的方法与流程

- 国知局

- 2024-07-31 19:17:50

本发明涉及一种闪存存储器技术,且特别涉及一种改善nor型闪存存储器耐受力的方法。

背景技术:

1、闪存存储器由于具有使存入的数据在断电后也不会消失的优点,因此成为个人电脑和其他电子设备所广泛采用的一种存储器。闪存存储器一般来说包括基板、依序堆叠于基板上的隧穿氧化层、浮置栅极、介电层与控制栅极、以及源极与漏极。

2、闪存存储器包括或非式(nor型)闪存存储器以及与非式(nand型)闪存存储器,其中nor型闪存存储器在数据读取速度方面较快,其是通过热电子注入的方式进行写入(program),使电子隧穿于浮置栅极内,另通过fn隧穿效应(fowler nordheim tunneling)进行抹除。然而,经过多次写入/抹除循环之后,电子容易累积于靠近漏极端的隧穿氧化层以及隧穿氧化层与基板的交界处中。由于电子的累积会导致临界电压vt改变,使存储器窗口(memory window)逐渐缩小,导致抹除所需的时间逐渐增加,最终使得nor型闪存存储器的耐受力(endurance)降低而有寿命短的问题。

3、传统的解决方法是对含有闪存存储器的整体半导体装置进行加热退火,使在漏极端的隧穿氧化层以及隧穿氧化层与基板的交界处中的陷入电子(trapped electron)移出。然而,由于半导体装置通常已封装,所以这样的加热方式往往因为封装材的温度限制而无法达到所需高温,且整体效率不佳。

技术实现思路

1、本发明提供一种改善nor型闪存存储器耐受力的方法,能有效降低nor型闪存存储器内的界面陷阱(interface traps)与本体陷阱(bulk traps),同时不影响半导体装置中的封装材料与内连线,从而改善nor型闪存存储器的耐受力与使用寿命。

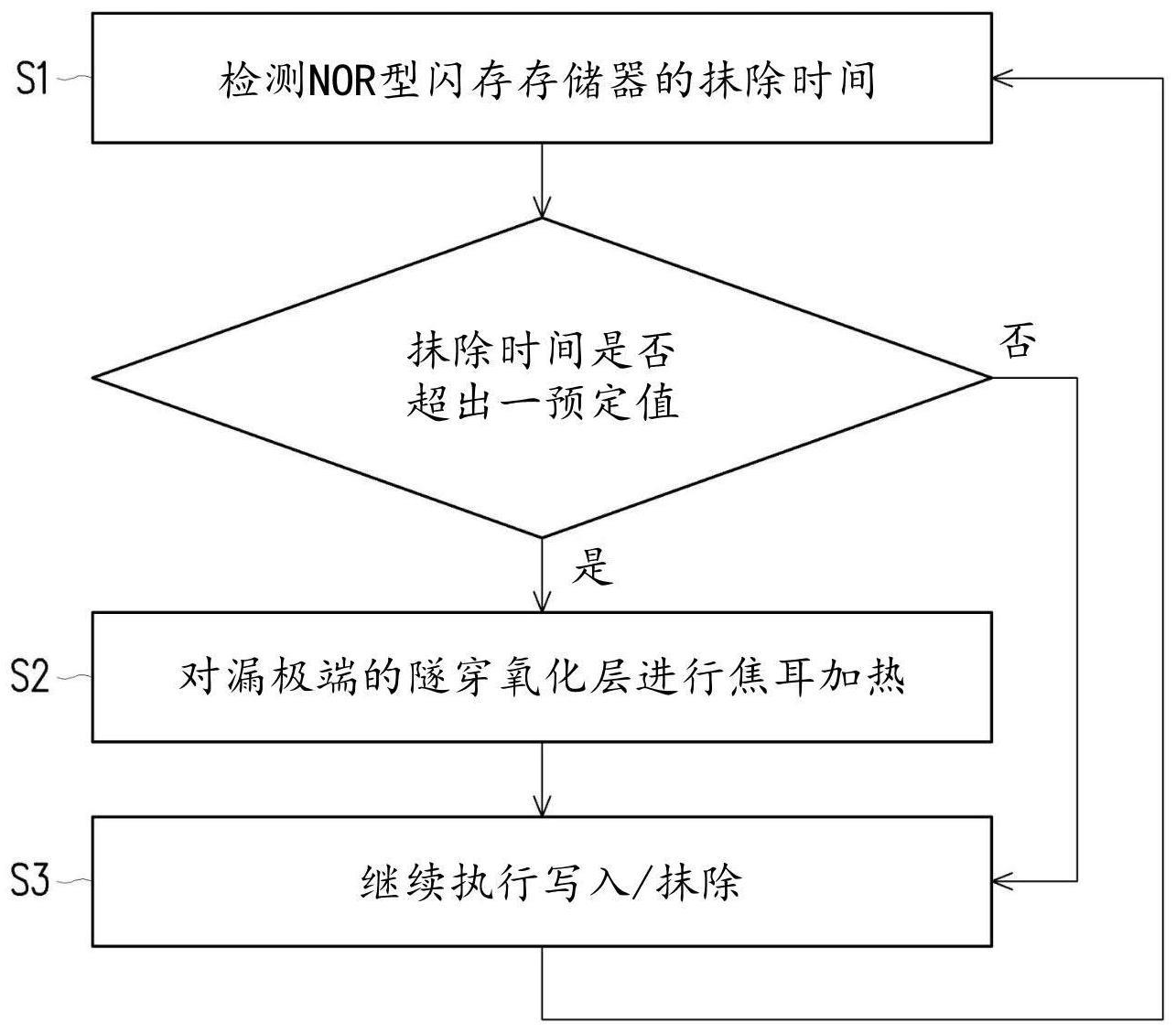

2、本发明改善nor型闪存存储器耐受力的方法,其中nor型闪存存储器包括基板、形成于基板内的阱区、依序堆叠于基板上的隧穿氧化层、浮置栅极、介电层与控制栅极、以及设置于阱区中的源极与漏极,方法包括:检测nor型闪存存储器的抹除时间;以及在抹除时间超出一预定值时,使源极处于浮置状态,施加负电压于控制栅极,以及施加正电压于阱区,以对漏极端进行焦耳加热。

3、在本发明的一实施例中,进行上述焦耳加热的时间大于1秒。

4、在本发明的一实施例中,进行上述焦耳加热的时间大于60秒。

5、在本发明的一实施例中,上述阱区为p型掺杂区。

6、在本发明的一实施例中,上述负电压为-2v。

7、在本发明的一实施例中,上述负电压小于-2v。

8、在本发明的一实施例中,上述正电压介于3v至5v之间。

9、在本发明的一实施例中,上述漏极的电压为0v。

10、在本发明的一实施例中,所述焦耳加热的温度在150℃至800℃之间。

11、基于上述,根据本发明的改善nor型闪存存储器耐受力的方法,通过在进行写入/抹除的过程中,同时检测所需的抹除时间,抹除时间超出一预定值时,通过对漏极端进行焦耳加热的方式,使靠近漏极端的隧穿氧化层以及隧穿氧化层与基板的交界处的陷入电子移出,以改善nor型闪存存储器的耐受力。而且,因为焦耳加热不会对半导体装置的其他部位加热,因此不影响半导体装置中的内连线或整体封装结构,而可改善其使用寿命。

12、为让本发明的上述特征和优点能更明显易懂,下文特举实施例,并配合所附的附图作详细说明如下。

技术特征:1.一种改善nor型闪存存储器耐受力的方法,其中所述nor型闪存存储器包括基板、形成于所述基板内的阱区、依序堆叠于所述基板上的隧穿氧化层、浮置栅极、介电层与控制栅极、以及设置于所述阱区中的源极与漏极,所述方法包括:

2.如权利要求1所述的改善nor型闪存存储器耐受力的方法,其中进行所述焦耳加热的时间大于1秒。

3.如权利要求1所述的改善nor型闪存存储器耐受力的方法,其中进行所述焦耳加热的时间大于60秒。

4.如权利要求1所述的改善nor型闪存存储器耐受力的方法,其中所述阱区为p型掺杂区。

5.如权利要求1所述的改善nor型闪存存储器耐受力的方法,其中所述负电压为-2v。

6.如权利要求1所述的改善nor型闪存存储器耐受力的方法,其中所述负电压小于-2v。

7.如权利要求1所述的改善nor型闪存存储器耐受力的方法,其中所述正电压介于3v至5v之间。

8.如权利要求1所述的改善nor型闪存存储器耐受力的方法,其中所述漏极的电压为0v。

9.如权利要求1所述的改善nor型闪存存储器耐受力的方法,其中所述焦耳加热的温度在150℃至800℃之间。

技术总结本发明公开一种改善NOR型闪存存储器耐受力的方法,其中NOR型闪存存储器包括基板、形成于基板内的阱区、依序堆叠于基板上的隧穿氧化层、浮置栅极、介电层与控制栅极、以及设置于阱区中的源极与漏极。所述方法包括:检测NOR型闪存存储器的抹除时间,并在抹除时间超出一预定值时,使源极处于浮置状态,施加负电压于控制栅极,施加正电压于阱区,以对漏极端进行焦耳加热。技术研发人员:张文岳受保护的技术使用者:力晶积成电子制造股份有限公司技术研发日:技术公布日:2024/1/16本文地址:https://www.jishuxx.com/zhuanli/20240731/182235.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 YYfuon@163.com 举报,一经查实,本站将立刻删除。

下一篇

返回列表