读操作方法及存储芯片、频率检测电路与流程

- 国知局

- 2024-07-31 19:36:20

本申请涉及存储,具体涉及一种读操作方法及存储芯片、频率检测电路。

背景技术:

1、随着技术的不断发展,存储芯片得到了更为广泛的应用。而不同的应用场景、不同的应用时段又对存储芯片提出了不同的需求。

2、因此,使得存储芯片能够满足不同的需求成为亟需解决的一个课题。

技术实现思路

1、本申请提供一种读操作方法及存储芯片、频率检测电路,以缓解读操作在不同应用场景中对频率、功耗的不同需求的技术问题。

2、第一方面,本申请提供一种读操作方法,该读操作方法包括:检测读指令的频率属于第一频率范围或者第二频率范围,第一频率范围高于第二频率范围;根据读指令的频率检测结果采用高频读取模式或者低频读取模式。

3、在其中一些实施方式中,根据读指令的频率检测结果采用高频读取模式或者低频读取模式,包括:若频率检测结果指示读指令的频率属于第一频率范围,控制驱动电路、读控制电路、参考电路、以及电荷泵中的至少一个进入高频读取模式;或者,若频率检测结果指示读指令的频率属于第二频率范围,控制驱动电路、读控制电路、参考电路、以及电荷泵中的至少一个进入低频读取模式。

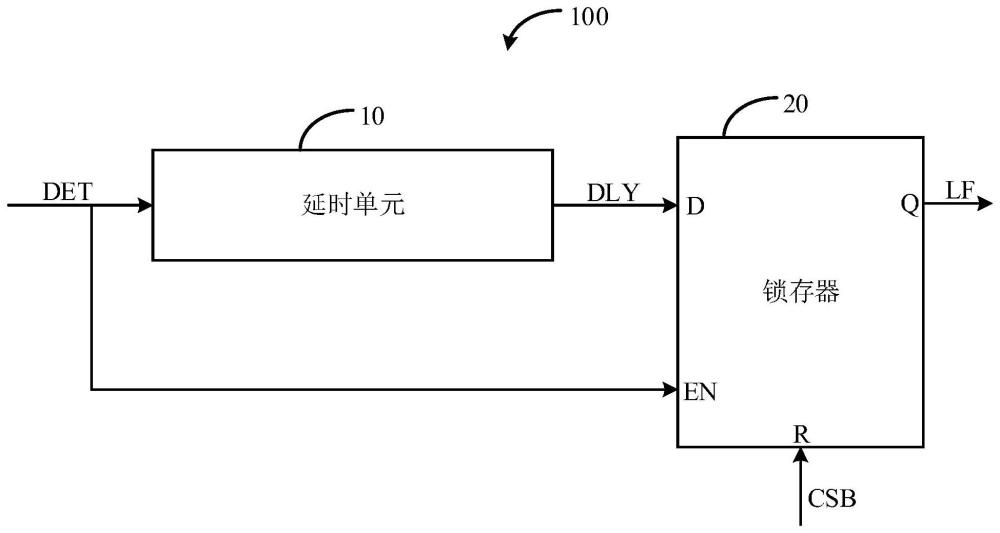

4、在其中一些实施方式中,检测读指令的频率属于第一频率范围或者第二频率范围,包括:输入使能信号、清零控制信号、以及输入信号依次分别至锁存器的使能端、复位端、输入端,输入信号是使能信号延迟一滞后时段后得到的;根据锁存器的输出信号的电位确定读指令的频率属于第一频率范围或者第二频率范围;其中,在用户下读指令后的时段中或者每次读操作之前的时段中,使能信号持续一段时间。

5、在其中一些实施方式中,根据锁存器的输出信号的电位确定读指令的频率属于第一频率范围或者第二频率范围,包括:响应于锁存器的输出信号处于逻辑高电位而确定读指令的频率属于第二频率范围;或者,响应于锁存器的输出信号处于逻辑低电位而确定读指令的频率属于第一频率范围。

6、在其中一些实施方式中,响应于锁存器的输出信号处于逻辑高电位而确定读指令的频率属于第二频率范围,包括:在用户下读指令后的时段中或者每次读操作之前的时段中,设置使能信号的高电位保持时间为n*tclk,其中,n为正数,tclk为时钟信号的时钟周期;在高电位保持时间大于或者等于滞后时段的情况下,锁存器的输出信号处于逻辑高电位。

7、在其中一些实施方式中,响应于锁存器的输出信号处于逻辑低电位而确定读指令的频率属于第一频率范围,包括:在用户下读指令后的时段中或者每次读操作之前的时段中,设置使能信号的高电位保持时间为n*tclk,其中,n为正数,tclk为时钟信号的时钟周期;在高电位保持时间小于或者等于滞后时段的情况下,锁存器的输出信号处于逻辑低电位。

8、在其中一些实施方式中,输入使能信号、清零控制信号、以及输入信号依次分别至锁存器的使能端、复位端、输入端,包括:响应于用户下读指令之前或者之后,设置清零控制信号处于高电位,以使得锁存器的输出信号处于逻辑低电位。

9、在其中一些实施方式中,驱动电路包括具有第一尺寸的晶体管的第一驱动电路和具有第二尺寸的晶体管的第二驱动电路,第一尺寸大于第二尺寸,根据读指令的频率检测结果采用高频读取模式或者低频读取模式,包括:响应于频率检测结果指示读指令的频率属于第一频率范围,而选择第一驱动电路处于工作状态;或者,响应于频率检测结果指示读指令的频率属于第二频率范围,而选择第二驱动电路处于工作状态。

10、在其中一些实施方式中,根据读指令的频率检测结果采用高频读取模式或者低频读取模式,还包括:响应于频率检测结果指示读指令的频率属于第一频率范围,而控制读控制电路减少读检测时间;或者,响应于频率检测结果指示读指令的频率属于第二频率范围,而控制读控制电路增加读检测时间。

11、在其中一些实施方式中,根据读指令的频率检测结果采用高频读取模式或者低频读取模式,还包括:响应于频率检测结果指示读指令的频率属于第一频率范围,而控制参考电路在读指令的整个执行期间中为灵敏放大器提供参考电流;或者,响应于频率检测结果指示读指令的频率属于第二频率范围,而在两个读操作之间的间隔时段中关闭参考电路。

12、在其中一些实施方式中,根据读指令的频率检测结果采用高频读取模式或者低频读取模式,还包括:响应于频率检测结果指示读指令的频率属于第一频率范围,而提高电荷泵的输出能力;或者,响应于频率检测结果指示读指令的频率属于第二频率范围,而降低电荷泵的输出能力。

13、第二方面,本申请提供一种存储芯片,该存储芯片包括驱动电路、执行电路,读频率检测电路用于检测读指令的频率属于第一频率范围或者第二频率范围,第一频率范围高于第二频率范围;执行电路用于根据读指令的频率检测结果采用高频读取模式或者低频读取模式。

14、第三方面,本申请提供一种频率检测电路,该频率检测电路包括延时单元和锁存器,延时单元的一端接入使能信号,延时单元的另一端输出输入信号,输入信号是使能信号延迟一滞后时段后得到的;锁存器的使能端接入使能信号,锁存器的输入端接入输入信号,锁存器的复位端接入清零控制信号,锁存器的输出端输出频率指示信号;其中,频率指示信号的逻辑高电位用于指示指令的频率属于第二频率范围,频率指示信号的逻辑低电位用于指示指令的频率属于第一频率范围。

15、在其中一些实施方式中,指令包括读指令,在用户下读指令后的时段中或者每次读操作之前的时段中,使能信号持续一段时间。

16、本申请提供的读操作方法及存储芯片、频率检测电路,通过检测读指令的频率是属于更高的第一频率范围还是更低的第二频率范围,能够识别出读指令的频率高低,再根据读指令的频率高低进入高频读取模式或者低频读取模式,进而有利于实现在读指令的更高频率应用场景中提高读操作的频率,在读指令的更低频率应用场景中降低读操作的功耗。

17、又,上述读操作方法及存储芯片、频率检测电路不仅能够识别读指令的频率,而且还开发出了针对不同读指令的频率的不同应用场景,这丰富并提高了用户的体验。

技术特征:1.一种读操作方法,其特征在于,所述读操作方法包括:

2.根据权利要求1所述的读操作方法,其特征在于,所述根据所述读指令的频率检测结果采用高频读取模式或者低频读取模式,包括:

3.根据权利要求2所述的读操作方法,其特征在于,所述检测读指令的频率属于第一频率范围或者第二频率范围,包括:

4.根据权利要求3所述的读操作方法,其特征在于,所述根据所述锁存器的输出信号的电位确定所述读指令的频率属于第一频率范围或者第二频率范围,包括:

5.根据权利要求4所述的读操作方法,其特征在于,所述响应于所述锁存器的输出信号处于逻辑高电位而确定所述读指令的频率属于第二频率范围,包括:

6.根据权利要求4所述的读操作方法,其特征在于,所述响应于所述锁存器的输出信号处于逻辑低电位而确定所述读指令的频率属于第一频率范围,包括:

7.根据权利要求3所述的读操作方法,其特征在于,所述输入使能信号、清零控制信号、以及输入信号依次分别至锁存器的使能端、复位端、输入端,包括:

8.根据权利要求1-7任一项所述的读操作方法,其特征在于,所述驱动电路包括具有第一尺寸的晶体管的第一驱动电路和具有第二尺寸的晶体管的第二驱动电路,所述第一尺寸大于所述第二尺寸,所述根据所述读指令的频率检测结果采用高频读取模式或者低频读取模式,包括:

9.根据权利要求2所述的读操作方法,其特征在于,所述根据所述读指令的频率检测结果采用高频读取模式或者低频读取模式,还包括:

10.根据权利要求2所述的读操作方法,其特征在于,所述根据所述读指令的频率检测结果采用高频读取模式或者低频读取模式,还包括:

11.根据权利要求2所述的读操作方法,其特征在于,所述根据所述读指令的频率检测结果采用高频读取模式或者低频读取模式,还包括:

12.一种存储芯片,其特征在于,所述存储芯片包括:

13.一种频率检测电路,其特征在于,所述频率检测电路包括:

14.根据权利要求13所述的频率检测电路,其特征在于,所述指令包括读指令,在用户下所述读指令后的时段中或者每次读操作之前的时段中,所述使能信号持续一段时间。

技术总结本申请公开了一种读操作方法及存储芯片、频率检测电路,该读操作方法通过检测读指令的频率是属于更高的第一频率范围还是更低的第二频率范围,能够识别出读指令的频率高低,再根据读指令的频率高低进入高频读取模式或者低频读取模式,进而有利于实现在读指令的更高频率应用场景中提高读操作的频率,在读指令的更低频率应用场景中降低读操作的功耗。技术研发人员:杜艳强受保护的技术使用者:武汉新芯集成电路制造有限公司技术研发日:技术公布日:2024/1/25本文地址:https://www.jishuxx.com/zhuanli/20240731/183153.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 YYfuon@163.com 举报,一经查实,本站将立刻删除。

下一篇

返回列表