写入前弱预充电双轨SRAM写入优化的制作方法

- 国知局

- 2024-07-31 19:36:17

背景技术:

1、参考图1,存储器单元140是耦接到相关联电路的示例性六晶体管双轨静态随机存取存储器(sram)单元。存储器单元140包括具有由字线wl驱动的栅极的传输晶体管101和传输晶体管103。存储器单元140还包括通过传输晶体管耦接到位线blt和位线blc的两个交叉耦合反相器。位线blt和blc被预充电并且具有显著的电容,因为许多存储器单元出于密度目的而耦接到这些位线。字线驱动器113断言(即,设定为有效电平)字线wl上的信号用于读取操作,从而致使电荷从位线递送到存储器单元中。

2、预充电晶体管134和138响应于控制器和地址解码器130对预充电信号blpcx的断言而将位线blt和位线blc预充电到vdd(例如,存储器单元140的电源电压或控制器和地址解码器130的电源电压),以为存储器单元操作(即,读取或写入)做准备。预充电信号blpcx为低有效,如“x”所指示。均衡器晶体管136耦接到blpcx,并且在预充电信号blpcx有效时将位线blt和位线blc短接在一起。

3、读出放大器电路120包括用以选择期望的位线对以耦接到读出放大器电路120的读取列选择晶体管102和读取列选择晶体管104。读取列选择晶体管102耦接(或隔离)位线真blt和读出放大器真线sat。读取列选择晶体管104耦接(或隔离)位线补数blc和读出放大器补线sac。如“x”所指示,读取列选择控制信号rdcsx为低有效。预充电晶体管114和预充电晶体管116响应于低有效的读出放大器预充电信号sapcx的断言而将读出放大器真线sat和读出放大器补线sac预充电到vdd,以为读取操作做准备。均衡器晶体管118还耦接到读出放大器预充电信号sapcx,并且在预充电有效时将读出放大器真线sat和读出放大器补线sac短接在一起。一旦读出放大器真线sat和读出放大器补线sac被预充电,并且位线blt和blc被上述单独的预充电电路预充电,则预充电晶体管114和116以及均衡器晶体管118被关断,读取列选择被导通以将位线blt和blc耦接到读出放大器真线sat和读出放大器补线sac。对应于正被读取的存储器单元的值,在读出放大器真线sat和读出放大器补线sac上构建差分电荷。一旦构建了差分电荷,就使用读出放大器使能信号saen导通差分读出放大器电路120,以使尾晶体管126能够锁存正被读取的存储器单元的值。

4、写入驱动器170包括具有由写入列选择线wrcs驱动的栅极的传输晶体管150和传输晶体管152。在一个实施方案中,写入驱动器170包括分别经由传输晶体管150和传输晶体管152分别耦接到位线blt和位线blc的下拉晶体管154和下拉晶体管156。对于写入操作,控制器和地址解码器130断言写入列选择线wrcs,以致使存储器单元根据如“x”指示的为低有效的写入数据信号wdt_x和写入数据信号wdc_x从位线放电。

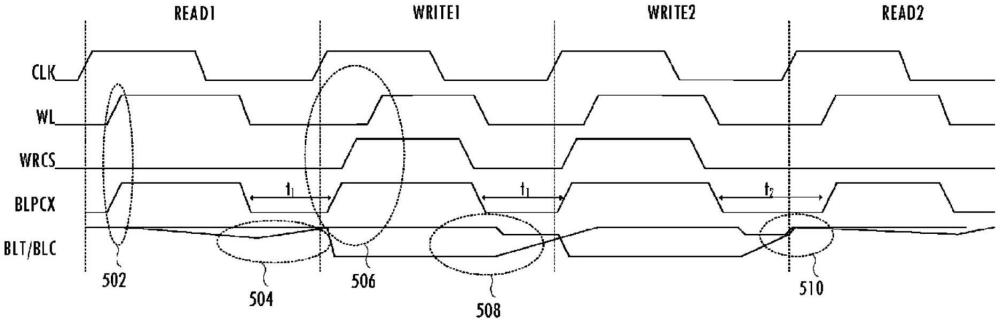

5、参考图1和图2,在存储器单元140的示例性写入操作中,位线blt和blc在第一存储器操作之后并且在下一存储器操作之前被预充电到vdd。如果下一操作是读取,则在开始在位线上形成差分(例如,大约5mv-10mv的差分)之前,需要将两个位线完全预充电到vdd。在下一访问是写入的情况下,写入驱动器170需要在预充电位线之后并且在断言字线wl之前根据写入数据wdt_x和wdc_x来驱动位线blt和blc上的数据。字线wl的断言致使高节点通过n型晶体管放电。n型晶体管具有足以克服存储器单元140的上拉的强度。经由源极跟随器n型晶体管转移装置将弱‘1’写入到存储器单元140。在至少一个实施方案中,当新数据到达(例如,将位线blc驱动到vdd)时,不存在到vdd的强路径,因为写入驱动器仅使用n型晶体管。如果写入驱动器170在断言字线wl之前或在断言该字线的同时未完全驱动位线blt和blc上的数据,则存储器单元140开始读取操作,例如将位线blc驱动到接地并且位线blt停留在vdd处,并且写入失败,如图3所示。因此,期望用于写入存储器单元的改进技术。

技术实现思路

1、在本发明的至少一个实施方案中,一种用于访问存储器单元的方法包括在对该存储器单元的下一访问之前启用对该存储器单元的位线的预充电。该方法包括在该下一访问是写入的情况下,在第一间隔之后禁用该预充电。该方法包括在该下一访问是读取的情况下,在第二间隔之后禁用该预充电。该第一间隔比该第二间隔短。

2、在本发明的至少一个实施方案中,一种存储器包括存储器单元,该存储器单元耦接到位线并且响应于位线预充电控制信号、存储器单元选择信号和存储器单元写入控制信号。该存储器包括控制电路,该控制电路被配置为生成该位线预充电控制信号、该存储器单元选择信号和该存储器单元写入控制信号以在对该存储器单元的下一访问之前启用对该位线的预充电,在该下一访问是写入的情况下在第一间隔之后禁用该预充电,并且在该下一访问是读取的情况下在第二间隔之后禁用该预充电。该第一间隔比该第二间隔短。

技术特征:1.一种用于访问存储器单元的方法,所述方法包括:

2.根据权利要求1所述的方法,

3.根据权利要求1所述的方法,

4.根据权利要求1所述的方法,其中前一访问是读取,所述下一访问是写入,并且所述位线被预充电到电源电压。

5.根据权利要求1所述的方法,其中前一访问是写入,所述下一访问是写入,并且所述位线被弱预充电到电源电压的最多90%。

6.根据权利要求1、2、3、4或5所述的方法,其中所述第一间隔基本上比所述第二间隔短。

7.根据权利要求1、2、3、4或5所述的方法,其中存储器单元控制电路接收具有第一正电压范围的电源电压,并且所述存储器单元接收具有第二正电压范围的第二电源电压。

8.根据权利要求1、2、3、4或5所述的方法,其中所述写入与时钟信号同步,所述时钟信号具有与访问包括所述存储器单元的存储器阵列的处理器的第二时钟信号相同的频率。

9.根据权利要求1、2、3、4或5所述的方法,其中与将字线控制信号复位为无效电平同时断言位线预充电控制信号。

10.一种存储器,包括:

11.根据权利要求10所述的存储器,

12.根据权利要求10所述的存储器,

13.根据权利要求10所述的存储器,其中前一访问是读取,所述下一访问是写入,并且所述位线被预充电到电源电压。

14.根据权利要求10所述的存储器,其中前一访问是写入,所述下一访问是写入,并且所述位线被弱预充电到电源电压的最多90%。

15.根据权利要求10、11、12、13或14所述的存储器,其中所述第一间隔基本上比所述第二间隔短。

16.根据权利要求10、11、12、13或14所述的存储器,其中所述控制电路断言字线控制信号并且同时将所述位线预充电控制信号复位为无效电平以进行读取访问。

17.根据权利要求10、11、12、13或14所述的存储器,其中所述控制电路在将所述位线预充电控制信号复位为无效电平以进行写入访问之后断言字线控制信号。

18.根据权利要求10、11、12、13或14所述的存储器,其中所述控制电路接收具有第一正电压范围的电源电压,并且所述存储器单元接收具有第二正电压范围的第二电源电压。

技术总结一种用于访问存储器单元的方法包括在对该存储器单元的下一访问之前启用对该存储器单元的位线的预充电。该方法包括在该下一访问是写入的情况下,在第一间隔之后禁用该预充电。该方法包括在该下一访问是读取的情况下,在第二间隔之后禁用该预充电。该第一间隔比该第二间隔短。技术研发人员:塔菲克·艾哈迈德,安德鲁·J·罗比森,拉塞尔·J·施瑞博尔受保护的技术使用者:超威半导体公司技术研发日:技术公布日:2024/1/25本文地址:https://www.jishuxx.com/zhuanli/20240731/183145.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 YYfuon@163.com 举报,一经查实,本站将立刻删除。