用于写入路径中的定时控制的设备的制作方法

- 国知局

- 2024-07-31 19:32:11

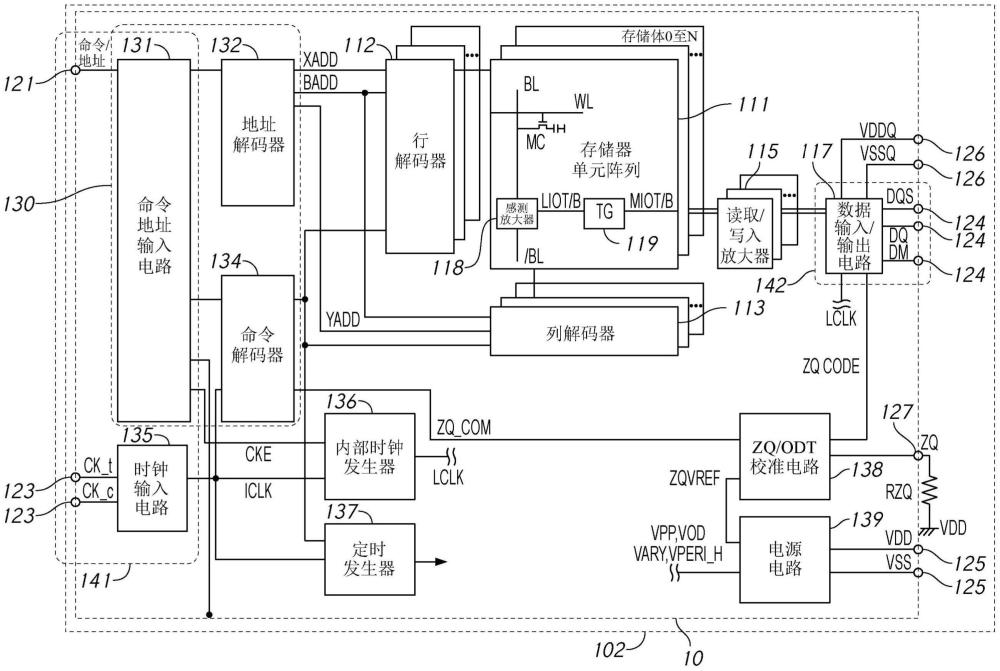

本申请涉及用于写入路径中的定时控制的设备。

背景技术:

1、高数据可靠性、高速存储器存取、较低功率消耗和减小的芯片大小是半导体存储器所需要的特征。为了实现较高存储器存取速度,使用时钟信号(ck)和数据队列选通信号(dqs)作为参考信号来调整半导体存储器中的操作定时。

2、最新的半导体存储器包含命令、地址、控制信号和定时信号的飞越拓扑布局,包含用于将数据写入到存储器芯片中的时钟信号和数据队列选通信号。拓扑布局包含长度缩短的更少短截线,从而减少噪声。然而,飞越拓扑布局可能会导致时钟信号和数据队列选通信号出现时间偏差。为了解决偏差问题,可执行写入均衡训练。

3、写入均衡训练的流程可包含外部写入均衡和内部写入均衡。半导体存储器的外部写入均衡允许半导体存储器外部的存储器控制器补偿由于外部时钟与dqs引脚之间的未对准而引起的延迟差异。为了执行外部写入均衡,在用于dqs的路径上提供等效于命令路径的延迟。

4、半导体存储器的内部写入均衡在半导体存储器内补偿时钟信号与数据队列选通信号之间的内部延迟差异。半导体存储器提供可编程延迟设置,包含可由存储器控制器执行的写入均衡内部循环对准(wica)。存储在模式寄存器中的wica值特定于每一装置、其写入前导码设置和所使用的操作频率。存储器控制器可以使用写入均衡训练和wica值来控制写入路径中的延迟,以与写入命令指示写入操作之后的cas写入时延(cwl)延迟对准。在内部写入均衡期间,等效于命令路径的延迟从用于dqs的路径中省略。

5、在内部写入均衡期间,通过以一个时钟信号循环对时间延迟和启动时间向上取整来计算wica设置。因此,仅使用wica值计算的dqs的微调可能会受到影响,且微调的最大差异可能在一个时钟循环的范围内。因此,可能需要更好地计算dqs的微调以改善dqs的偏移。

技术实现思路

1、在一个方面中,本申请提供一种设备,其包括:时钟输入电路,其被配置成接收外部时钟信号且进一步被配置成提供内部时钟信号;命令解码器,其被配置成接收命令信号和所述内部时钟信号,且进一步被配置成响应于所述命令信号指示写入操作而提供处于活动状态的写入命令信号;写入时延移位器,其被配置成接收所述写入命令信号、时延值和写入均衡内部循环对准(wica)值,所述写入时延移位器被配置成响应于所述时延值和所述wica值而调整所述写入命令信号的定时,且进一步被配置成提供移位的写入命令信号;以及写入延迟锁定回路,其包括延迟线,所述延迟线被配置成接收所述移位的写入命令信号且进一步被配置成提供延迟的写入命令信号,其中所述写入延迟锁定回路被配置成提供所述wica值以设置从所述时钟输入电路到所述写入延迟锁定回路的传播时间。

2、在另一方面中,本申请提供一种设备,其包括:写入正向路径,其包含:命令解码器,其被配置成接收内部时钟信号和命令信号且进一步被配置成响应于命令信号指示写入操作而提供处于活动状态的写入命令信号;写入时延移位器,其被配置成接收所述写入命令信号、时延值和wica值,所述写入时延移位器被配置成响应于所述时延值和所述wica值而调整所述写入命令信号的定时,且进一步被配置成提供移位的写入命令信号;以及写入延迟锁定回路,其包括延迟线,所述延迟线被配置成接收所述移位的写入命令信号且进一步被配置成提供延迟的写入命令信号,其中所述写入延迟锁定回路被配置成向所述写入时延移位器提供所述wica值以设置所述写入正向路径的传播时间。

3、在另一方面中,本申请提供一种设备,其包括:写入正向路径,其包括:时钟输入电路,其被配置成接收外部时钟信号且进一步被配置成提供内部时钟信号;命令/地址电路,其被配置成接收所述内部时钟信号和命令信号且进一步被配置成提供具有时间调整的写入命令信号;以及写入延迟锁定回路,其包括:延迟线,所述延迟线被配置成接收所述内部时钟信号且进一步被配置成提供延迟的内部时钟信号;延迟模型,其具有等效于所述时钟输入电路中的第一传播延迟和所述命令/地址电路中的第二传播延迟之和的模型传播延迟,所述延迟模型被配置成接收所述延迟的内部时钟信号且进一步被配置成提供反馈信号;以及测量初始化电路,其被配置成在开始节点处接收所述内部时钟信号且在停止节点处接收所述反馈信号,且进一步被配置成提供wica值,所述wica值指示等效于从所述时钟输入电路的输入节点到所述写入延迟锁定回路的输出节点的传播时间的循环数,其中所述写入延迟锁定回路被配置成将所述wica值提供到所述命令/地址电路以设置所述传播时间。

技术特征:1.一种设备,其包括:

2.根据权利要求1所述的设备,其中所述传播时间被设置为所述外部时钟信号的周期的整数倍。

3.根据权利要求1所述的设备,其中所述写入延迟锁定回路被配置成接收指示外部写入均衡模式或内部写入均衡模式的写入均衡模式,且进一步被配置成在所述写入均衡模式指示所述外部写入均衡模式时提供所述wica值。

4.根据权利要求3所述的设备,其被配置成通过执行所述外部写入均衡来完成写入均衡。

5.根据权利要求3所述的设备,其中所述wica值是第一wica值,并且

6.根据权利要求5所述的设备,其中所述内部写入均衡模式期间的所述第二wica值是基于所述第一wica值以及在从所述外部写入均衡模式切换到所述内部写入均衡模式时对数据选通信号的定时的偏移的向上取整。

7.根据权利要求3所述的设备,其中所述wica值是第一wica值,所述设备进一步包括:

8.根据权利要求7所述的设备,其中所述模式寄存器被配置成提供控制信号,所述控制信号指示所述选择器在所述外部写入均衡模式期间从所述写入延迟锁定回路提供所述第一wica值或在所述内部写入均衡模式期间从所述模式寄存器提供所述第二wica值。

9.根据权利要求1所述的设备,其中所述延迟线是第一延迟线,

10.根据权利要求9所述的设备,其中所述写入延迟锁定回路进一步包括测量初始化电路,所述测量初始化电路被配置成在开始节点处接收所述内部时钟信号且在停止节点处接收所述反馈信号,且进一步被配置成提供所述wica值。

11.根据权利要求10所述的设备,其中所述测量初始化电路被配置成在所述写入延迟锁定回路复位时计算所述wica值。

12.一种设备,其包括:

13.根据权利要求12所述的设备,其中所述传播时间被设置为所述内部时钟信号的周期的整数倍。

14.根据权利要求13所述的设备,其中所述延迟线是第一延迟线,

15.根据权利要求14所述的设备,其中所述测量初始化电路被配置成在所述写入延迟锁定回路复位时计算所述wica值。

16.根据权利要求14所述的设备,其中所述写入延迟锁定回路被配置成接收当前写入均衡模式,且进一步被配置成在所述当前写入均衡模式为外部写入均衡模式的情况下提供所述wica值。

17.根据权利要求16所述的设备,其中所述wica值是第一wica值,并且

18.根据权利要求17所述的设备,其中所述内部写入均衡模式期间的所述第二wica值是基于所述第一wica值以及在从所述外部写入均衡模式切换到所述内部写入均衡模式时对数据选通信号的定时的偏移的向上取整。

19.一种设备,其包括:

20.根据权利要求19所述的设备,其中所述传播时间被设置为所述外部时钟信号的周期的整数倍。

21.根据权利要求19所述的设备,其中所述命令/地址电路包括写入时延移位器,所述写入时延移位器被配置成接收所述写入命令信号、时延值和所述wica值,且进一步被配置成响应于所述时延值和所述wica值而调整所述写入命令信号的定时,且进一步被配置成提供具有时间调整的所述写入命令信号。

22.根据权利要求19所述的设备,其中所述wica值是第一wica值,

23.根据权利要求22所述的设备,其中所述模式选择器进一步被配置成在所述当前写入均衡模式为内部写入均衡模式的情况下提供第二wica值。

24.根据权利要求23所述的设备,其中所述内部写入均衡模式期间的所述第二wica值是基于所述第一wica值以及在从所述外部写入均衡模式切换到所述内部写入均衡模式时对数据选通信号的定时的偏移的向上取整。

技术总结公开了用于写入路径中的定时控制的设备。一种示例设备包含:时钟输入电路,其接收时钟信号且提供内部时钟信号;命令解码器,其接收命令信号和所述内部时钟信号,且在所述命令信号指示写入操作时提供活动的写入命令信号;写入时延移位器,其接收所述写入命令信号、时延值和WICA值,响应于所述时延值和所述WICA值而调整所述写入命令信号的定时,且提供移位的写入命令信号;以及写入DLL,其包含延迟线,所述延迟线接收所述移位的写入命令信号且提供延迟的写入命令信号。所述写入DLL提供所述WICA值以将从所述时钟输入电路到所述写入DLL的传播时间设置为所述时钟信号的周期的倍数。技术研发人员:三堀真吾,藤巻亮,上村裕受保护的技术使用者:美光科技公司技术研发日:技术公布日:2024/1/15本文地址:https://www.jishuxx.com/zhuanli/20240731/182967.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 YYfuon@163.com 举报,一经查实,本站将立刻删除。

下一篇

返回列表