一种低功耗寄存器堆电路

- 国知局

- 2024-07-31 19:32:08

本发明涉及寄存器堆电路,尤其是涉及一种低功耗寄存器堆电路。

背景技术:

1、随着高新技术如机器学习和人工智能的兴起,处理器性能需要面对海量数据和超大算力挑战。寄存器堆是由多个寄存器组成的阵列电路结构,用于暂存数据,是处理器数据交互的核心电路。寄存器堆的读写功耗和速度直接决定中央处理器(central processingunit,cpu)或图形处理器(graphics processing unit,gpu)的性能水平。

2、现有的寄存器堆电路通常包括译码模块、预充电模块、控制模块和两个存储阵列,每个存储阵列均由m×n个存储单元(即寄存器)按照m行n列分布形成,m为大于等于1的整数,n为大于等于1的整数,译码模块用于将列地址信号转译为对应的列地址选择信号,所述的列地址选择信号用于在写入操作或者读出操作时选中每个存储阵列中对应列存储单元,控制模块用于控制预充电模块和两个存储阵列按照预设时序工作以及将待存储数据转换为写入数据后,在执行写入操作时,将写入数据写入到每个存储阵列中当前被选中的存储单元中,预充电模块用于在执行读出操作时,通过控制充放电过程来判断读取两个存储阵列中当前被选中的存储单元输出的数据并进行输出。

3、现有的寄存器堆电路中,存储单元通常采用6t存储单元结构实现,待写入状态(即数据)在写入状态到达之前提前加载到存储单元的位线上,当被选中的存储单元的字线打开(执行写入操作)时会将其位线状态写入到其内两个互联反相器中进行保存。6t存储单元结构采用双端写入的方式,使用一组反相数据同时驱动其内两个互联反相器发生变化,从而同时完成一组反相数据的写入,其写入速度较快。但是,6t存储单元结构采用双端读取方式,在双端读取过程会有两条对地通路,增加了电路的泄露功耗,并且,其写入和读取使用同一对mos管,以致读取稳定性不高;另外,6t存储单元结构在写入状态时,1代表电源电压,0代表电源地,所以其任何写入过程都会有从电源电压到地的放电过程,导致写入过程中存在额外功耗损失。由此,采用6t存储单元结构实现的存储单元虽然写入速度较快,但是其功耗较高,读取稳定性不高,最终导致寄存器堆电路功耗较高,读取稳定性不高。

技术实现思路

1、本发明所要解决的技术问题是提供一种在写入速度较快的同时,功耗较低,且读取稳定性较高的低功耗寄存器堆电路。

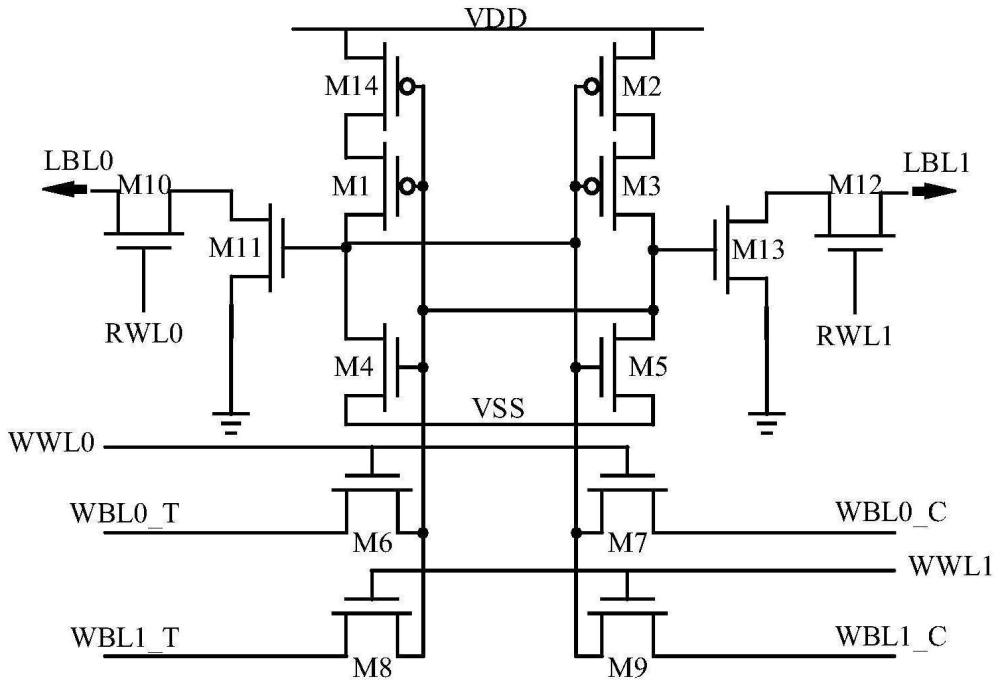

2、本发明解决上述技术问题所采用的技术方案为:一种低功耗寄存器堆电路,包括译码模块、预充电模块、控制模块和两个存储阵列,每个存储阵列均由m×n个存储单元按照m行n列分布形成,m为大于等于1的整数,n为大于等于1的整数,所述的译码模块用于将列地址信号转译为对应的列地址选择信号,所述的列地址选择信号用于在写入操作或者读出操作时选中每个存储阵列中对应列存储单元,所述的控制模块用于控制所述的预充电模块和两个存储阵列按照预设时序工作以及将待存储数据转换为写入数据后,在执行写入操作时,将写入数据写入到每个存储阵列中当前被选中的存储单元中,所述的预充电模块用于在执行读出操作时,通过控制充放电过程来判断读取两个存储阵列中当前被选中的存储单元输出的数据并进行输出,每个所述的存储单元均具有第一输入端口wbl0_t、第二输入端口wbl0_c、第三输入端口wbl1_t、第四输入端口wbl1_c、第五输入端口wwl0、第六输入端口rwl0、第七输入端口wwl1、第八输入端口rwl1、第一输出端口lbl0和第二输出端口lbl1,所述的存储单元的第一输入端口wbl0_t、第二输入端口wbl0_c、第三输入端口wbl1_t和第四输入端口wbl1_c用于数据写入,其中第一输入端口wbl0_t和第二输入端口wbl0_c写入的数据为一对相反数据,第三输入端口wbl1_t和第四输入端口wbl1_c写入的数据也为一对相反数据,第一输入端口wbl0_t和第二输入端口wbl0_c写入的一对相反数据中一个数据为有效数据,第三输入端口wbl1_t和第四输入端口wbl1_c写入的一对相反数据中一个数据为有效数据,即所述的存储单元每次能够写入两个有效数据,所述的存储单元的第五输入端口wwl0和第七输入端口wwl1分别用于接入写入操作的列地址选择信号,所述的存储单元的第六输入端口rwl0和第八输入端口rwl1用于接入分别用于接入读出操作的列地址选择信号,所述的存储单元的第一输出端口lbl0和第二输出端口lbl1用于将其内存储的两个有效数据进行对应输出;每个所述的存储单元均包括第一mos管、第二mos管、第三mos管、第四mos管、第五mos管、第六mos管、第七mos管、第八mos管、第九mos管、第十mos管、第十一mos管、第十二mos管、第十三mos管和第十四mos管,所述的第一mos管、所述的第二mos管、所述的第三mos管和所述的第十四mos管均为pmos管,所述的第四mos管、所述的第五mos管、所述的第六mos管、所述的第七mos管、所述的第八mos管、所述的第九mos管、所述的第十mos管、所述的第十一mos管、所述的第十二mos管和所述的第十三mos管均为nmos管,所述的第二mos管的源极和所述的第十四mos管的源极均接入电压vdd,所述的第二mos管的漏极和所述的第三mos管的源极连接,所述的第二mos管的栅极、所述的第三mos管的栅极、所述的第一mos管的漏极、所述的第十一mos管的栅极、所述的第四mos管的漏极、所述的第五mos管的栅极、所述的第七mos管的漏极和所述的第九mos管的漏极连接,所述的第三mos管的源极、所述的第五mos管的漏极、所述的第十三mos管的栅极、所述的第十四mos管的栅极、所述的第一mos管的栅极、所述的第四mos管的栅极、所述的第六mos管的源极和所述的第八mos管的源极连接,所述的第五mos管的源极和所述的第四mos管的源极连接,且其连接端接入电压vss,电压vss大于0,且小于电压vdd,所述的第十三mos管的漏极和所述的第十二mos管的漏极连接,所述的第十三mos管的源极接地,所述的第十二mos管的源极为所述的存储单元的第二输出端口lbl1,所述的第十二mos管的栅极为所述的存储单元的第八输入端口rwl1,所述的第十一mos管的漏极和所述的第十mos管的源极连接,所述的第十一mos管的源极接地,所述的第十mos管的漏极为所述的存储单元的第一输出端口lbl0,所述的第十mos管的栅极为所述的存储单元的第六输入端口rwl0,所述的第六mos管的栅极和所述的第七mos管的栅极连接,且其连接端为所述的存储单元的第五输入端口wwl0,所述的第六mos管的漏极为所述的存储单元的第一输入端口wbl0_t,所述的第七mos管的源极为所述的存储单元的第二输入端口wbl0_c,所述的第八mos管的栅极和所述的第九mos管的栅极连接,且其连接端为所述的存储单元的第七输入端口wwl1;所述的第八mos管的漏极为所述的存储单元的第三输入端口wbl1_t,所述的第九mos管的源极为所述的存储单元的第四输入端口wbl1_c,所述的第十四mos管的源极和所述的第一mos管的漏极连接。

3、所述的低功耗寄存器堆电路还包括输出缓冲模块,每个存储阵列均由64×32个存储单元按照64行32列分布形成,每个存储阵列中,位于第j行的32个存储单元的第一输入端口wbl0_t连接,且将其连接端称为第j行第1个输入端口,位于第j行的32个存储单元的第二输入端口wbl0_c连接,且将其连接端称为第j行第2个输入端口,位于第j行的32个存储单元的第三输入端口wbl1_t连接,且将其连接端称为第j行第3个输入端口,位于第j行的32个存储单元的第四输入端口wbl1_c连接,且将其连接端称为第j行第4个输入端口,位于第j行的32个存储单元的第一输出端口lbl0连接,且将其连接端称为第j行第1个输出端口,位于第j行的32个存储单元的第二输出端口lbl1连接,且将其连接端称为第j行第2个输出端口,j=1,2,…,64,第1行第1个输入端口至第64行第1个输入端口构成所述的存储阵列的第一输入端口,第1行第2个输入端口至第64行第2个输入端口构成所述的存储阵列的第二输入端口,第1行第3个输入端口至第64行第3个输入端口构成所述的存储阵列的第三输入端口,第1行第4个输入端口至第64行第4个输入端口构成所述的存储阵列的第四输入端口,第1行第1个输出端口至第64行第1个输出端口构成所述的存储阵列的第一输出端口,第1行第2个输出端口至第64行第2个输出端口构成所述的存储阵列的第二输出端口,位于第k列的64个存储单元的第五输入端口wwl0连接,且将其连接端称为第k列第1个输入端口,位于第k列的64个存储单元的第六输入端口rwl0连接,且将其连接端称为第k列第2个输入端口,位于第k列的64个存储单元的第七输入端口wwl1连接,且将其连接端称为第k列第3个输入端口,位于第k列的64个存储单元的第八输入端口rwl1连接,且将其连接端称为第k列第4个输入端口,k=1,2,…,32,第1列第1个输入端口至第32列第1个输入端口构成所述的存储阵列的第五输入端口,第1列第2个输入端口至第32列第2个输入端口构成所述的存储阵列的第六输入端口,第1列第3个输入端口至第32列第3个输入端口构成所述的存储阵列的第七输入端口,第1列第4个输入端口至第32列第4个输入端口构成所述的存储阵列的第八输入端口;所述的译码模块具有用于接入时钟信号clk的时钟输入端口、用于接入外部地址信号addr0<0:5>的第一地址输入端口、用于接入外部地址信号addr1<0:5>的第二地址输入端口、第一输出端口、第二输出端口、第三输出端口以及第四输出端口,所述的译码模块用于将地址信号addr0<0:5>转换为列地址选择信号wwl0<0:63>和列地址选择信号rwl0<0:63>以及将地址信号addr1<0:5>转换为列地址选择信号wwl1<0:63>和列地址选择信号rwl1<0:63>,其中列地址选择信号wwl0<0:63>在其第一输出端口输出,列地址选择信号rwl0<0:63>在其第二输出端口输出,列地址选择信号wwl1<0:63>在其第三输出端口输出,列地址选择信号rwl1<0:63>在其第四输出端口输出,其中,列地址选择信号wwl0<0:63>的第1到第32位wwl0<0:31>输出至所述的第一存储阵列的第五输入端口,第33到第64位wwl0<32:63>输出至所述的第二存储阵列的第五输入端口,列地址选择信号rwl0<0:63>的第1到第32位rwl0<0:31>输出至所述的第一存储阵列的第六输入端口,第33到第64位rwl0<32:63>输出至第二存储阵列的第六输入端口,列地址选择信号wwl1<0:63>的第1到第32位wwl1<0:31>输出至所述的第一存储阵列的第七输入端口,第33到第64位wwl1<32:63>输出至所述的第二存储阵列的第七输入端口,列地址选择信号rwl1<0:63>的第1到第32位rwl1<0:31>输出至所述的第一存储阵列的第八输入端口,第33到第64位rwl1<32:63>输出至所述的第二存储阵列的第八输入端口;wwl0<0:31>、wwl0<32:63>、wwl1<0:31>和wwl1<32:63>分别作为写入操作的列地址选择信号,rwl0<0:31>、rwl0<32:63>、rwl1<0:31>和rwl1<32:63>分别作为读出操作的列地址选择信号;列地址选择信号wwl0<0:63>在一个工作周期内只有一位信号为高电平,其余六十三位信号均为低电平,列地址选择信号rwl0<0:63>在一个工作周期内只有一位信号为高电平,其余六十三位信号均为低电平,列地址选择信号wwl1<0:63>在一个工作周期内只有一位信号为高电平,其余六十三位信号均为低电平,列地址选择信号rwl1<0:63>在一个工作周期内只有一位信号为高电平,其余六十三位信号均为低电平,且在同一个工作周期内,列地址选择信号wwl0<0:63>和列地址选择信号wwl1<0:63>不相同,列地址选择信号wwl0<0:63>和列地址选择信号rwl0<0:63>不相同,列地址选择信号wwl1<0:63>和列地址选择信号rwl1<0:63>不相同;所述的控制模块具有用于接入时钟信号clk的时钟输入端口、用于接入第一待存储数据data0<0:63>的第一输入端口、用于接入第二待存储数据data1<0:63>的第二输入端口、第一输出端口、第二输出端口、第三输出端口、第四输出端口、第一控制端、第二控制端和的第三控制端,所述的控制模块用于将时钟信号clk转换为第一预充电控制信号pch_b、第二预充电控制信号pch_t以及时钟控制信号ctrl_clk输出、将第一待存储数据data0<0:63>转换为第一写入数据wbl0_t<0:63>和第二写入数据wbl0_c<0:63>输出、以及将第二待存储数据data1<0:63>转换为第三写入数据wbl1_t<0:63>和第四写入数据wbl1_c<0:63>,第一预充电控制信号pch_b通过其第一控制端输出至所述的预充电模块,第二预充电控制信号pch_t通过其第二控制端输出至所述的预充电模块,时钟控制信号ctrl_clk通过其第三控制端输出至所述的预充电模块,第一预充电控制信号pch_b和第二预充电控制信号pch_t用于控制所述的预充电模块内部充放电时序,第一写入数据wbl0_t<0:63>通过其第一输出端口输出至所述的第一存储阵列和所述的第二存储阵列的第一输入端口,第二写入数据wbl0_c<0:63>通过其第二输出端口输出至所述的第一存储阵列和所述的第二存储阵列的第二输入端口,第三写入数据wbl1_t<0:63>通过其第三输出端口输出至所述的第一存储阵列和所述的第二存储阵列的第三输入端口,第四写入数据wbl1_c<0:63>通过其第四输出端口输出至所述的第一存储阵列和所述的第二存储阵列的第四输入端口;第一写入数据wbl0_t<0:63>和第二写入数据wbl0_c<0:63>为一对相反数据,用于在两个存储阵列中写入第一个存储数据,第三写入数据wbl1_t<0:63>和第四写入数据wbl1_c<0:63>为一对相反数据,用于在两个存储阵列中写入第二个存储数据;所述的预充电模块具有用于接入第二预充电控制信号pch_t的第一输入端口、用于接入第一预充电控制信号pch_b的第二输入端口、用于接入时钟控制信号ctrl_clk的第三输入端口、与所述的第一存储阵列输出的第一输出口连接的第四输入端口、与所述的第一存储阵列的第二输出端口连接的第五输入端口、与所述的第二存储阵列的第一输出端口连接的第六输入端口、与所述的第二存储阵列的第二输出端口连接的第七输入端口、用于输出第一数据信号rd0<0:63>的第一输出端口和用于输出第二数据信号rd1<0:63>的第二输出端口,其中第一数据信号rd0<0:63>表示从通过列地址选择信号rwl0<0:63>选中的存储单元处读取出来的存储数据信息,第二数据信号rd1<0:63>表示从通过列地址选择信号rwl1<0:63>选中的存储单元处读取出来的存储数据信息;所述的预充电模块在第一预充电控制信号pch_b和第二预充电控制信号pch_t控制下完成内部充放电过程,第一预充电控制信号pch_b、第二预充电控制信号pch_t都为低电平时,所述的预充电模块开启充电过程,在初始状态或写入状态对所述的预充电模块进行充电,第一预充电控制信号pch_b和第二预充电控制信号pch_t都为高电平时,关闭充电过程,在读取状态所述的预充电模块停止充电,所述的预充电模块通过判断所述的第一存储阵列的第一输出端口和第二输出端口、所述的第二存储阵列的第一输出端口和第二输出端口的电压变化状态发生变化,在其第一输出端口输出对应的第一数据信号rd0<0:63>,在其第二输出端口输出对应的第二数据信号rd1<0:63>,时钟控制信号ctrl_clk关闭时,两个存储阵列为初始状态或写入状态,此时所述的预充电模块输出的第一数据信号rd0<0:63>和第二数据信号rd1<0:63>不会发生变化,只能保持低电平输出,时钟控制信号ctrl_clk开启时所述的预充电模块为读取状态,此时所述的预充电模块输出的第一数据信号rd0<0:63>和第二数据信号rd1<0:63>会根据所述的第一存储阵列的第一输出端口和第二输出端口、所述的第二存储阵列的第一输出端口和第二输出端口的电压变化状态发生变化,进行高电平输出或保持低电平状态;所述的输出缓冲模块具有用于接入第一数据信号rd0<0:63>的第一输入端口、用于接入第二数据信号rd1<0:63>的第二输入端口、用于输出第一数据信号out0<0:63>的第一输出端口和用于输出第二数据信号out1<0:63>的第二输出端口,所述的输出缓冲模块用于将第一数据信号rd0<0:63>缓冲驱动为第一数据信号out0<0:63>后在其第一输出端口输出,所述的输出缓冲模块用于将第二数据信号rd1<0:63>缓冲驱动为第二数据信号out1<0:63>后在其第二输出端口输出;所述的译码模块的第一输出端口分别与两个存储阵列的第五输入端口对应连接,所述的译码模块的第二输出端口与两个存储阵列的第六输入端口对应连接,所述的译码模块的第三输出端口与两个存储阵列的第七输入端口对应连接,所述的译码模块的第四输出端口与两个存储阵列的第八输入端口对应连接,所述的控制模块的第一输出端口分别与两个存储阵列的第一输入端口连接,所述的控制模块的第二输出端口分别与两个存储阵列的第二输入端口连接,所述的控制模块的第三输出端口分别与两个存储阵列的第三输入端口连接,所述的控制模块的第四输出端口分别与两个存储阵列的第四输入端口连接,所述的控制模块的第一控制端与所述的预充电模块的第二输入端口连接,所述的控制模块的第二控制端与所述的预充电模块的第一输入端口连接,所述的控制模块的第三控制端与所述的预充电模块的第三输入端口连接,所述的预充电模块的第四输入端口与第一存储阵列的第一输出端口连接,所述的预充电模块的第五输入端口与第一存储阵列的第二输出端口连接,所述的预充电模块的第六输入端口与第二存储阵列的第一输出端口连接,所述的预充电模块的第七输入端口与第二存储阵列的第二输出端口连接,所述的预充电模块的第一输出端口与所述的输出缓冲模块的第一输入端口连接,所述的预充电模块的第二输出端口与所述的输出缓冲模块的第二输入端口连接。

4、所述的预充电模块包括两个预充电电路,每个所述的预充电电路均具有第一输入端、第二输入端、第三输入端、第四输入端、第五输入端和输出端,将两个预充电电路分别称为第一预充电电路和第二预充电电路,所述的第一预充电电路的第一输入端和所述的第二预充电电路的第一输入端连接,且其连接端为所述的预充电模块的第三输入端口,所述的第一预充电电路的第二输入端和所述的第二预充电电路的第二输入端连接,且其连接端为所述的预充电模块的第二输入端口,所述的第一预充电电路的第三输入端和所述的第二预充电电路的第三输入端连接,且其连接端为所述的预充电模块的第一输入端口,所述的第一预充电电路的第四输入端为所述的预充电模块的第四输入端口,所述的第一预充电电路的第五输入端为所述的预充电模块的第五输入端口,所述的第二预充电电路的第四输入端为所述的预充电模块的第六输入端口,所述的第二预充电电路的第五输入端为所述的预充电模块的第七输入端口,所述的第一预充电电路的输出端为所述的预充电模块的第一输出端口,所述的第二预充电电路的输出端为所述的预充电模块的第二输出端口;每个所述的预充电电路均包括第十五mos管、第十六mos管、第十七mos管、第十八mos管、第十九mos管、第二十mos管、第二十一mos管、第二十二mos管、第二十三mos管、第二十四mos管、第二十五mos管、第二十六mos管、第二十七mos管、第二十八mos管、第二十九mos管、第三十mos管、第三十一mos管、第三十二mos管、第三十三mos管、第三十四mos管、第三十五mos管、第三十六mos管、第三十七mos管、第三十八mos管、第三十九mos管、第四十mos管和第四十一mos管,所述的第十五mos管、所述的第十六mos管、所述的第十七mos管、所述的第十八mos管、所述的第十九mos管、所述的第二十mos管、所述的第二十三mos管、所述的第二十四mos管、所述的第二十五mos管、所述的第二十六mos管、所述的第二十八mos管、所述的第三十mos管、所述的第三十一mos管、所述的第三十二mos管、所述的第三十三mos管、所述的第三十六mos管、所述的第三十七mos管、所述的第三十八mos管和所述的第四十一mos管均为pmos管,所述的第二十一mos管、所述的第二十二mos管、所述的第二十七mos管、所述的第二十九mos管、所述的第三十四mos管、所述的第三十五mos管、所述的第三十九mos管和所述的第四十mos管均为nmos管;所述的第十五mos管的源极、所述的第十八mos管的源极、所述的第四十一mos管的源极、所述的第二十五mos管的源极、所述的第二十六mos管的源极、所述的第二十八mos管的源极、所述的第三十mos管的源极、所述的第三十二mos管的源极、所述的第三十三mos管的源极、所述的第三十六mos管的源极、所述的第三十七mos管的源极和所述的第三十八mos管的源极均接入电压vdd,所述的第十五mos管的栅极为所述的预充电电路的第二输入端,所述的第十五mos管的漏极、所述的第二十三mos管的漏极、所述的第二十二mos管的栅极和所述的第二十mos管的栅极连接,且其连接端为所述的预充电电路的第五输入端,所述的第二十三mos管的栅极、所述的第二十四mos管的栅极、所述的第二十五mos管的栅极、所述的第十六mos管的栅极、所述的第十七mos管的栅极和所述的第十八mos管的栅极连接,所述的第二十三mos管的源极和所述的第二十四mos管的漏极连接,所述的第二十四mos管的源极和所述的第二十五mos管的漏极连接,所述的第四十一mos管的栅极为所述的预充电电路的第三输入端,所述的第四十一mos管的漏极、所述的第十六mos管的漏极、所述的第十九mos管的栅极和所述的第二十一mos管的栅极连接,且其连接端为所述的预充电电路的第四输入端,所述的第十六mos管的源极和所述的第十七mos管的漏极连接,所述的第十七mos管的源极和所述的第十八mos管的漏极连接,所述的第十九mos管的源极和所述的第二十mos管的源极均接入电源电压vdd,所述的第十九mos管的漏极、所述的第二十mos管的漏极、所述的第二十一mos管的漏极、所述的第二十六mos管的栅极和所述的第二十七mos管的栅极连接,所述的第二十六mos管的漏极、所述的第二十七mos管的漏极、所述的第三十一mos管的漏极、所述的第三十mos管的漏极、所述的第三十四mos管的栅极和所述的第三十三mos管的栅极连接,所述的第二十七mos管的源极接地,所述的第二十八mos管的漏极、所述的第二十九mos管的漏极和所述的第三十mos管的栅极连接,所述的第二十九mos管的源极接地,所述的第二十八mos管的栅极、所述的第二十九mos管的栅极、所述的第三十七mos管的栅极和所述的第三十九mos管的栅极连接,且其连接端为所述的预充电电路的第一输入端,所述的第三十一mos管的源极和所述的第三十二mos管的漏极连接,所述的第三十三mos管的漏极、所述的第三十四mos管的漏极、所述的第三十一mos管的栅极、所述的第三十二mos管的栅极、所述的第三十六mos管的漏极、所述的第三十八mos管的栅极和所述的第四十mos管的栅极连接,且其连接端为所述的预充电电路的输出端,所述的第三十四mos管的源极和所述的第三十五mos管的漏极连接,所述的第三十五mos管的源极接地,所述的第三十五mos管的栅极、所述的第三十六mos管的栅极、所述的第三十七mos管的漏极、所述的第三十八mos管的漏极和所述的第三十九mos管的漏极连接,所述的第三十九mos管的源极和所述的第四十mos管的漏极连接,所述的第四十mos管的源极接地,所述的第二十一mos管的源极和所述的第二十二mos管的漏极连接,所述的第二十二mos管的源极接地。

5、所述的控制模块包括两个二输入与门和二十个反相器,每个所述的二输入与门均具有第一输入端、第二输入端和输出端,将两个二输入与门分别称为第一与门和第二与门,将二十个反相器分别称为第一反相器、第二反相器、第三反相器、第四反相器、第五反相器、第六反相器、第七反相器、第八反相器、第九反相器、第十反相器、第十一反相器、第十二反相器、第十三反相器、第十四反相器、第十五反相器、第十六反相器、第十七反相器、第十八反相器、第十九反相器和二十反相器,所述的第一与门的第一输入端为所述的控制模块的第一输入端口,所述的第一与门的第二输入端、所述的第二与门的第二输入端、所述的第五反相器的输入端、所述的第十一反相器的输入端和所述的第十六反相器的输入端连接,且其连接端为所述的控制模块的时钟输入端口,所述的第二与门的第一输入端为所述的控制模块的第二输入端口,所述的第一与门的输出端和所述的第一反相器的输入端连接,所述的第一反相器的输出端和所述的第二反相器的输入端连接,且其连接端为所述的控制模块的第二输出端口,所述的第二反相器的输出端为所述的控制模块的第一输出端口,所述的第二与门的输出端和所述的第三反相器的输入端连接,所述的第三反相器的输出端和所述的第四反相器的输入端连接,且其连接端为所述的控制模块的第四输出端口,所述的第四反相器的输出端为所述的控制模块的第三输出端口,所述的第五反相器的输出端和所述的第六反相器的输入端连接,所述的第六反相器的输出端和所述的第七反相器的输入端连接,所述的第七反相器的输出端和所述的第八反相器的输入端连接,所述的第八反相器的输出端和所述的第九反相器的输入端连接,所述的第九反相器的输出端和所述的第十反相器的输入端连接,所述的第十反相器的输出端为所述的控制模块的第第三控制端,所述的第十一反相器的输出端和所述的第十二反相器的输入端连接,所述的第十二反相器的输出端和所述的第十三反相器的输入端连接,所述的第十三反相器的输出端和所述的第十四反相器的输入端连接,所述的第十四反相器的输出端和所述的第十五反相器的输入端连接,所述的第十五反相器的输出端为所述的控制模块的第一控制端,所述的第十六反相器的输出端和所述的第十七反相器的输入端连接,所述的第十七反相器的输出端和所述的第十八反相器的输入端连接,所述的第十八反相器的输出端和所述的第十九反相器的输入端连接,所述的第十九反相器的输出端和所述的第二十反相器的输入端连接,所述的第二十反相器的输出端为所述的控制模块的第二控制端。

6、所述的输出缓冲模块包括第二十一反相器、第二十二反相器、第二十三反相器和第二十四反相器,所述的第二十一反相器的输入端为所述的输出缓冲模块的第一输入端口,所述的第二十一反相器的输出端和所述的第二十二反相器的输入端连接,所述的第二十二反相器的输出端为所述的输出缓冲模块的第一输出端口,所述的第二十三反相器的输入端为所述的输出缓冲模块的第二输入端口,所述的第二十三反相器的输出端和所述的第二十四反相器的输入端连接,所述的第二十四反相器的输出端为所述的输出缓冲模块的第二输出端口。

7、所述的译码模块包括两个译码模组,每个所述的译码模组均包括4个3-8译码器和128个二输入与门,每个所述的3-8译码器均具有三个输入端、八个输出端和时钟端,每个二输入与门具有两个输入端和一个输出端,将4个3-8译码器分别称为第一3-8译码器、第二3-8译码器、第三3-8译码器和第四3-8译码器,第一3-8译码器的第1个输出端与第1个至第8个二输入与门的第1个输入端均连接,第二3-8译码器的8个输出端与第1个至第8个二输入与门的第2个输入端一一对应连接,第一3-8译码器的第2个输出端与第9个至第16个二输入与门的第1个输入端均连接,第二3-8译码器的8个输出端与第9个至第16个二输入与门的第2个输入端一一对应连接,第一3-8译码器的第3个输出端与第17个至第24个二输入与门的第1个输入端均连接,第二3-8译码器的8个输出端与第17个至第24个二输入与门的第2个输入端一一对应连接,第一3-8译码器的第4个输出端与第25个至第32个二输入与门的第1个输入端均连接,第二3-8译码器的8个输出端与第25个至第32个二输入与门的第2个输入端一一对应连接,第一3-8译码器的第5个输出端与第33个至第40个二输入与门的第1个输入端均连接,第二3-8译码器的8个输出端与第33个至第40个二输入与门的第2个输入端一一对应连接,第一3-8译码器的第6个输出端与第41个至第48个二输入与门的第1个输入端均连接,第二3-8译码器的8个输出端与第41个至第48个二输入与门的第2个输入端一一对应连接,第一3-8译码器的第7个输出端与第49个至第56个二输入与门的第1个输入端均连接,第二3-8译码器的8个输出端与第49个至第56个二输入与门的第2个输入端一一对应连接,第一3-8译码器的第7个输出端与第57个至第64个二输入与门的第1个输入端均连接,第二3-8译码器的8个输出端与第57个至第64个二输入与门的第2个输入端一一对应连接,第三3-8译码器的第1个输出端与第65至第72个二输入与门的第1个输入端均连接,第四3-8译码器的8个输出端与第65个至第72个二输入与门的第2个输入端一一对应连接,第三3-8译码器的第2个输出端与第73个至第80个二输入与门的第1个输入端均连接,第四3-8译码器的8个输出端与第73个至第80个二输入与门的第2个输入端一一对应连接,第三3-8译码器的第3个输出端与第81个至第88个二输入与门的第1个输入端均连接,第四3-8译码器的8个输出端与第81个至第88个二输入与门的第2个输入端一一对应连接,第三3-8译码器的第4个输出端与第89个至第96个二输入与门的第1个输入端均连接,第四3-8译码器的8个输出端与第89个至第96个二输入与门的第2个输入端一一对应连接,第三3-8译码器的第5个输出端与第97个至第104个二输入与门的第1个输入端均连接,第四3-8译码器的8个输出端与第97个至第104个二输入与门的第2个输入端一一对应连接,第三3-8译码器的第6个输出端与第105个至第112个二输入与门的第1个输入端均连接,第四3-8译码器的8个输出端与第105个至第112个二输入与门的第2个输入端一一对应连接,第三3-8译码器的第7个输出端与第113个至第120个二输入与门的第1个输入端均连接,第四3-8译码器的8个输出端与第113个至第120个二输入与门的第2个输入端一一对应连接,第三3-8译码器的第7个输出端与第121个至第128个二输入与门的第1个输入端均连接,第四3-8译码器的8个输出端与第121个至第128个二输入与门的第2个输入端一一对应连接;将两个译码模组分别称为第一译码模组和第二译码模组;所述的第一译码模组的第一3-8译码器的三个输入端和所述的第二译码模组的第一3-8译码器的三个输入端一一对应连接,且其三个连接端作为第一组输入端,所述的第一译码模组的第二3-8译码器的三个输入端和所述的第二译码模组的第二3-8译码器的三个输入端一一对应连接,且其三个连接端作为第二组输入端,所述的第一组输入端和第二组输入端构成所述的译码模块的第一地址输入端口,所述的第一译码模组的第三3-8译码器的三个输入端和所述的第二译码模组的第三3-8译码器的三个输入端一一对应连接,且其三个连接端作为第三组输入端,所述的第一译码模组的第四3-8译码器的三个输入端和所述的第二译码模组的第四3-8译码器的三个输入端一一对应连接,且其三个连接端作为第四组输入端,所述的第三组输入端和第四组输入端构成所述的译码模块的第二地址输入端口,所述的第一译码模组的第1个二输入与门的输出端至第64个二输入与门的输出端作为所述的译码模块的第一输出端口,第65个二输入与门的输出端至第128个二输入与门的输出端作为所述的译码模块的第三输出端口,所述的第二译码模组的第1个二输入与门的输出端至第64个二输入与门的输出端作为所述的译码模块的第二输出端口,第65个二输入与门的输出端至第128个二输入与门的输出端作为所述的译码模块的第四输出端口,所述的第一译码模组和所述的第二译码模组的所有3-8译码器和所有二输入与门的时钟端连接,且其连接端为所述的译码模块的时钟输入端口。

8、与现有技术相比,本发明的优点在于通过第一mos管、第二mos管、第三mos管、第四mos管、第五mos管、第六mos管、第七mos管、第八mos管、第九mos管、第十mos管、第十一mos管、第十二mos管、第十三mos管和第十四mos管构成存储单元,当存储单元的第五输入端口wwl0、第六输入端口rwl0、第七输入端口wwl1和第八输入端口rwl1均为低电平时,此时存储单元为初始状态,第六mos管、第七mos管、第八mos管、第九mos管、第十mos管、第十一mos管、第十二mos管和第十三mos管均为关闭状态,第一mos管、第二mos管、第三mos管、第四mos管、第五mos管和第十四mos管开启,能够进行数据保存,如果此时存储单元的第五输入端口wwl0接入高电平,第六输入端口rwl0接入低电平,存储单元开始执行写入操作,第六mos管和第七mos管打开,第一输入端口wbl0_t和第二输入端口wbl0_c接入的数据通过第六mos管和第七mos管写入,数据写入完成后在由第一mos管、第二mos管、第三mos管、第四mos管、第五mos管和第十四mos管组成的互联反相器中进行存储,如果此时存储单元的第七输入端口wwl1接入高电平,第八输入端口rwl1接入低电平,存储单元开始执行写入操作,第八mos管和第九mos管打开,存储单元的第三输入端口wbl1_t和第四输入端口wbl1_c接入的数据通过第八mos管和第九mos管写入,在数据写入完成后,在由第一mos管、第二mos管、第三mos管、第四mos管、第五mos管和第十四mos管组成的互联反相器中进行存储;如果此时存储单元的第六输入端口rwl0接入高电平,开始进入到读取操作过程,第十mos管打开,存储单元内部存储的数据如果是1,则会打开第十一mos管,通过第十一mos管和第十mos管这条通路输出到其第一输出端口lbl0,将其第一输出端口lbl0的电压拉低,存储单元内部存储的数据如果是0,第十一mos管会关闭,存储单元的第一输出端口lbl0的电压保持不变,后续预充电模块通过判断是否有对地通路完成存储单元数据的读取过程;如果此时存储单元的第八输入端口rwl1接入高电平,开始进入到读取操作过程,第十二mos管打开,存储单元内部存储的数据如果是1,则会打开第十三mos管,通过第十三mos管第十二mos管这条通路输出到存储单元的第二输出端口lbl1,将存储单元的第二输出端口lbl1与地相连,存储单元内部存储的数据如果是0,第十三mos管会关闭,存储单元的第二输出端口lbl1的电压保持不变,后续预充电模块通过判断是否有对地通路完成存储单元数据的读取过程;通过后续预充电模块判断是否有对地通路完成数据读取过程;本发明的存储单元中,通过第六mos管和第七mos管进行双端写入加快数据写入速度,保证写入速度较快,第四mos管和第五mos管接入高于电源地(即0电压)的电压vss,降低了存储单元的充放电范围,从而降低由电源电压到电源地通路放电引起的功耗,电压vss根据实际使用需要设定,使用第十mos管和第十一mos管单端读取,降低了读取通路中的泄露功耗,并且由于第六mos管和第七mos管进行双端写入,使用第十mos管和第十一mos管进行读取,将写入和读取过程使用的mos管分隔开,提高读取稳定性,存储单元在写入速度较快的同时,功耗较低,且读取稳定性较高,由此本发明的低功耗寄存器堆电路在写入速度较快的同时,功耗较低,且读取稳定性较高。

本文地址:https://www.jishuxx.com/zhuanli/20240731/182963.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 YYfuon@163.com 举报,一经查实,本站将立刻删除。

下一篇

返回列表