忆阻阵列的测试系统及其测试方法及计算机可读存储介质与流程

- 国知局

- 2024-07-31 19:32:04

本技术涉及忆阻器测试,尤其涉及一种忆阻阵列的测试系统及其测试方法及计算机可读存储介质。

背景技术:

1、rram(resistive random access memory)是一种新型的阻变式存储器,也称为忆阻器,为简单的mim(metal-insulator-metal,金属-绝缘体-金属)的三明治电容结构,通过两端金属极施加外加电场使得忆阻材料的阻值在高阻态和低阻态之间转换,以此来实现二值存储。因为其高速度、低功耗、非易失特性、与传统cmos工艺兼容等优点,被认为是最有潜力的下一代非挥发存储技术。

2、忆阻器还被应用在神经形态计算领域,其中忆阻器模拟电子突触,其组成的阻变存储器阵列具备存算一体能力,将神经网络的权重映射到忆阻器的电导值后,阻变存储器阵列可以用于高能效的神经网络推理和训练运算,与基于cmos的冯诺依曼架构相比,忆阻神经形态计算作为一种新的计算架构,具有提高计算效率和降低功耗的潜力。

3、测试基于忆阻器的神经网络芯片的重要步骤之一是调制阻变存储器阵列中每个忆阻单元的电导值。例如,泰克4200系参数分析仪是一种测试忆阻器器件的常规测试设备。然而,由于忆阻器存储阵列往往包含成千上万个忆阻器存储单元,而参数分析仪的电压电流测试资源通道远远小于忆阻阵列所引出来的地址管脚数量,如果通过线缆在地址管脚间来回切换,要想遍历并调制整个忆阻阵列的所有存储单元,操作复杂费时费力。

技术实现思路

1、本技术的目的在于提供一种忆阻阵列的测试系统及其测试方法及计算机可读存储介质,能够实现忆阻阵列自动化和快速测试的需求。

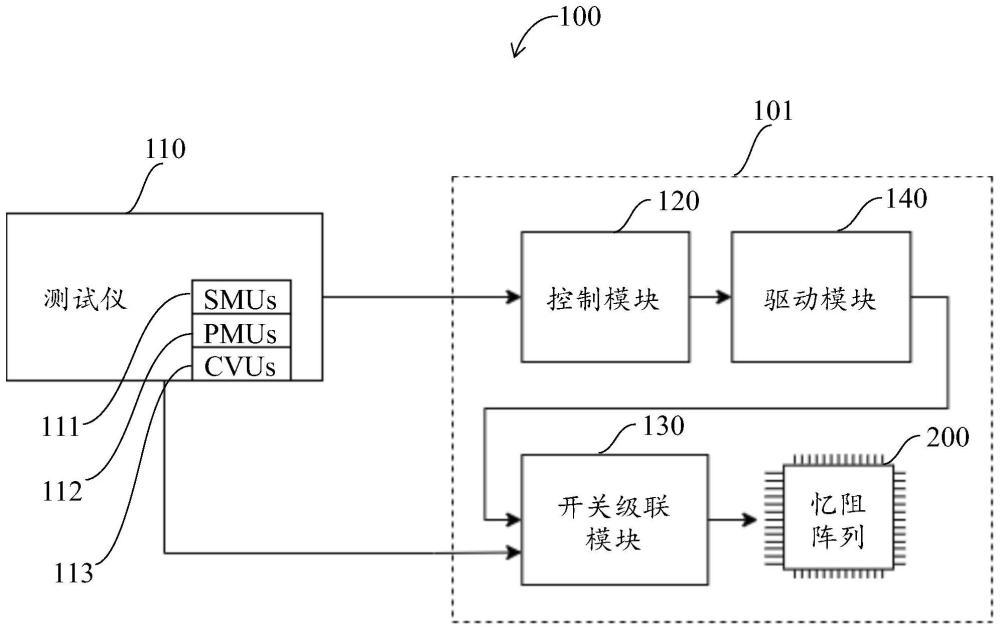

2、本技术的一个方面提供一种忆阻阵列的测试系统。所述测试系统包括测试仪、控制模块及开关级联模块,所述测试仪用于为待测的忆阻阵列提供激励源和测量功能,所述测试仪与所述控制模块通讯连接,所述忆阻阵列包括呈矩阵排布的多个存储单元及多个地址管脚,每一个存储单元具有对应的地址管脚,所述测试仪具有多个资源通道,所述测试仪的所述资源通道的数量少于所述忆阻阵列的所述地址管脚的数量,所述测试仪中的至少部分资源通道通过所述开关级联模块连接到所述忆阻阵列的所述多个地址管脚,所述控制模块用于对所述开关级联模块进行控制,以将所述测试仪的至少部分资源通道选通至所述忆阻阵列中待测存储单元的对应地址管脚。

3、进一步地,所述测试系统还包括驱动模块,所述驱动模块与所述控制模块通讯连接,用于为所述开关级联模块提供驱动电流。

4、进一步地,所述开关级联模块包括第一开关模块及与所述第一开关模块级联的第二开关模块,所述第一开关模块连接所述测试仪的至少部分资源通道,所述第二开关模块连接到所述忆阻阵列的所述多个地址管脚,其中,所述控制模块用于对所述第一开关模块和所述第二开关模块进行控制,以选通所述忆阻阵列中待测存储单元的地址管脚,并将所述忆阻阵列中其他存储单元的地址管脚接地。

5、进一步地,所述第一开关模块具有多个第一接线端和多个第一地址接线端,所述第二开关模块具有多个第二地址接线端、多个接地端及多个第三地址接线端,其中,所述多个第一接线端分别对应连接所述测试仪的至少多个资源通道,所述多个第一地址接线端分别与所述多个第二地址接线端对应连接,所述多个接地端分别连接至地,所述第三地址接线端分别对应连接至所述忆阻阵列的所述多个地址管脚。

6、进一步地,所述多个资源通道包括多种类型,所述开关级联模块还包括第三开关模块,所述第一开关模块与所述第三开关模块级联,所述第一开关模块通过所述第三开关模块连接所述测试仪的多种类型的资源通道,其中,所述控制模块用于对所述第三开关模块进行控制以选择至少一种类型的资源通道与所述忆阻阵列连接。

7、进一步地,所述第三开关模块包括多个切换端及多个第二接线端,所述多个切换端分别对应连接所述测试仪的所述多种类型的资源通道,所述多个第二接线端分别与所述多个第一接线端对应连接。

8、进一步地,所述多个地址管脚包括多个字线管脚、多个源线管脚以及多个位线管脚,所述忆阻阵列中的每一个存储单元具有对应的字线管脚、源线管脚及位线管脚,其中,所述控制模块用于控制选通所述待测存储单元对应的所述字线管脚、所述源线管脚及所述位线管脚。

9、进一步地,所述测试仪包括至少一种类型的资源通道,所述至少一种类型的资源通道包括smu资源通道、pmu资源通道和/或cvu资源通道。

10、本技术的另一个方面提供一种忆阻阵列的测试方法,所述忆阻阵列包括呈矩阵排布的多个存储单元及多个地址管脚,每一个存储单元具有对应的地址管脚。所述测试方法包括:读取测试仪下发的忆阻阵列中待测存储单元的地址信息,其中,所述测试仪具有多个资源通道,所述忆阻阵列具有多个地址管脚,所述测试仪的多个资源通道的数量少于所述待测忆阻阵列的所述多个地址管脚的数量,所述测试仪中的至少部分资源通道通过开关级联模块连接到所述忆阻阵列的所述多个地址管脚;响应于所述地址信息,控制所述开关级联模块,以将所述测试仪的至少部分资源通道选通至所述忆阻阵列中所述待测存储单元的对应地址管脚;及由所述测试仪通过所述至少部分资源通道向所述待测存储单元的地址管脚提供激励和测量。

11、进一步地,所述开关级联模块包括第一开关模块及与所述第一开关模块级联的第二开关模块,所述第一开关模块连接所述测试仪的至少部分资源通道,所述第二开关模块连接到所述忆阻阵列的所述多个地址管脚,所述控制所述开关级联模块,以将所述测试仪的至少部分资源通道选通至所述忆阻阵列中所述待测存储单元的对应地址管脚包括:对所述第一开关模块和所述第二开关模块进行控制,以选通所述忆阻阵列中所述待测存储单元的地址管脚,并将所述忆阻阵列中其他存储单元的地址管脚接地。

12、进一步地,所述第一开关模块具有多个第一接线端和多个第一地址接线端,所述第二开关模块具有多个第二地址接线端、多个接地端及多个第三地址接线端,其中,所述多个第一接线端分别对应连接至所述测试仪的至少多个资源通道,所述多个第一地址接线端分别与所述多个第二地址接线端对应连接,所述多个接地端分别连接至地,所述第三地址接线端分别对应连接至所述忆阻阵列的所述多个地址管脚,所述对所述第一开关模块和所述第二开关模块进行控制,以选通所述忆阻阵列中所述待测存储单元的地址管脚,并将所述忆阻阵列中其他存储单元的地址管脚接地包括:控制所述多个第一接线端分别与所述待测存储单元的地址管脚相对应的第一地址接线端对应连通;控制与所述待测存储单元的地址管脚相对应的第三地址接线端分别与所述第二地址接线端对应连通;及控制与其他存储单元的地址管脚相对应的第三地址接线端分别与所述接地端连通。

13、进一步地,所述多个资源通道包括多种类型,所述开关级联模块还包括第三开关模块,所述第一开关模块与所述第三开关模块级联,所述第一开关模块通过所述第三开关模块连接所述测试仪的多种类型的资源通道,所述测试方法还包括:对所述第三开关模块进行控制以选择至少一种类型的资源通道与所述忆阻阵列连接。

14、进一步地,所述第三开关模块包括多个切换端及多个第二接线端,所述多个切换端分别对应连接所述测试仪的所述多种类型的资源通道,所述多个第二接线端分别与所述多个第一接线端对应连接,所述对所述第三开关模块进行控制以选择至少一种类型的资源通道与所述忆阻阵列连接包括:控制所述多个第二接线端分别与要选择类型的资源通道相对应的切换端对应连通。

15、进一步地,所述测试方法还包括:在完成一组待测存储单元的测试后,读取所述测试仪下发的下一组待测存储单元的地址信息;及响应于所述下一组待测存储单元的地址信息,控制所述开关级联模块,以将所述测试仪的至少部分资源通道切换选通至所述下一组待测存储单元的对应地址管脚,直到遍历所述忆阻阵列中的所有存储单元。

16、本技术的又一个方面提供一种计算机可读存储介质,其上存储有程序,所述程序被处理器执行时,实现如上所述的忆阻阵列的测试方法。

17、本技术一个或多个实施例的测试系统及其测试方法及计算机可读存储介质,能够规避测试仪有限的资源通道数量,利用开关级联模块可以用测试仪有限的资源通道去覆盖更大规模的忆阻阵列,可以达到忆阻器自动化测试且快速测试的需求。

18、另外,本技术一个或多个实施例的测试系统及其测试方法及计算机可读存储介质不用人为地去切换忆阻阵列的地址管脚和测试仪的资源通道之间的连线,加快测试效率。

本文地址:https://www.jishuxx.com/zhuanli/20240731/182958.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 YYfuon@163.com 举报,一经查实,本站将立刻删除。

下一篇

返回列表