一种FPGA内可配置SRAM的写入电路及方法与流程

- 国知局

- 2024-07-31 19:31:07

本发明涉及集成电路,更具体地涉及一种fpga内可配置sram的写入技术。

背景技术:

1、本部分旨在为权利要求书中陈述的本技术的实施方式提供背景或上下文。此处的描述不因为包括在本部分中就承认是已被公开的现有技术。

2、随着集成电路先进制造工艺特征尺寸的不断减小,金属氧化物半导体场效应晶体管(mos)器件的偏差尤其是局部偏差(local variation)变得越来越大,给静态随机访问存储器(sram)的可靠性带来极大的影响。sram的读写过程是n型驱动管(nmos管)和p型驱动管(pmos管)驱动能力的竞争过程,当nmos管和pmos管由于工艺偏差而造成驱动能力的差别较大时,就可能导致sram的读写失败。本文主要描述提高sram写可靠性的实现方法。

3、现场可编程门阵列(fpga)的主流技术有基于反熔丝、基于sram和基于快闪(flash)三种。相对于反熔丝和基于flash的fpga,sram型fpga具有强大的性能优势和设计灵活性,对飞控和航电应用具有巨大的吸引力。目前占据市场份额最大的fpga厂商xilinx和altera的绝大部分产品都是基于sram的,欧美等国家的航空航天机构也把sram型fpga作为核心电子元器件。

4、sram是sram型fpga实现功能的重要组成元件,用户需将要实现的逻辑功能以码流的形式下载到fpga的可编程sram中,如果可编程sram的写入失败,则可能导致用户无法实现预想的功能,芯片失效。

5、增强sram写可靠性方法主要有三种,sram使用工艺偏差较小的器件、提高sram的字线(wordline,即sram的地址线)电压和增强驱动管的能力。采用器件偏差较小的器件类型构成sram可靠性提高明显,缺点是带来更大的面积或者静态漏电。提高sram的wordline电压需要设计一个额外的稳压器,设计复杂并且开销大。增强驱动管的能力是常用设计手段,在写sram的过程中由nmos构成的下拉管起主要作用,但随着芯片上条件(工艺角、电压与温度,即pvt)的变化,在边界情况下增加nmos管的尺寸也会有写sram失败的情况发生。

6、目前fpga厂商xilinx和altera在其先进工艺产品上也加强了sram的写可靠性,用于应对越来越大的工艺偏差以及更低的工作电压。其主要手段是抬高写过程中sram的wordline电压,这样做会存在以下问题:增加设计成本,提高wordline电压需要独立做一个稳压器,需要投入人力资源开发模拟电路,增加设计复杂度的同时也增加了芯片面积,提高整体的设计成本。

技术实现思路

1、本发明的目的在于提供一种fpga内可配置sram的写入电路,在设计成本增加较低的情况下,提高了sram的写可靠性。

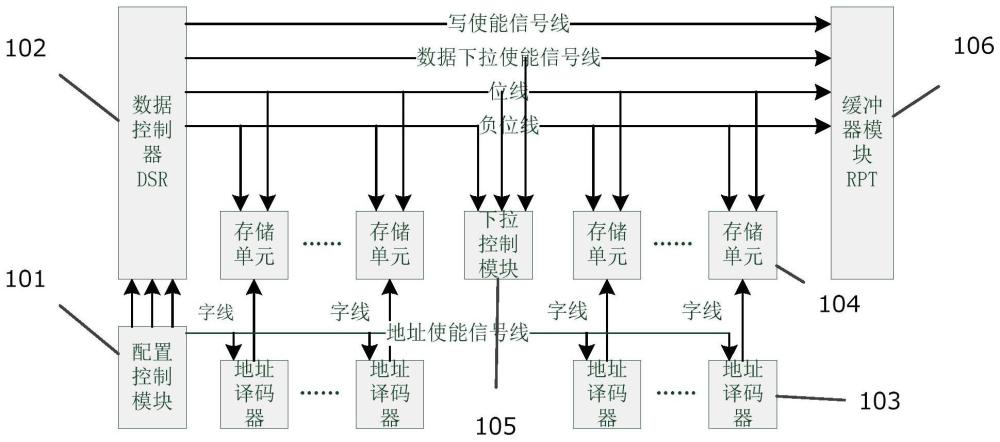

2、在本发明中,本发明提供了一种fpga内可配置sram的写入电路,包括配置控制模块、数据控制器、多个地址译码器、配置存储单元阵列、下拉控制模块、以及缓冲器模块,其中:

3、所述配置控制模块连接所述数据控制器;

4、所述数据控制器分别通过多对位线和负位线连接所述配置存储单元阵列,每对位线和负位线连接所述配置存储单元阵列中的一列存储单元;

5、所述数据控制器通过所述多对位线和负位线、写使能信号线和数据下拉使能信号线连接所述缓冲器模块,并通过所述多对位线和负位线和所述数据下拉使能信号线连接所述下拉控制模块,其中所述下拉控制模块用于接收所述位线或负位线上的“0”信号,在所述数据下拉使能信号的控制下打开下拉“0”信号对应的位线或负位线的n型驱动管开关,关闭所述位线或负位线中的另一个的n型驱动管开关;

6、所述配置控制模块通过地址使能信号线连接所述多个地址译码器中的每一个,所述配置存储单元阵列中的每一行存储单元与所述多个地址译码器之间一一对应并通过字线对应连接。

7、在一个优选例中,所述下拉控制模块设置在所述配置存储单元阵列中的居中位置。

8、在一个优选例中,所述下拉控制模块设置在所述配置存储单元阵列中远离位线起点的边界位置。

9、在一个优选例中,一行所述存储单元对应一个或多个所述下拉控制模块。

10、在一个优选例中,所述下拉控制模块的面积和功耗小于所述数据控制器。

11、在一个优选例中,包括配置控制模块、数据控制器、多个地址译码器、配置存储单元阵列、下拉控制模块、和缓冲器模块,其中:

12、通过所述配置控制模块发送一帧数据,然后发送写使能信号;

13、通过所述数据控制器将所述数据传递到连接所述配置存储单元阵列中的一列存储单元的位线上,根据数据值,位线或负位线被所述数据控制器下拉为“0”;

14、在“0”信号建立完成后,通过所述数据控制器向所述缓冲器模块发送数据下拉使能信号;

15、通过所述下拉控制模块根据所述位线或负位线上的“0”信号,在所述数据下拉使能信号的控制下,将下拉“0”信号对应的位线或负位线的n型驱动管开关打开,将所述位线或负位线中的另一个的n型驱动管开关关闭;

16、通过所述配置控制模块发送的地址使能信号,开启字线,启动所述多个地址译码器;

17、在所述写使能信号和所述地址使能信号控制下,将存储单元的值改写为所述数据值,完成静态随机访问存储器的写入操作。

18、在一个优选例中,所述数据值包括“0”;

19、当配置控制模块发送数据“0”时,位线被数据控制器下拉为“0”,所述数据下拉使能信号需要等待位线上的“0”完全建立好后开启;

20、所述下拉控制模块根据所述位线上的“0”信号,在所述数据下拉使能信号的控制下,将下拉位线的n型驱动管开关打开,将负位线的n型驱动管开关关闭。

21、在一个优选例中,所述数据值包括“1”;

22、当配置控制模块发送数据“1”时,负位线被数据控制器下拉为“0”,所述数据下拉使能信号需要等待负位线上的“0”完全建立好后开启;

23、所述下拉控制模块根据所述负位线上的“0”信号,在所述数据下拉使能信号的控制下,将下拉负位线的n型驱动管开关打开,将位线的n型驱动管开关关闭。

24、在一个优选例中,所述写使能信号在一帧数据全部发送完成后发出;所述数据下拉使能信号需要等待n个周期结束直至“0”信号完全建立好后开启,n取决于“0”信号的建立时间。

25、在一个优选例中,在所述下拉控制模块接收到所述位线或负位线上的“0”信号,在所述数据下拉使能信号的控制下打开下拉“0”信号对应的位线或负位线的n型驱动管开关,关闭位线或负位线中的另一个的n型驱动管开关时,写通路上的驱动包括所述数据控制器和所述下拉控制模块。

26、本发明实施方式与现有技术相比,主要区别及其效果在于:

27、本公开采用多组下拉控制模块组合并且利用sram位线(bitline,即sram的数据线)反馈的方式提高sram写的驱动能力,从而提高sram的写可靠性,尤其是提高sram在不同工艺偏差和较低电压下的写可靠性。

28、进一步的,该实现方法电路面积小,实现灵活,可根据不同的bitline负载插入多组模块。这种设计方法可以大大降低设计成本和面积,提高产品竞争力。

29、应理解,在本发明范围内中,本发明的上述各技术特征和在下文(如实施例)中具体描述的各技术特征之间都可以互相组合,从而构成新的或优选的技术方案。限于篇幅,在此不再一一累述。

本文地址:https://www.jishuxx.com/zhuanli/20240731/182880.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 YYfuon@163.com 举报,一经查实,本站将立刻删除。

下一篇

返回列表