一种全光存储器阵列及方法与流程

- 国知局

- 2024-07-31 19:36:19

本发明属于全光信息计算领域,尤其涉及一种全光存储器阵列及方法。

背景技术:

1、全光计算和全光通信是未来取代电子计算的下一代信息技术,是未来信息技术的主要发展方向,也是打破技术封锁和技术壁垒的关键技术。由于光的并行性和高速性等物理性质,有可能开发远远超过电子技术的高性能信息处理系统。因此光计算已成为引人注目的研究领域。而且光信号具有非常强的抗干扰性和保密性;其无阻抗性和无容抗性无需在光路中加入电阻、电容等器件进行电路匹配,所以光路设计比电路设计简单。因而全光计算将成为未来全光信息网络的支撑技术,使用全光信号处理技术的全光网络和全光计算机将是未来信息技术发展的主流趋势。而全光存储器又是全光计算的关键功能,和电子领域中的存储器在电子领域的地位一样,是形成全光计算时序逻辑数据计算、存储的核心技术,是所有全光计算和全光信息交换绕不开的核心技术点。及早进行全光存储器的研发和布局,有利于在未来全光技术方向上的战略布局,提升未来在全光信息技术方面的竞争力。它可以用于实现全光信号的存储、计算、交换、数据编码、奇偶效验、转发等。全光存储器阵列是在基本全光逻辑门基础上组合而成的进行信息存储和计算的关键器件,而现有的存储器阵列,技术大部分是电子半导体领域的,一小部分是基于光电转换的光盘型存储器。

2、现有的存储器阵列大部分是电子半导体领域的,无法实现光信号的存储、计算、交换、数据编码、奇偶效验、转发等;一小部分光盘型光存储器是基于光电、电光转换的,要进行信息的存储、计算、交换、数据编码、奇偶效验、转发等处理须先进行光电转换,在电域完成处理后再进行电光转换;因存在光电、电光转换,因而不便于光学领域的高密度、大规模集成。

技术实现思路

1、为了解决上述背景技术中存在的至少一项技术问题,本发明的提供一种全光存储器阵列及方法,其采用多个存储单元串联组成全光存储器阵列,提高了存储数据的精度和范围,存储同样数量的信息,节省数据总线条数和地址总线n倍,提高了数据总线复用效率;提高了数据线使用灵活度;数据线可根据需要读、写、清零结合地址总线进行灵活控制。

2、为了实现上述目的,本发明采用如下技术方案:

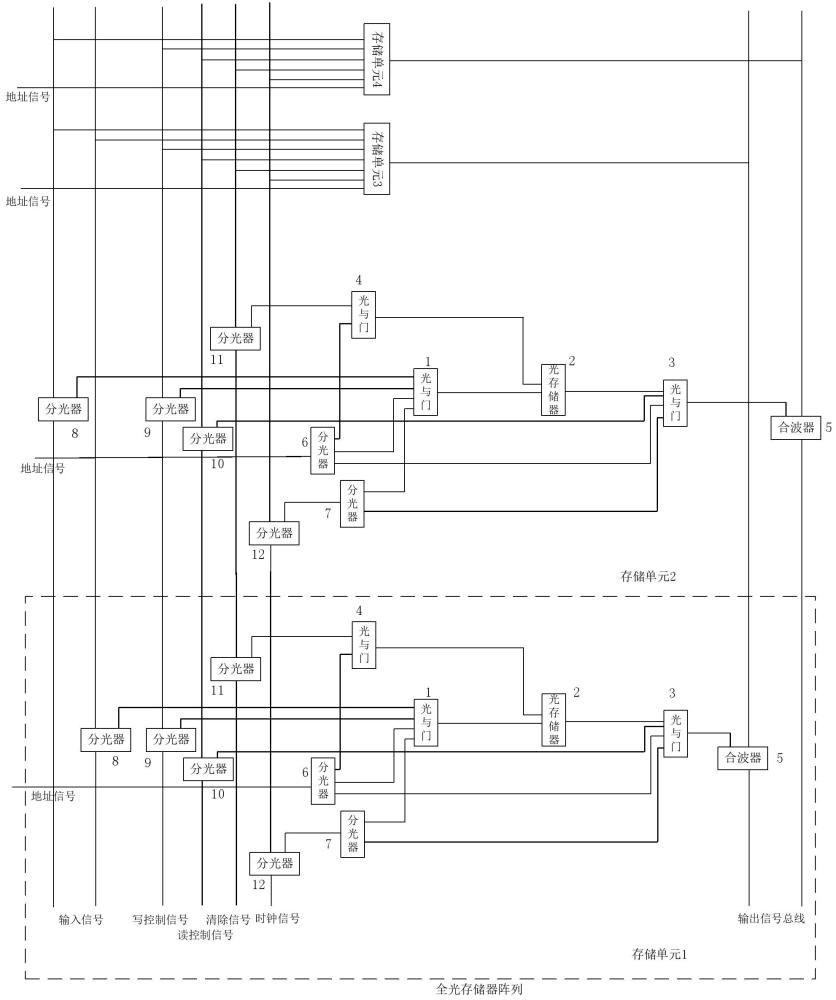

3、第一方面,本发明提供了一种全光存储器阵列,包括多个存储单元,存储单元的一端连接输入信号、写控制信号、清除信号和时钟信号,另一端连接输出信号总线,多个存储单元串联组成全光存储器阵列;所述存储单元包括输入信号线路、写控信号线路、清除信号线路、时钟信号线路和地址信号线路;

4、所述输入信号线路包括依次串联的分光器八、光与门一、光存储器二、光与门三和合波器五;

5、写控信号线路包括依次串联的分光器九、光与门一、光存储器二、光与门三和合波器五;

6、清除信号线路包括依次串联的分光器十一、光与门四、光存储器二和合波器五;

7、读控制信号线路包括依次串联的分光器十、光与门三和合波器五;

8、时钟信号线路包括依次串联的分光器十二、分光器七、光与门一和光与门三,分光器七具有两个输出端,第一输出端连接光与门一,第二输出端连接光与门三;

9、所述地址信号线路包括依次串联的分光器六、光与门一、光与门三和光与门四;所述分光器六具有三个输出端,第一输出端连接光与门四,第二输出端连接光与门一,第三输出端连接光与门三。

10、进一步的,所述光与门一具有四个输入端口,第一输入端口连接分光器八,第二输入端口连接分光器九,第三输入端口连接分光器六,第四输入端口连接分光器七。

11、进一步的,所述光与门四具有两个输入端口,第一输入端口连接分光器十一,第二输入端口连接分光器六。

12、进一步的,所述光存储器二具有两个输入端口,第一输入端口连接光与门四,第二输入端口连接光与门一。

13、进一步的,所述光与门三具有四个输入端口,第一输入端口连接光存储器二,第二输入端口连接分光器十,第三输入端口连接分光器六,第四输入端口连接分光器七。

14、第二方面,本发明提供了一种全光存储器阵列的工作方法,包括:

15、当写控制信号、时钟信号、地址信号同时为“1”时,光与门一输出信号与数据总线输入信号相同,实现信号选通输入;

16、写控制信号、时钟信号、地址信号中任一信号为“0”时,光与门一输出为零,禁止信号输入;光与门一的输出信号输出到光存储器二,光存储器二输出到光与门三;

17、当读控制信号、时钟信号、地址信号同时为“1”时,光与门三的输出与光存储器二的输出信号相同,实现信号选通输出到合波器,合波器五的输出作为输出信号;

18、当读控制信号、时钟信号、地址信号任一为“0”时,光与门三输出信号为零,没有信号输出,因而合波器五没有输出。整个存储单元实现地址信号、时钟信号、读写控制信号的选择输入输出。

19、本发明的有益效果是:

20、1.本发明采用多个存储单元串联组成全光存储器阵列,提高了存储数据的精度和范围,以整数为例,1位数据存储数值范围0-1(2^1),2位数据存储为0-3(2^2),n位则存储范围为0—2^n-1;

21、2.本发明存储同样数量的信息,节省数据总线条数和地址总线n倍(n为数据位数),提高了数据总线复用效率:数据总线和地址总线只需要总存储位数/n条;

22、3.本发明控制总线读、写、清零只需三条,省了3倍存储总位数,不使用存储阵列式,每个存储单元都需要读、写、清零控制线各一条。

23、4.本发明提高了数据线使用灵活度。数据线可根据需要读、写、清零结合地址总线进行灵活控制。

24、本发明附加方面的优点将在下面的描述中部分给出,部分将从下面的描述中变得明显,或通过本发明的实践了解到。

技术特征:1.一种全光存储器阵列,其特征在于,包括多个存储单元,存储单元的一端连接输入信号、写控制信号、清楚信号和时钟信号,另一端连接输出信号总线,多个存储单元串联组成全光存储器阵列;所述存储单元包括输入信号线路、写控信号线路、清除信号线路、时钟信号线路、读控制信号线路和地址信号线路;

2.如权利要求1所述的全光存储器阵列,其特征在于,所述光与门一具有四个输入端口,第一输入端口连接分光器八,第二输入端口连接分光器九,第三输入端口连接分光器六,第四输入端口连接分光器七。

3.如权利要求1所述的全光存储器阵列,其特征在于,所述光与门四具有两个输入端口,第一输入端口连接分光器十一,第二输入端口连接分光器六。

4.如权利要求1所述的全光存储器阵列,其特征在于,所述光存储器二具有两个输入端口,第一输入端口连接光与门四,第二输入端口连接光与门一。

5.如权利要求1所述的全光存储器阵列,其特征在于,所述光与门三具有四个输入端口,第一输入端口连接光存储器二,第二输入端口连接分光器十,第三输入端口连接分光器六,第四输入端口连接分光器七。

6.一种全光存储器阵列的工作方法,其特征在于,包括:

技术总结本发明属于全光信息计算领域,提供了一种全光存储器阵列及方法,包括多个存储单元,存储单元的一端连接输入信号、写控制信号、清楚信号和时钟信号,另一端连接输出信号总线,多个存储单元串联组成全光存储器阵列;所述存储单元包括输入信号线路、写控信号线路、清除信号线路、时钟信号线路和地址信号线路;采用多个存储单元串联组成全光存储器阵列,提高了存储数据的精度和范围,存储同样数量的信息,节省数据总线条数和地址总线N倍,提高了数据总线复用效率;数据线可根据需要读、写、清零结合地址总线进行灵活控制。技术研发人员:邢露文,邢培宏,刘平,邢建昌,邢转义受保护的技术使用者:山东全寻智能科技有限公司技术研发日:技术公布日:2024/1/25本文地址:https://www.jishuxx.com/zhuanli/20240731/183151.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 YYfuon@163.com 举报,一经查实,本站将立刻删除。