基于反相器链跨阻放大器的动态随机存储器单元读出电路

- 国知局

- 2024-07-31 19:36:45

本发明涉及一种基于反相器链跨阻放大器的2t动态随机存储器单元读出电路,属于集成电路领域。

背景技术:

1、目前大多数主流的dram都采用1t1c的器件,这种器件具有体积小巧,集成度高等特点。但因为其自身条件限制,譬如存储电容相对bl寄生电容较小;读取过程中会对存储电容存储电荷会发生破坏;存储的电荷会通过晶体管漏电等,需要搭配相应的读出电路和频繁的刷新才能正常使用。

2、对于2t1c存储单元组成的器件相较于1t1c器件的最大区别是将写入管与读出管分开,使得读出时无需直接读取存储电容上的电荷,转而通过电容分压来进行读取。因为读取时不涉及电荷转移,因此可以达到非破坏性读出。此外,基于2t1c的特殊结构,存储电荷的能力更强。这就使得存储整列无需频繁刷新。大大节约了功耗。

3、但相较于传统1t1c器件来说,2t1c器件读出方式发生了很大改变。1t1c器件因为是通过感应电荷来进行读取,因此输出的是电压信号,可以直接为后续的多路复用器或其他模块所用。而2t1c器件是通过改变读出管的栅压来进行读出的,这就使得最后得到的信号以电流形式表现,无法直接应用到后续模块。因此需要提出一种读出电路来解决电流域向电压域转化的问题。

技术实现思路

1、为了解决上述技术问题,本发明提供了基于反相器链跨阻放大器的2t动态随机存储器单元读出电路,以达到2t1c动态随机存储器单元实现高速、高精度读出的目的。

2、本发明电路采用的技术方案如下:

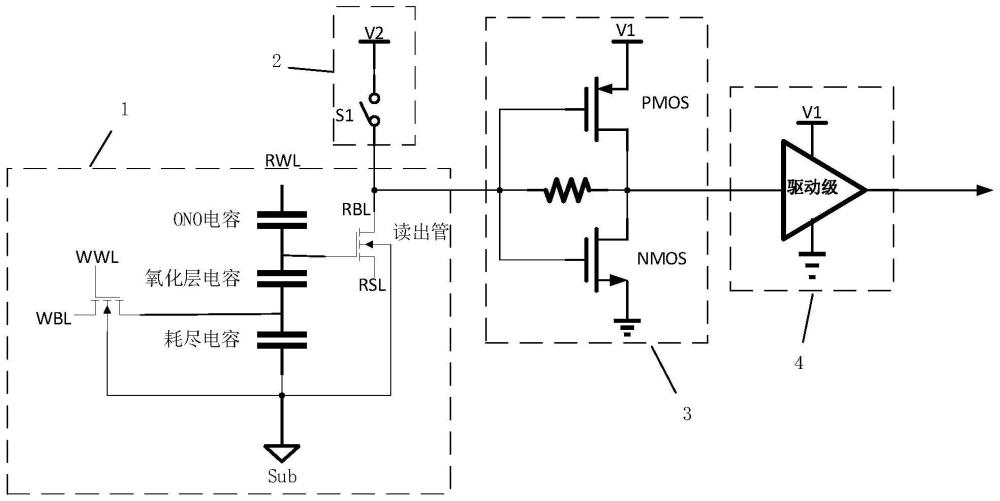

3、基于反相器链跨阻放大器的动态随机存储器单元读出电路,包括2t动态随机存储单元、开关、反相器链跨阻放大器和驱动级;所述2t动态随机存储单元包括mos-c信号收集区、mosfet信号读出区与mosfet信号写入区,所述mosfet信号写入区与mos-c信号收集区相连,所述mosfet信号读出区连接反相器链跨阻放大器输入端;所述反相器链跨阻放大器的输出端与所述驱动级的输入端连接;所述驱动级的输出端输出数字信号;所述开关的一端连接所述反相器链跨阻放大器的输入端。

4、进一步地,所述反相器链跨阻放大器包括由n级反相器级联组成的开环前馈放大器以及电阻构成的反馈网络,其中n为奇数。

5、进一步地,每级反相器包括一对串联的p型掺杂mosfet晶体管和n型掺杂mosfet晶体管;p型掺杂mosfet晶体管的源极接第一电压v1,n型掺杂mosfet晶体管的源极接零电势;p型掺杂mosfet晶体管和n型掺杂mosfet晶体管的栅极相连作为输入端,漏极相连作为输出端,且两个晶体管各自的宽长比为空穴与电子迁移率之比的倒数。

6、进一步地,所述mos-c信号收集区为复合介质栅结构,其衬底无源漏注入,其浮栅与所述mosfet信号读出区的控制栅端相连,所述mosfet信号读出区为复合介质栅结构,其浮栅与所述mos-c信号收集区的浮栅相连。

7、进一步地,所述反相器链跨阻放大器和驱动级均与所述第一电压v1连接。

8、进一步地,所述开关的另一端连接第二电压v2且v2=0.5*v1。

9、进一步地,所述n型掺杂mosfet晶体管的阈值电压大于第二电压v2,且所述p型掺杂mosfet晶体管的阈值电压的绝对值小于第二电压v2;或者增大pmos管的宽长比为nmos管的宽长比的数倍。

10、本发明还提供上述基于反相器链跨阻放大器的动态随机存储器单元读出电路的工作方法,所述2t动态随机存储单元包括六个端口:mosfet信号写入区的漏端wbl、mosfet信号写入区的栅端wwl、mos-c信号收集区的栅端rwl、mosfet信号读出区的漏端rbl、mosfet信号读出区的源端rsl和衬底sub;在读出模式中,栅端wwl接负压使mosfet信号写入区关闭,漏端wbl浮空,栅端rwl接正压供串联电容分压,衬底sub为负压,以形成耗尽电容。

11、进一步地,所述反相器链跨阻放大器包括由n级反相器级联组成的开环前馈放大器以及电阻构成的反馈网络,其中n为奇数;每级反相器包括一对串联的p型掺杂mosfet晶体管和n型掺杂mosfet晶体管;p型掺杂mosfet晶体管的源极接第一电压v1,n型掺杂mosfet晶体管的源极接零电势,p型掺杂mosfet晶体管和n型掺杂mosfet晶体管的栅极相连作为输入端,漏极相连作为输出端,且两个晶体管各自的宽长比为空穴与电子迁移率之比的倒数;所述反相器链跨阻放大器和驱动级均与所述第一电压v1连接;所述开关的另一端连接所述第二电压v2且v2=0.5*v1;其中,n型掺杂mosfet晶体管的阈值电压大于第二电压v2,且p型掺杂mosfet晶体管的阈值电压的绝对值小于第二电压v2,当无法调节阈值满足上述条件时,则增大pmos管的宽长比为nmos管的宽长比的数倍。

12、本发明的工作原理/过程如下:

13、基于反相器链跨阻放大器的2t动态随机存储器单元读出电路有两种工作状态,即读出状态与待机状态,待机与读出状态交替进行。在读出状态时,开关s1断开;在待机状态时,开关s1闭合。待机状态相较于读出状态,在器件层面的区别是rwl端是否施加电压。读出时,rwl端为正压与衬底负压相耦合,其作用是在ono电容(复合介质栅结构中浮栅与控制栅之间的介质层)、氧化层(浮栅与衬底间介质)电容和耗尽电容(控制栅端施加电压,衬底形成耗尽层作为电容)的分压。施加的电压满足当耗尽电容区域被充进电子后,读出管控制栅端电压根据串联电容分压产生的电势vrg与读出管源端电势vrsl之差小于读出管的阈值电压vth。释放电子或充入空穴后满足(vrg-vrsl)大于等于读出管阈值电压。在读出模式时,反相器链跨阻放大器输入端接第二电压v2(v2=0.5*v1)。若2t动态随机存储器单元存储的权值为“1”,即vrg-vrsl<vth,则2t动态随机存储器单元中n型mosfet信号读出晶体管关闭,其源极与漏极所在支路电流近似为0。由于反相器链跨阻放大器为闭环连接,其反馈电阻没有电流流过,因而反相器链跨阻放大器的输出端为第二电压v2,则反相器链中各级反相器级联处均为中间电平附近电势,各级反相器中pmos与nmos处于饱和工作区的直流工作电平,驱动级需满足输入为中间电势v2附近时输出高电平v1,输入为v1电势附近时输出0。因此可以设置驱动级nmos阈值电压大于v2,pmos阈值电压的绝对值小于v2,或者增大pmos管的宽长比为nmos的数倍(5-10倍),也可实现驱动级的翻转。此时驱动级输出高电平v1。若2t动态随机存储器单元存储的权值为“0”,即vrg-vrsl≥vth,则2t动态随机存储器单元中n型mosfet信号读出晶体管立刻导通,其源极与漏极所在支路出现微安级电流,电流方向为从漏极到源极。在这个时刻,反相器链所有晶体管处于饱和工作状态,具备高增益,且反相器链中不存在大电容,瞬态响应速度快,反相器链跨阻放大器中利用其高增益、高速的前馈放大器对该电流迅速响应,利用反馈电阻对其进行放大,使得跨阻放大器输出电平迅速从v2上升到v1,实现了快速检测2t动态随机存储器单元的权值并完成逻辑翻转的功能,而具备反相功能的驱动级的输出电平则由v1电平快速下降到0v,完成读出。

14、相比现有技术,本发明具有以下有益效果:

15、(1)本发明电路中的反相器链跨阻放大器结构能够快速检测2t动态随机存储器单元的权值并完成逻辑翻转,以此实现对2t动态随机存储器实现高速、高精度的读出。

16、(2)本发明提出的基于反相器链跨阻放大器的2t动态随机存储器单元读出电路,在避免常规稳压器结构的设计,解决了可能出现的环路稳定性问题的基础上,规避了开环结构放大器的设计,利用闭环接法的反相器链跨阻放大器替代了上述现有方案中的开环运算放大器与比较器的级联结构。由于是闭环结构且前馈放大器为反相器链结构,反相器链跨阻放大器在复位阶段中易于确定线性放大工作状态的直流工作电平,由于不存在任何电流流经反馈电阻,其输出端直流工作电平跟随输入端直流工作电平复位到电源电平的二分之一,因而在读出阶段开启时,反相器链各个节点均处于中间电平处,不会存在偏移线性工作区间的问题,反相器链所有晶体管处于饱和工作状态具备高增益,且反相器链中不存在大电容,瞬态响应速度快;闭环结构另一个优点是对输入端高频噪声不敏感,有效的规避输入端高频噪声经过增益影响输出端工作电平的隐患,因而电路具备高速、高增益。综上所述,本发明的电路相较于现有技术,规避了放大器直流工作电平不处于线性放大区间的问题,且不易受到输入端高频噪声的干扰,可以对如复合介质栅结构mos-c双晶体管动态随机存储器等实现高速、高精度的读出。

17、(3)本发明的读出电路可以用在2t动态随机存储器上,用于存储领域,具有良好的应用前景。

本文地址:https://www.jishuxx.com/zhuanli/20240731/183208.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 YYfuon@163.com 举报,一经查实,本站将立刻删除。

下一篇

返回列表