用于校准半导体装置的阻抗的基于定时的仲裁方法和设备与流程

- 国知局

- 2024-07-31 19:32:15

本申请涉及用于校准半导体装置的阻抗的基于定时的仲裁方法和设备。

背景技术:

1、高数据可靠性、高速存储器存取和减小的芯片大小是半导体存储器所需的特征。近年来,已致力于进一步增大存储器存取的速度。

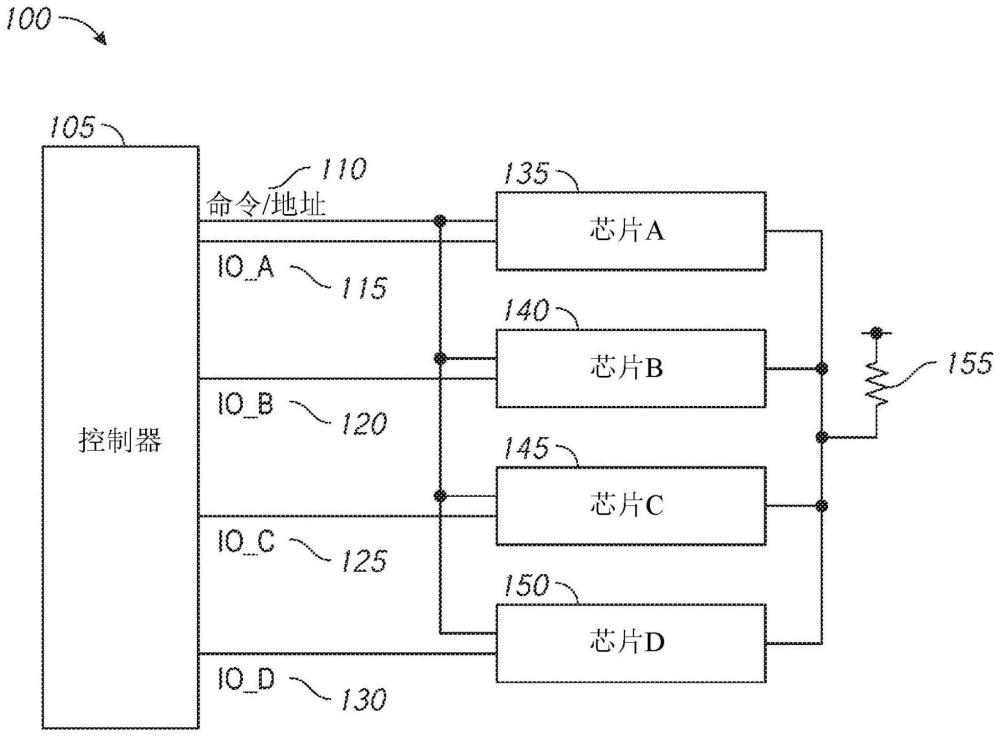

2、在用于半导体存储器装置的常规的外围电路中,举例来说,衬垫和数据输入/输出电路以跨越层的对应的方式布置。举例来说,半导体存储器装置可包含数据输入/输出电路。为了实现高速传输,应该控制数据输入/输出电路的阻抗。为了控制阻抗,可以耦合外部电阻,例如,zq电阻器。包含多个芯片的半导体存储器装置通常配备有一个外部zq电阻器。当两个或大于两个两个芯片同时请求使用zq电阻器时,通常使用仲裁器电路来确定哪个芯片应该存取zq电阻器。相应地,一个芯片可以存取zq电阻器,且后续芯片可在已完成针对这一个芯片的zq校准之后存取zq电阻器。

3、举例来说,仲裁器电路可依赖于基于电压的仲裁方案来确定哪个芯片,主芯片或从芯片已发布zq校准请求。在基于电压的仲裁方案中,由主芯片发布的zq校准请求可具有强下拉,而由从芯片发布的zq校准请求可具有弱下拉。因此,可以经由zq衬垫电压确定zq电阻器的使用的各种状态。然而,具有多个芯片的芯片封装和/或低功率消耗类型的芯片封装可能无法通过基于电压的仲裁方案经由zq衬垫电压在多个状态之间进行有效地区分。

4、举例来说,一些近期的半导体装置(例如,低功率双数据速率同步dram),例如,低功率双数据速率4(lpddr4),采用基于时间的仲裁方案。在基于时间的仲裁方案之下,共享zq电阻器的每个芯片以唯一的时间延迟编程以形成主从层级。此基于时间的仲裁方案使得每个封装的半导体存储器装置中的任何数量的芯片能够使用zq电阻器,然而根据芯片的数量所需要的时间以指数方式增加。举例来说,包含共享单个zq电阻器的16个芯片的半导体存储器装置可能需要16个不同的延迟变化用于16个芯片。

5、因此,对于具有大量的芯片的半导体存储器装置来说在没有用于zq校准请求仲裁的延长时间的情况下要完成zq校准需要实施仲裁方案的仲裁电路。

技术实现思路

1、根据本发明的实施例的实例系统可包含电阻器;以及多个芯片。多个芯片中的每个芯片可包含:端子,其耦合到电阻器;以及校准电路,其经配置以至少部分地基于对于多个芯片的对应的芯片唯一的定时信息确定电阻器是否是可供使用的。多个芯片中的每个芯片的定时信息可具有多个芯片共用的固定持续时间。

2、根据本发明的实施例的实例设备可包含耦合在电源电压与端子之间的电阻器;以及芯片。芯片可包含:端子,其耦合到电阻器;以及校准电路,其经配置以至少部分地基于定时信息确定电阻器是否是可供使用的。芯片的定时信息可包含对于对应的芯片唯一的二进制代码。

3、根据本发明的实施例的实例方法可包含检测多个芯片之中的一个芯片中的端子处的电压。端子可以耦合到电阻器。多个芯片中的每个芯片可以耦合到电阻器。根据实施例的方法可进一步包含基于定时信息启用包含在芯片中的驱动器电路达一段持续时间。定时信息可以是对于多个芯片的其它芯片之中的芯片是唯一的并且具有多个芯片共用的固定持续时间。根据实施例的方法可进一步包含:基于定时信息上拉或下拉电压达一段持续时间;以及基于在上拉电压之后的电压确定电阻器是否是可供使用的。

4、根据本发明的实施例的另一实例方法可包含检测多个芯片之中的一个芯片中的端子处的电压。端子可以耦合到电阻器。多个芯片中的每个芯片可以耦合到电阻器。根据实施例的方法可进一步包含基于定时信息启用和停用包含在芯片中的驱动器电路达一段持续时间。定时信息可以是对于多个芯片的其它芯片之中的芯片唯一的。根据实施例的方法可进一步包含:响应于启用和停用驱动器电路相应地上拉和下拉电压达一段持续时间;以及基于在上拉电压之后的电压确定电阻器是否是可供使用的。定时信息可包含在定时信息中用信号发送启用和停用的对于多个芯片的其它芯片之中的芯片唯一的二进制代码。

技术特征:1.一种系统,其包括:

2.根据权利要求1所述的系统,其中所述多个芯片中的每个芯片的所述定时信息具有所述多个芯片共用的固定持续时间。

3.根据权利要求2所述的系统,其中所述多个芯片中的每个芯片的所述校准电路包括:

4.根据权利要求2所述的系统,其中所述多个芯片中的每个芯片的所述校准电路包括:

5.根据权利要求1所述的系统,其中所述多个芯片中的每个芯片中的所述校准电路包括仲裁器电路,且

6.根据权利要求1所述的系统,其中所述电阻器在所述多个芯片之间共享。

7.根据权利要求6所述的系统,其中所述驱动器电路是下拉电路。

8.根据权利要求6所述的系统,其中所述驱动器电路是上拉电路。

9.根据权利要求1所述的系统,其中所述多个芯片中的每个芯片的所述校准电路包括:

10.根据权利要求1所述的系统,其中所述多个芯片中的每个芯片的所述校准电路包括:

11.一种方法,其包括:

12.根据权利要求11所述的方法,其进一步包括基于所述定时信息上拉或下拉所述电压达所述持续时间;

13.根据权利要求11所述的方法,其中所述定时信息包括二进制代码,所述二进制代码被指派并用信号发送作为所述芯片唯一的定时模式。

14.根据权利要求13所述的方法,其中所述二进制代码选自具有预定数量的位的二进制代码的集合。

15.根据权利要求14所述的方法,其中经选择具有所述预定数量的位的所述二进制代码的集合中没有任何一者等于具有所述预定数量的位的预定的禁止的代码。

16.根据权利要求11所述的方法,其中至少部分地基于所述定时信息确定所述电阻器是否是可供使用的包括将所述端子处的所检测的电压与参考电压进行比较。

17.一种设备,其包括:

18.根据权利要求17所述的设备,其中所述校准电路包括:

19.根据权利要求17所述的设备,其中所述校准电路包括耦合到所述端子的驱动器电路,

20.根据权利要求17所述的设备,其中所述校准电路包括:

21.一种设备,其包括:

22.根据权利要求21所述的设备,其进一步包括校准控制电路,其耦合至所述驱动器电路,其中所述校准控制电路经配置以在所述电阻器可供用于所述校准操作时调节所述驱动器电路的阻抗。

23.根据权利要求21所述的设备,其中所述驱动器电路包括上拉电路和下拉电路。

24.根据权利要求23所述的设备,其中所述上拉电路包括在第一电源端子与节点之间并联耦合的第一多个晶体管,且所述下拉电路包括在第二电源端子与所述节点之间并联耦合的第二多个晶体管。

25.根据权利要求21所述的设备,其进一步包括比较器,其经配置以比较第一电压和参考电压并将比较器结果提供至所述仲裁器电路。

26.根据权利要求25所述的设备,其进一步包括参考电压产生器,其经配置以将所述参考电压提供至所述比较器。

27.根据权利要求25所述的设备,其进一步包括多路复用器,其中所述多路复用器经配置以将所述端子的所述电压或者中间电压作为所述第一电压提供至所述比较器。

28.根据权利要求27所述的设备,其中所述驱动器电路包括上拉电路和下拉电路,且所述中间电压为所述上拉电路和所述下拉电路之间的节点处的电压。

29.根据权利要求21所述的设备,其中仲裁器电路包括寄存器,且对所述芯片唯一的所述定时信息存储在所述寄存器中。

30.一种设备,其包括:

31.根据权利要求30所述的设备,其进一步包括:

32.根据权利要求31所述的设备,其中所述第一驱动器电路包括第一下拉电路,所述第二驱动器电路包括第二下拉电路,且所述第三驱动器电路包括上拉电路。

33.根据权利要求30所述的设备,其进一步包括比较器,其经配置以比较第一电压和参考电压并将比较器结果提供至所述仲裁器电路。

34.根据权利要求33所述的设备,其进一步包括:

35.根据权利要求34所述的设备,其中所述多路复用器提供所述端子的所述电压还是所述节点的所述电压是至少部分地基于正在执行仲裁操作还是校准操作。

36.根据权利要求33所述的设备,其进一步包括校准代码控制电路,其经配置以接收来自所述仲裁器电路的所述第一代码和来自所述比较器电路的所述比较器结果,其中所述校准代码控制电路进一步经配置以提供第二代码以启用所述第三驱动器电路,其中所述第二代码至少部分地基于对所述芯片唯一的所述定时信息。

37.一种设备,其包括:

38.根据权利要求37所述的设备,其中所述仲裁器电路经配置以至少部分地基于对所述芯片唯一的所述定时信息,在固定持续时间的起点处停用所述驱动器电路达预定时间以改变所述端子的电压。

39.根据权利要求38所述的设备,其中所述仲裁器电路进一步经配置以在所述预定时间之后启用所述驱动器电路。

40.根据权利要求37所述的设备,其中所述仲裁器电路经配置以至少部分地基于对每一芯片唯一的所述定时信息启用和停用所述驱动器电路达固定持续时间。

41.一种方法,其包括:

42.根据权利要求41所述的方法,其进一步包括,在将所述外部衬垫的所述电压下拉至所述第二电压状态达所述第二时间段之前,将所述外部衬垫的所述电压与参考电压进行比较以确定所述外部衬垫的所述电压是处于所述第一电压状态还是第二电压状态,其中当所述外部衬垫的所述电压被确定处于所述第一电压状态时,所述方法进一步包括重复浮动所述外部衬垫的所述电压达所述第一时间段。

43.根据权利要求41所述的方法,其进一步包括,在所述多个时钟循环的每一时钟循环之后,将所述外部衬垫的所述电压与参考电压进行比较以确定所述外部衬垫的所述电压是处于所述第一电压状态还是第二电压状态,其中当所述外部衬垫的所述电压被确定处于所述第一电压状态时,所述方法进一步包括重复浮动所述外部衬垫的所述电压达所述第一时间段。

44.根据权利要求41所述的方法,其中所述第一时间段为三个时钟循环。

45.根据权利要求41所述的方法,其中所述第二时间段为两个时钟循环。

46.根据权利要求41所述的方法,其中所述第一时间段至少部分地基于对于所述多个芯片中的所述芯片唯一的所述定时信息。

47.根据权利要求41所述的方法,其中所述第二时间段至少部分地基于对于所述多个芯片中的所述芯片唯一的所述定时信息。

48.一种方法,其包括:

49.根据权利要求48所述的方法,其进一步包括响应于确定所述外部衬垫的所述电压为所述第二电压状态,在所述多个时钟循环中的最后一个时钟循环之后,将所述外部衬垫的所述电压下拉至所述第一电压状态达第二时间段。

50.根据权利要求49所述的方法,其进一步包括在所述第二时间段之后,浮动所述外部衬垫的所述电压达第三时间段。

51.根据权利要求50所述的方法,其进一步包括将所述外部衬垫的所述电压下拉至所述第二电压状态;以及

52.根据权利要求50所述的方法,其中所述第三时间段为一个时钟循环。

53.根据权利要求49所述的方法,其中所述第二时间段为两个时钟循环。

54.根据权利要求48所述的方法,其中所述定时信息包含二进制代码。

55.根据权利要求54所述的方法,其中所述二进制代码在时域中成镜像。

56.一种方法,其包括:

57.根据权利要求56所述的方法,其中所述多个芯片中的具有较高优先级的芯片的延迟比具有较低优先级的芯片的延迟更长。

58.根据权利要求56所述的方法,其中对于所述多个芯片中的至少一个芯片,将所述外部衬垫的所述电压浮动达所述多个时钟循环是在不同的相位下执行的。

59.根据权利要求56所述的方法,其进一步包括在所述多个时钟循环之后,将所述外部衬垫的所述电压下拉至所述低电压状态达等于所述延迟的时钟循环数。

60.根据权利要求56所述的方法,其进一步包括在提供所述电压脉冲后执行zq校准操作。

技术总结本申请涉及用于校准半导体装置的阻抗的基于定时的仲裁方法和设备。实例系统包含电阻器和多个芯片。所述多个芯片中的每一个进一步包含耦合到所述电阻器的端子以及校准电路。所述校准电路至少部分地基于对于所述多个芯片中的对应的芯片唯一的定时信息确定所述电阻器是否是可供使用的。所述多个芯片中的每个芯片的所述定时信息具有所述多个芯片共用的固定持续时间。技术研发人员:C·G·维杜威特,J·约翰逊受保护的技术使用者:美光科技公司技术研发日:技术公布日:2024/1/15本文地址:https://www.jishuxx.com/zhuanli/20240731/182973.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 YYfuon@163.com 举报,一经查实,本站将立刻删除。

下一篇

返回列表