页缓冲器、具有其的半导体存储器装置及其操作方法与流程

- 国知局

- 2024-07-31 19:37:32

本公开总体上涉及电子装置,更具体地,涉及一种页缓冲器、具有其的半导体存储器装置及其操作方法。

背景技术:

1、半导体存储器装置是使用诸如硅(si)、锗(ge)、砷化镓(gaas)或磷化铟(inp)的半导体实现的存储器装置。半导体存储器装置可大致分类为易失性存储器装置和非易失性存储器装置。

2、易失性存储器装置是当供电中断时所存储的数据消失的存储器装置。易失性存储器装置的示例包括静态随机存取存储器(sram)、动态ram(dram)、同步dram(sdram)等。非易失性存储器装置是即使当供电中断时所存储的数据也保留的存储器装置。非易失性存储器装置的示例包括只读存储器(rom)、可编程rom(prom)、电可编程rom(eprom)、电可擦除可编程rom(eeprom)、闪存、相变ram(pram)、磁性ram(mram)、电阻ram(rram)、铁电ram(fram)等。闪存大致分类为nor型闪存和nand型闪存。

技术实现思路

1、根据本公开的一方面,提供了一种页缓冲器,该页缓冲器包括:第一电流供应电路,该第一电流供应电路连接到位线,该第一电流供应电路被配置为基于位线的电位电平将电源电压节点连接到公共感测节点或从公共感测节点阻断;第二电流供应电路,其被配置为基于公共感测节点的电流量来控制感测节点的电位电平;以及锁存单元,其被配置为基于感测节点的电位来锁存数据。

2、根据本公开的另一方面,提供了一种半导体存储器装置,该半导体存储器装置包括:存储块,其包括多个存储器串;电压发生电路,其被配置为在读操作中生成要施加到存储块的源极线的源极线电压以及要施加到存储块的字线的读电压和通过电压;位线电位调节电路,该位线电位调节电路连接到存储块的位线,该位线电位调节电路在读操作中通过对位线的电位电平进行放电来执行初始设定;以及读/写电路,该读/写电路连接到位线,该读/写电路通过基于位线的电位电平将施加到公共感测节点的电流量放大来感测数据。

3、根据本公开的另一方面,提供了一种半导体存储器装置,该半导体存储器装置包括:存储块,其包括多个存储器串;电压发生电路,其被配置为在读操作中将接地电压施加到存储块的源极线,并且生成要施加到存储块的字线的读电压和通过电压;位线电位调节电路,该位线电位调节电路连接到存储块的位线,该位线电位调节电路在读操作中通过将位线的电位电平预充电至特定电平来执行初始设定;以及读/写电路,该读/写电路连接到位线,该读/写电路通过基于位线的电位电平将施加到公共感测节点的电流量放大来感测数据。

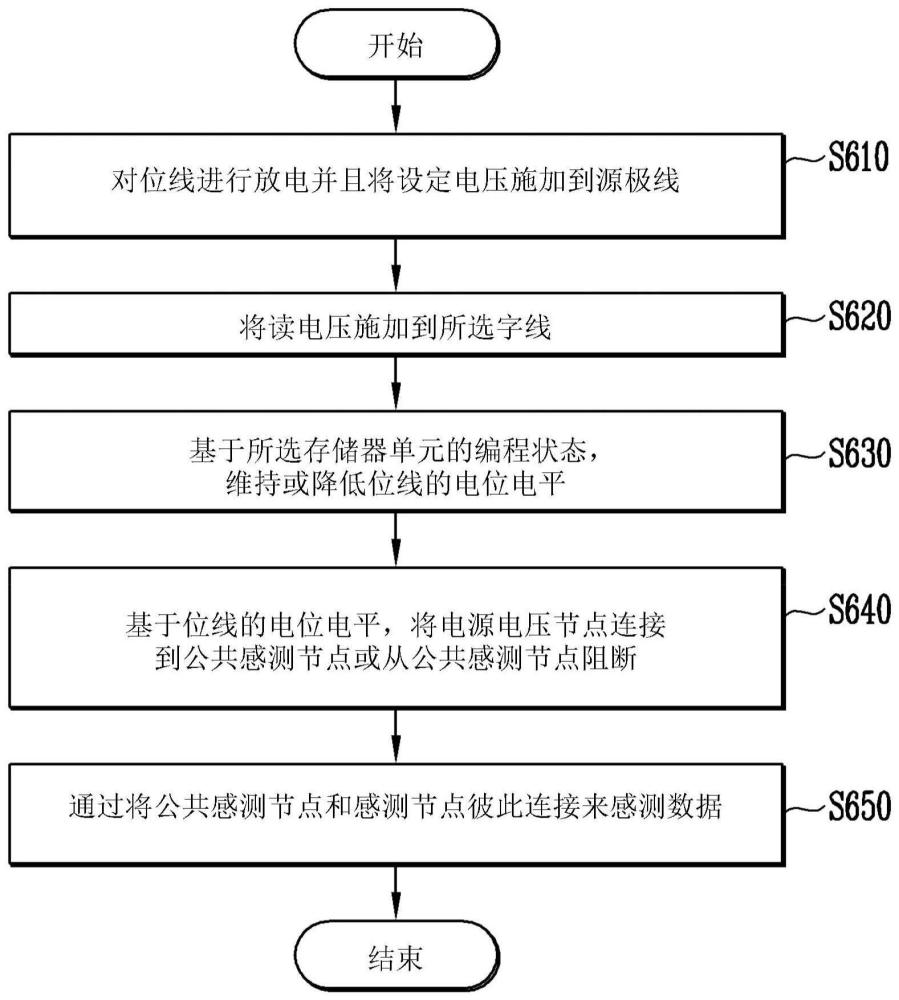

4、根据本公开的另一方面,提供了一种操作半导体存储器装置的方法,该方法包括以下步骤:对连接到存储块的位线进行放电,并且将正设定电压施加到连接到存储块的源极线;将读电压施加到存储块的所选字线;基于各条位线的电位电平将电源电压施加到分别连接到位线的各个页缓冲器的公共感测节点或从公共感测节点阻断;以及基于施加到各个页缓冲器的公共感测节点的电流量来感测数据。

5、根据本公开的另一方面,提供了一种操作半导体存储器装置的方法,该方法包括以下步骤:将连接到存储块的位线预充电至设定电平,并且将接地电压施加到连接到存储块的源极线;将读电压施加到存储块的所选字线;基于各条位线的电位电平将电源电压施加到分别连接到位线的各个页缓冲器的公共感测节点或从公共感测节点阻断;以及基于施加到各个页缓冲器的公共感测节点的电流量来感测数据。

技术特征:1.一种页缓冲器,该页缓冲器包括:

2.根据权利要求1所述的页缓冲器,其中,所述第一电流供应电路包括连接在所述电源电压节点和所述公共感测节点之间的晶体管,该晶体管响应于所述位线的电位电平而将所述电源电压节点连接到所述公共感测节点或从所述公共感测节点阻断。

3.根据权利要求2所述的页缓冲器,其中,所述晶体管被配置成nmos晶体管或耗尽nmos晶体管。

4.根据权利要求2所述的页缓冲器,其中,所述晶体管被配置成pmos晶体管或耗尽pmos晶体管。

5.根据权利要求1所述的页缓冲器,其中,当所述位线的电位电平维持处于初始状态的放电电平时,所述第一电流供应电路将所述公共感测节点与所述电源电压节点电分离,并且当所述位线的电位电平从所述放电电平上升至设定电压电平时,所述第一电流供应电路将所述公共感测节点电连接到所述电源电压节点。

6.根据权利要求1所述的页缓冲器,其中,当所述位线的电位电平维持处于初始状态的预充电电平时,所述第一电流供应电路将所述公共感测节点与所述电源电压节点电分离,并且当所述位线的电位电平从所述预充电电平下降至放电电平时,所述第一电流供应电路将所述公共感测节点电连接到所述电源电压节点。

7.一种半导体存储器装置,该半导体存储器装置包括:

8.根据权利要求7所述的半导体存储器装置,其中,所述读/写电路包括分别连接到所述位线的多个页缓冲器,并且

9.根据权利要求8所述的半导体存储器装置,其中,所述第一电流供应电路包括连接在所述电源电压节点和所述公共感测节点之间的晶体管,该晶体管响应于所连接的位线的电位电平而将所述电源电压节点连接到所述公共感测节点或从所述公共感测节点阻断。

10.根据权利要求9所述的半导体存储器装置,其中,所述晶体管被配置成nmos晶体管或耗尽nmos晶体管。

11.根据权利要求8所述的半导体存储器装置,其中,当所连接的位线的电位电平维持处于初始状态的放电电平时,所述第一电流供应电路将所述公共感测节点与所述电源电压节点电分离,并且当所连接的位线的电位电平从所述放电电平上升至设定电压电平时,所述第一电流供应电路将所述公共感测节点电连接到所述电源电压节点。

12.一种半导体存储器装置,该半导体存储器装置包括:

13.根据权利要求12所述的半导体存储器装置,其中,所述读/写电路包括分别连接到所述位线的多个页缓冲器,并且

14.根据权利要求13所述的半导体存储器装置,其中,所述第一电流供应电路包括连接在所述电源电压节点和所述公共感测节点之间的晶体管,该晶体管响应于所连接的位线的电位电平而将所述电源电压节点连接到所述公共感测节点或从所述公共感测节点阻断。

15.根据权利要求14所述的半导体存储器装置,其中,所述晶体管被配置成pmos晶体管或耗尽pmos晶体管。

16.根据权利要求13所述的半导体存储器装置,其中,当所述位线的电位电平维持处于初始状态的预充电电平时,所述第一电流供应电路将所述公共感测节点与所述电源电压节点电分离,并且当所述位线的电位电平从所述预充电电平下降至放电电平时,所述第一电流供应电路将所述公共感测节点电连接到所述电源电压节点。

17.一种操作半导体存储器装置的方法,该方法包括以下步骤:

18.根据权利要求17所述的方法,其中,在将所述电源电压施加到所述公共感测节点或从所述公共感测节点阻断的步骤中,当与所述公共感测节点对应的位线的电位电平维持处于初始状态的放电电平时,被施加有所述电源电压的电源电压节点从所述公共感测节点被电阻断,并且当与所述公共感测节点对应的所述位线的电位电平从处于初始电平的所述放电电平上升至正设定电压电平时,所述电源电压节点电连接到所述公共感测节点。

19.一种操作半导体存储器装置的方法,该方法包括以下步骤:

20.根据权利要求19所述的方法,其中,在将所述电源电压施加到所述公共感测节点或从所述公共感测节点阻断的步骤中,当与所述公共感测节点对应的位线的电位电平维持处于初始状态的预充电电平时,被施加有所述电源电压的电源电压节点从所述公共感测节点被电阻断,并且当与所述公共感测节点对应的所述位线的电位电平从处于初始电平的所述预充电电平下降至放电电平时,所述电源电压节点电连接到所述公共感测节点。

技术总结提供了一种页缓冲器、具有其的半导体存储器装置及其操作方法。该页缓冲器包括:第一电流供应电路,该第一电流供应电路连接到位线,该第一电流供应电路基于位线的电位电平将电源电压节点连接到公共感测节点或从公共感测节点阻断;第二电流供应电路,该第二电流供应电路用于基于公共感测节点的电流量来控制感测节点的电位电平;以及锁存单元,该锁存单元用于基于感测节点的电位来锁存数据。技术研发人员:徐韩受保护的技术使用者:爱思开海力士有限公司技术研发日:技术公布日:2024/2/1本文地址:https://www.jishuxx.com/zhuanli/20240731/183265.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 YYfuon@163.com 举报,一经查实,本站将立刻删除。

下一篇

返回列表