熔断器存储电路及半导体装置的制作方法

- 国知局

- 2024-07-31 19:38:28

本公开涉及熔断器存储电路。

背景技术:

1、在各种半导体装置中,作为进行制造后的特性调整或构成变更的技术,已知有微调。微调存在连续性(模拟)地进行的方法和非连续性(数字)地进行的方法,但近年来优选在成本方面有利的数字微调。

2、成本方面有利的理由可举出容易利用细微化带来的面积效率良好的数字电路、或不需要激光微调等冗余的测试流程。

3、此外,由于微调值是确定的,功能切换、基于冗余电路on/off的不良品救济的成品率提高也是数字微调受欢迎的原因。

4、作为数字微调的方法,已知有下面的方法。

5、·非易失性存储器(eeprom,flash存储器,feram,mram,pram等)

6、·熔丝(多晶硅熔断,金属布线熔断)

7、·反熔丝(齐纳管快速转换,栅极氧化膜击穿)

8、各个方法都有利有弊,因此选择与用途相符的最适当的方法。但是,在以往的微调中,并不限定于全部满足所要求的设计规格,有时被迫在一些限制下使用。

9、·非易失性存储器方式的技术问题

10、需要增加成本较高的工艺。此外,存储元件自身或锁存电路暴露在噪声或射线中时会引起软错误,需要刷新或基于错误订正电路的对策。这种状况对于模拟ic是不适合的。

11、并且,存在较短的存储保持寿命及较低的耐射线性、热导致的数据消失等限定性的耐环境性能较差的情况。

12、在需要闪存等外围电路的构成中,若存储容量小则规模优势发挥不出来。即,对于几比特~几十比特程度的微调并不适合。

13、并且,需要初始化和读取动作,因此在需要接入电源后立即确定值的用途中不能使用。

14、因此,在下面的用途中,使用采用了熔丝或反熔丝(下面,总称为熔断器元件)的熔断器存储电路。

15、·无复位/使能的模拟或混合信号(mixed-signal)的ic(integrated circuit:集成电路)

16、·需要基于冗余电路的不良品救济的产品

17、·以相同模具切换功能展开产品的用途

18、·por(power on reset:上电复位)电路的解除电压或不同电源间的起动序列变更等、将接入电源时的条件变更为可编程的所有用途

19、现有技术文献

20、专利文献

21、专利文献1:日本特开2005-85980号公报

技术实现思路

1、发明要解决的技术问题

2、对于熔断器存储电路,要求以下的特性。

3、·不需要预备动作。不需要读取动作/初始化动作。(=不需要上电(power-on)复位)

4、·高抗噪性

5、即,要求在发生外部干扰导致的数据乱码(软错误)的情况下,能够自动恢复正常状态。

6、·恒定电流小:期待的是不论熔丝的切断/未切断,恒定电流被削减到实质上为零(仅漏电流)。

7、·低成本

8、为此,期待小面积、少引脚数、低测试成本、少层数。

9、·工作电压范围广

10、具体而言,期待能够在针对熔断器存储电路以外的控制对象的电路的所有工作电压范围具有充分的余量的工作电压范围中工作。

11、·高可移动性

12、即,期待不要用于复杂控制或测试的外围电路。

13、·可测试性

14、期待能够进行程序前的假想定时及程序前后的故障检测。

15、·高可靠性

16、具体而言,期待具有半永久性的数据保持特性、高耐环境特性(热、射线)、高静电破坏耐性。

17、本公开是在相关状况中得到的,其一方案的例示性的目的之一在于,提供一种同时满足熔断器存储电路所要求的多个特性之中的几个的熔断器存储电路。

18、用于解决技术问题的方法

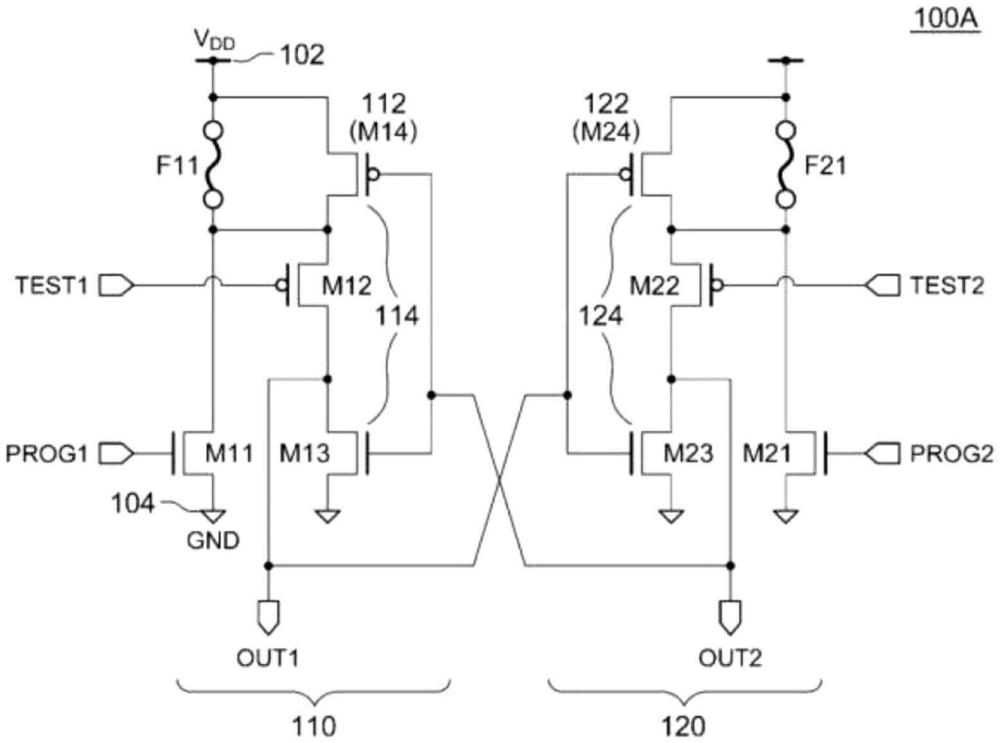

19、本公开的一方案的熔断器存储电路具备作为电源线和接地线的一者的第一线、作为电源线和接地线的另一者的第二线、第一熔断器单元、第二熔断器单元。第一熔断器单元及第二熔断器单元分别包括:测试端子;编程端子;输出端子;其第一端与第一线连接的熔断器元件;与熔断器元件并联连接的整流元件;第一晶体管,其漏极与熔断器元件的第二端连接,其源极与第二线连接,其栅极与编程端子连接;第二晶体管,其源极与熔断器元件的第二端连接,其漏极与输出端子连接,其栅极与测试端子连接;以及第三晶体管,其漏极与输出端子连接,其源极与第二线连接。第一熔断器单元的第三晶体管的栅极与第二熔断器单元的输出端子连接,第二熔断器单元的第三晶体管的栅极与第一熔断器单元的输出端子连接。

20、此外,将上述的构成要素任意组合的方案、或将本公开的表现在方法、装置等之间转换的方案作为本发明的方案也是有效的。

21、发明效果

22、根据本公开的一方案,能够同时满足熔断器存储电路所要求的多个特性之中的几个。

技术特征:1.一种熔断器存储电路,具备:

2.根据权利要求1所述的熔断器存储电路,

3.根据权利要求2所述的熔断器存储电路,

4.根据权利要求3所述的熔断器存储电路,

5.根据权利要求1所述的熔断器存储电路,

6.根据权利要求1至5的任一项所述的熔断器存储电路,

7.根据权利要求1至5的任一项所述的熔断器存储电路,

8.根据权利要求1至5的任一项所述的熔断器存储电路,

9.根据权利要求1至5的任一项所述的熔断器存储电路,

10.一种半导体装置,具备:

技术总结第一熔断器单元(110)及第二熔断器单元(120)具有相同的构成。整流元件(112)与熔断器元件并联连接。第一晶体管(M11),其漏极与熔断器元件(F11)的第二端连接,其源极与第二线(104)连接,其栅极与编程端子(PROG1)连接。第二晶体管(M12),其源极与熔断器元件(F11)的第二端连接,其漏极与输出端子(OUT1)连接,其栅极与测试端子(TEST1)连接。第三晶体管(M13),其漏极与输出端子连接,其源极与第二线(104)连接。技术研发人员:辻将信受保护的技术使用者:罗姆股份有限公司技术研发日:技术公布日:2024/2/8本文地址:https://www.jishuxx.com/zhuanli/20240731/183351.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 YYfuon@163.com 举报,一经查实,本站将立刻删除。

下一篇

返回列表