与型的快闪存储器、编程方法及抹除方法与流程

- 国知局

- 2024-07-31 19:43:06

本发明涉及一种具有与型(and型)存储单元阵列构造的快闪存储器、编程方法及抹除方法。

背景技术:

1、图1的(a)表示现有的或非型(nor)型快闪存储器的等效电路。各存储单元的源极/漏极连接于位线bl与源线sl(虚拟接地)之间,栅极连接于字线wl,而能够进行各存储单元的读取或编程。在nor型快闪存储器中,由于无法将存储单元的栅极长度定标为小于100nm,故而存储单元的定标有限制。而且,在无法定标栅极长度的情况下,也无法定标读取动作时应获得读取电流的通道宽度。因此,存储单元尺寸大致到了极限。

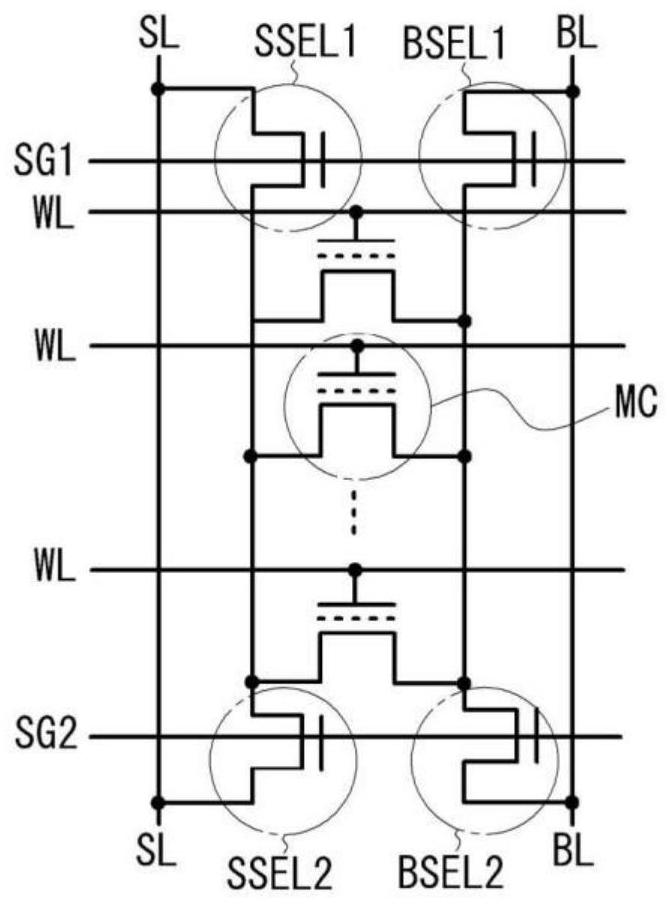

2、图1的(b)是表示and型快闪存储器的等效电路的图(非专利文献1)。在and型快闪存储器中,在局部位线lbl与局部源线lsl之间并联连接多个存储单元,存储单元的各栅极连接于字线wl。局部位线lbl经由位线侧的选择晶体管而连接于位线bl,局部源线lsl经由源线侧的选择晶体管而连接于源线sl。在选择存储单元时,通过选择控制线sg1开启位线侧的选择晶体管,通过选择控制线sg2开启源线侧的选择晶体管。

3、[非专利文献1]“a0.24-um2 cell process with 0.18um width isolation and3-d interpoly dielectric films for 1-gb flash memories”,takashi kobayashi etal.,1997iedm,p275-278

4、在现有的and型快闪存储器中,在编程动作时,由于局部源线lsl浮置,故而不会产生编程的穿通的问题。但是在编程中,需要将由源极/漏极间的通道电流所产生的热电子注入浮置栅极,而且为了抹除而排除从浮置栅极fg朝向局部位线lbl的电子时,需要增大漏极与浮置栅极fg的重叠区域。因此,存在难以将单元尺寸微细化的课题。

技术实现思路

1、本发明的目的在于提供一种and型的快闪存储器,谋求存储单元尺寸的微细化,实现高集成化。

2、本发明的and型的快闪存储器包括存储单元阵列,所述存储单元阵列包括在源线与位线之间电性并联连接的多个存储单元,在所述存储单元阵列形成并排的细长的多个扩散区域,所述并联连接的多个存储单元分别包括栅极与电荷积蓄层,所述栅极配置于相向的扩散区域之间,所述电荷积蓄层作为栅极绝缘膜而能够积蓄电荷,所述电荷积蓄层包括至少三层以上的绝缘层。

3、本发明的编程方法是一种and型的快闪存储器的编程方法,所述and型的快闪存储器包括存储单元阵列,所述存储单元阵列包括在源线与位线之间电性并联连接的多个存储单元,在所述存储单元阵列形成并排的细长的多个扩散区域,所述并联连接的多个存储单元分别具有栅极与电荷积蓄层,所述栅极配置于相向的扩散区域之间,所述电荷积蓄层作为栅极绝缘膜而包括至少三层以上的绝缘层,对选择存储单元的栅极施加编程电压,对通道施加基准电压,由此将从通道隧穿的电荷积蓄于所述电荷积蓄层。本发明的抹除方法是一种and型的快闪存储器的抹除方法,所述and型的快闪存储器包括存储单元阵列,所述存储单元阵列包括在源线与位线之间电性并联连接的多个存储单元,在所述存储单元阵列形成并排的细长的多个扩散区域,所述并联连接的多个存储单元分别具有栅极与电荷积蓄层,所述栅极配置于相向的扩散区域之间,所述电荷积蓄层作为栅极绝缘膜而包括至少三层以上的绝缘层,对选择存储单元的栅极施加基准电压,对包括通道的阱施加抹除电压,由此通过隧穿将积蓄于所述电荷积蓄层中的电荷释放至通道。在某一形态中,选择包括并联连接的多个存储单元的区块,将所选择的区块的多个存储单元一次性抹除。

4、根据本发明,在and型的存储单元阵列中,由于以存储单元具有能够积蓄电荷的包括至少三层以上的绝缘层的电荷积蓄层的方式构成,故而能够实现存储单元的微细化,且也能够简化制造工序。

技术特征:1.一种与型的快闪存储器,包括存储单元阵列,所述存储单元阵列包括在源线与位线之间电性并联连接的多个存储单元,其特征在于,

2.根据权利要求1所述的快闪存储器,其特征在于,所述电荷积蓄层包括用来积蓄电荷的氮化层。

3.根据权利要求2所述的快闪存储器,其特征在于,所述电荷积蓄层在上部绝缘层与下部绝缘层之间包括所述氮化层。

4.根据权利要求1所述的快闪存储器,其特征在于,所述电荷积蓄层相对于列方向或行方向的每个存储单元进行分离。

5.根据权利要求1所述的快闪存储器,其特征在于,所述电荷积蓄层相对于每个存储单元进行分离。

6.根据权利要求1所述的快闪存储器,其特征在于,在对选择存储单元的栅极施加编程电压时,所述电荷积蓄层积蓄从通道隧穿的电荷。

7.根据权利要求1所述的快闪存储器,其特征在于,在对选择存储单元的栅极施加基准电压,对阱区域施加抹除电压时,所述电荷积蓄层通过隧穿将所积蓄的电荷释放至通道,或使所积蓄的电子与从通道隧穿的空穴再结合。

8.根据权利要求1所述的快闪存储器,其特征在于,所述存储单元阵列还包括源线侧的选择晶体管与位线侧的选择晶体管,所述源线侧的选择晶体管用来将并联连接的n个存储单元的区块所共通的其中一扩散区域选择性地连接于源线,所述位线侧的选择晶体管用来将所述区块所共通的另一扩散区域选择性地连接于位线,

9.根据权利要求8所述的快闪存储器,其特征在于,所述源线侧的选择晶体管包括第一选择晶体管与第二选择晶体管,所述第一选择晶体管用来将所述区块的开端的存储单元的其中一扩散区域连接于源线,所述第二选择晶体管用来将最后的存储单元的其中一扩散区域连接于源线,

10.根据权利要求9所述的快闪存储器,其特征在于,所述区块的n个存储单元的各栅极分别连接于沿着行方向在存储单元阵列上延伸的字线,所述第一选择控制线及所述第二选择控制线与字线平行地延伸。

11.根据权利要求8所述的快闪存储器,其特征在于,所述源线侧的选择晶体管的其中一扩散区域电性连接于存储单元的其中一扩散区域,另一扩散区域经由导电性接点构件而电性连接于源线,

12.根据权利要求11所述的快闪存储器,其特征在于,所述源线侧的选择晶体管包括作为栅极绝缘膜的电荷积蓄层与其他绝缘膜的叠层,所述位线侧的选择晶体管包括作为栅极绝缘膜的电荷积蓄层与其他绝缘膜的叠层。

13.根据权利要求8所述的快闪存储器,其特征在于,所述快闪存储器还包括编程控制部件,所述编程控制部件对存储单元的编程进行控制,

14.根据权利要求8所述的快闪存储器,其特征在于,在编程控制部件对选择存储单元进行编程的情况下,开启第一选择晶体管及第二选择晶体管,使所述区块的其中一扩散区域与另一扩散区域电性连接于源线及位线,对选择字线施加编程电压,对非选择字线施加中间电压。

15.根据权利要求8所述的快闪存储器,其特征在于,所述快闪存储器还包括抹除控制部件,所述抹除控制部件对存储单元的抹除进行控制,

16.一种编程方法,为与型的快闪存储器的编程方法,所述与型的快闪存储器包括存储单元阵列,所述存储单元阵列包括在源线与位线之间电性并联连接的多个存储单元,其特征在于,

17.根据权利要求16所述的编程方法,其特征在于,将并联连接的选择存储单元及非选择存储单元的共通的扩散区域设为浮置状态,通过对选择存储单元及非选择存储单元的各栅极施加的电压使所述选择存储单元的扩散区域及通道自升压,而禁止选择存储单元的编程。

18.根据权利要求16所述的编程方法,其特征在于,对并联连接的选择存储单元及非选择存储单元的共通的扩散区域施加基准电压,对选择存储单元的栅极施加编程电压,对非选择存储单元施加中间电压,由此进行选择存储单元的编程。

19.一种抹除方法,为与型的快闪存储器的抹除方法,与型的快闪存储器包括存储单元阵列,所述存储单元阵列包括在源线与位线之间电性并联连接的多个存储单元,其特征在于,

20.根据权利要求19所述的抹除方法,其特征在于,选择包括并联连接的多个存储单元的区块,将所选择的区块的多个存储单元一次性抹除。

技术总结本发明提供一种与型的快闪存储器、编程方法及抹除方法。本发明的与型的快闪存储器包括在源线与位线之间并联连接的多个存储单元。存储单元包括包含SiN层的电荷积蓄层作为栅极绝缘膜而构成。在编程时,在存储单元的电荷积蓄层中积蓄从通道FN隧穿的电子。在抹除时,将积蓄于存储单元的电荷积蓄层中的电子释放至通道。技术研发人员:白田理一郎受保护的技术使用者:华邦电子股份有限公司技术研发日:技术公布日:2024/3/4本文地址:https://www.jishuxx.com/zhuanli/20240731/183646.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 YYfuon@163.com 举报,一经查实,本站将立刻删除。

下一篇

返回列表