一种用于访问SDRAM的EMIF的验证方法与流程

- 国知局

- 2024-07-31 19:51:44

本申请涉及芯片验证领域,具体而言本申请实施例涉及一种用于访问sdram的emif的验证方法。

背景技术:

1、在数字ic的设计中有很多的接口,对于不同类型的接口来说,需要不同的验证方法或验证平台。

2、在数字ic接口的设计越来越多的今天,繁杂的接口协议以及越来越多的接口信号数量使得验证的难度越来越高,其中验证平台的可移植性成为制约验证效率的关键因素。对于接口设计的验证而言亦是如此。在外部存储器接口emif(external memoryinterface)这种用来访问同步动态随机存取内存(synchronous dynamic random-accessmemory,简称sdram)的模块来说,对sdram的交互信号相对较多,协议也较多,相关技术提供的验证方法验证繁琐耗时且验证方法无通用性。

技术实现思路

1、本申请实施例的目的在于提供一种用于访问sdram的emif的验证方法,本申请实施例提出了一种基于uvm的针对emif接口的验证平台及验证方法,采用本申请实施例的验证方法可以提升验证效率且本申请实施例的验证方法具有极高的可移植性和通用性。

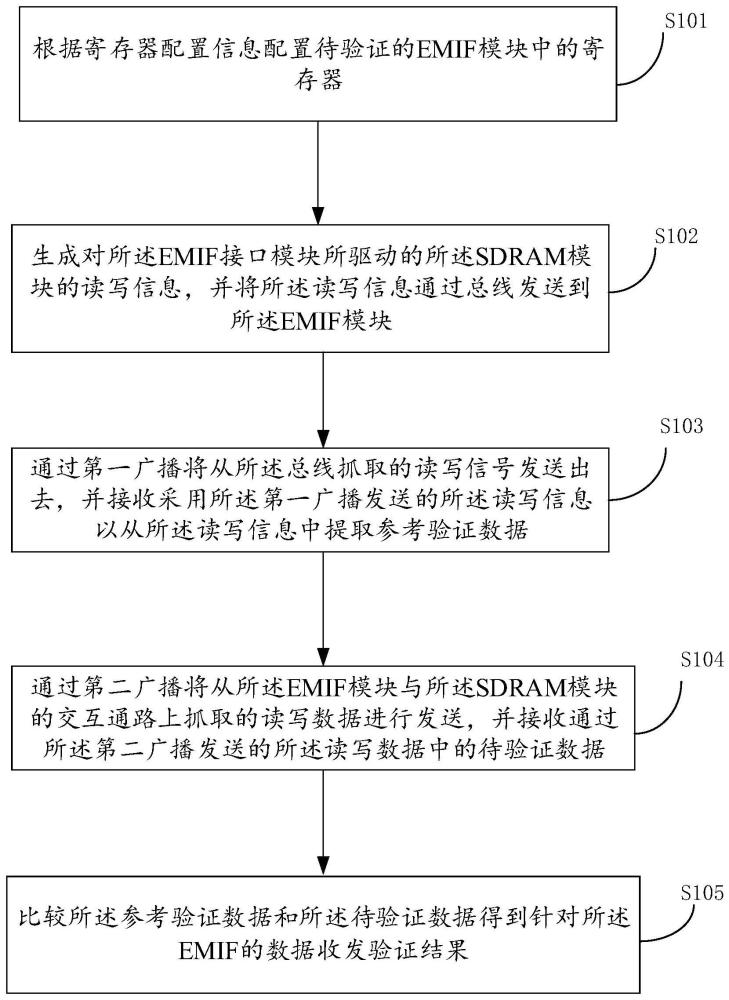

2、第一方面,本申请实施例提供一种用于访问sdram的emif的验证方法,所述验证方法包括:根据寄存器配置信息配置待验证的emif模块中的寄存器,其中,所述寄存器配置信息是与所述emif模块所需访问的sdram模块相适应的,所述寄存器配置信息包括用于对所述emif模块进行配置的第一配置信息以及用于对所述sdram模块进行配置的第二配置信息,所述第二配置信息包括时序配置信息;生成对所述emif接口模块所驱动的所述sdram模块的读写信息,并将所述读写信息通过总线发送到所述emif模块;通过第一广播将从所述总线抓取的读写信号发送出去,并接收采用所述第一广播发送的所述读写信息以从所述读写信息中提取参考验证数据,其中,所述读写信号包括寄存器读写信号与数据读写信号,所述第一广播中的广播包通过类别信号来表征所抓取的所述读写信号属于寄存器的包或者数据包,所述寄存器的包用于携带寄存器配置数据,所述数据包用于携带写入可读写存储空间的数据;通过第二广播将从所述emif模块与所述sdram模块的交互通路上抓取的读写数据进行发送,并接收通过所述第二广播发送的所述读写数据中的待验证数据,比较所述参考验证数据和所述待验证数据得到验证结果。

3、在一些实施例中,所述验证方法还包括:通过所述sdram模块中设置的配置比对模块、命令对比模块以及数据存储模块完成对所述emif模块的验证,其中,所述配置比对模块包括与所述寄存器配置信息所对应参数的映射空间,所述命令对比模组具备指令识别逻辑,所述数据存储模块对应的数据存储空间可被从所述emif模块收到的指令进行读写。

4、在一些实施例中,所述根据寄存器配置信息配置待验证的emif模块中的寄存器,包括:通过寄存器序列发生器regsequencer将所述寄存器配置信息通过寄存器驱动器regdriver驱动总线bus来进行所述emif模块中寄存器的配置。

5、在一些实施例中,所述生成对所述emif模块所驱动的所述sdram模块的读写信息,并将所述读写信息发送到所述emif模块,包括:通过数据发生序列datasequence生成所述读写信息,并通过数据序列生成器datasequencer将所述读写信息通过数据驱动器datadriver发送到所述emif模块。

6、在一些实施例中,在通过第一广播将从所述总线抓取的读写信号发送出去之前,所述方法还包括:搭建寄存器驱动器reg driver和数据驱动器datadriver,其中,所述寄存器驱动器reg或者所述数据驱动器datadriver用于对相应序列发生器发过来的数据驱动至总线上以达到对所述总线写或读的操作;通过所述寄存器驱动器或者所述数据驱动器将相应信息驱动至所述总线,并在所述总线上抓取所述读写信号。

7、在一些实施例中,所述通过所述sdram模块中设置的配置比对模块、命令对比模块以及数据存储模块完成对所述emif模块的验证,包括:通过所述配置比对模块接收来自所述第一广播的广播包并解析,得到解析广播包;通过所述配置比对模块收集所述解析广播包中的针对所述sdram模块中的寄存器的寄存器配置信息,得到目标寄存器配置信息;依据所述目标寄存器配置信息在之后的数据访问中控制所述sdram模块的数据吞吐行为,并依据所述目标寄存器配置信息配置所述sdram模块的数据宽度及深度。

8、在一些实施例中,所述通过所述sdram模块中设置的配置比对模块、命令对比模块以及数据存储模块完成对所述emif模块的验证,包括:通过指令比对模块获取由所述emif模块发出的指令,得到待验证指令,并判断与所述待验证指令对应的时序参数是否满足所述时序配置信息;若确认所述时序参数满足要求,则执行所述待验证指令以对所述sdram模块中的存储数据进行操作。

9、在一些实施例中,所述时序参数包括行刷新时间trfc(row refresh time)、行预充电时间trp(row precharge time)、行指令等待时间trcd(row command delay time)、写恢复时间twr(recovery time)、行激活建立时间tras(active set time)、两次激活指令之间的间隔时间trc(time between command)以及行到行的延时trrd(row to row delay)。这些参数属于sdram的时序参数。

10、在一些实施例中,在所述执行所述待验证指令之前,所述方法还包括:比对所述待验证指令的产生顺序符合设定的先后顺序。

11、在一些实施例中,所述执行所述待验证指令以对所述sdram模块中的存储数据进行操作,包括:若所述待验证指令为写数据操作,则通过所述写数据操作可修改所述sdram模块的存储数据;若所述待验证指令为读数据操作,则通过所述读数据操作可将所述sdram模块中的相关数据驱动到与所述emif模块对应的数据读接口上。

技术特征:1.一种用于访问sdram的emif的验证方法,其特征在于,所述验证方法包括:

2.如权利要求1所述的验证方法,其特征在于,所述验证方法还包括:

3.如权利要求1所述的验证方法,其特征在于,所述根据寄存器配置信息配置待验证的emif模块中的寄存器,包括:

4.如权利要求1所述的验证方法,其特征在于,所述生成对所述emif模块所驱动的所述sdram模块的读写信息,并将所述读写信息发送到所述emif模块,包括:

5.如权利要求1所述的验证方法,其特征在于,在通过第一广播将从所述总线抓取的读写信号发送出去之前,所述方法还包括:

6.如权利要求2所述的验证方法,其特征在于,所述通过所述sdram模块中设置的配置比对模块、命令对比模块以及数据存储模块完成对所述emif模块的验证,包括:

7.如权利要求2所述的验证方法,其特征在于,所述通过所述sdram模块中设置的配置比对模块、命令对比模块以及数据存储模块完成对所述emif模块的验证,包括:

8.如权利要求7所述的验证方法,其特征在于,所述时序参数包括行刷新时间trfc、行预充电时间trp、行指令等待时间trcd、写恢复时间twr、行激活建立时间tras、两次激活指令之间的间隔时间trc以及行到行的延时trrd。

9.如权利要求7所述的验证方法,其特征在于,在所述执行所述待验证指令之前,所述方法还包括:比对所述待验证指令的产生顺序符合设定的先后顺序。

10.如权利要求7所述的验证方法,其特征在于,所述执行所述待验证指令以对所述sdram模块中的存储数据进行操作,包括:

技术总结本申请实施例提供一种用于访问SDRAM的EMIF的验证方法,所述验证方法包括:根据寄存器配置信息配置待验证的EMIF模块中的寄存器;生成对所述EMIF接口模块所驱动的所述SDRAM模块的读写信息,并将所述读写信息通过总线发送到所述EMIF模块;通过第一广播将从所述总线抓取的读写信号发送出去,并接收采用所述第一广播发送的所述读写信息以从所述读写信息中提取参考验证数据;通过第二广播将从所述EMIF模块与所述SDRAM模块的交互通路上抓取的读写数据进行发送,并接收通过所述第二广播发送的所述读写数据中的待验证数据,比较所述参考验证数据和所述待验证数据得到验证结果。采用本申请实施例的验证方法可提升验证效率且本申请实施例的验证方法具有极高的可移植性和通用性。技术研发人员:王宏伟,冯新华,朱双双受保护的技术使用者:北京中科昊芯科技有限公司技术研发日:技术公布日:2024/4/29本文地址:https://www.jishuxx.com/zhuanli/20240731/184400.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 YYfuon@163.com 举报,一经查实,本站将立刻删除。

下一篇

返回列表