非易失性存储控制及校准方法、装置、设备、存储介质与流程

- 国知局

- 2024-07-31 19:51:39

本技术涉及非易失性存储,具体涉及一种非易失性存储控制及校准方法、装置、设备、存储介质。

背景技术:

1、非易失性存储(nvm,即non-volatile memory)在集成电路设计、集成领域广泛应用。通常非易失性存储的概念范围较大,nand/nor flash(闪存)、mtp(multiple-timeprogrammable,多次编程)都属于nvm(non-volatile memory,非易失性存储)范畴。非易失性存储(nvm)特点是存储的数据不会因为电源关闭而消失,常常应用于操作系统和应用程序的存储等场合。

2、因非易失性存储自身特性以及所处工作环境等影响,实际应用中需要正确、可靠地对非易失性存储执行一些操作,而对非易失性存储操作的正确性和可靠性,依赖于两个重要因素:其一,满足真值表和时序两方面的控制要求;其二,满足校准地址和校准数据关联性要求。但是,现有方案很难兼顾上述两个重要因素,造成对非易失性存储操作的正确性、可靠性等很难保证。

技术实现思路

1、有鉴于此,本技术提供一种非易失性存储控制及校准方法、装置、设备、存储介质。

2、本技术提供以下技术方案:

3、本技术提供一种非易失性存储控制方法,包括:

4、获取原子任务所需的数据包,其中所述原子任务为对非易失性存储操作的原子任务,所述数据包包括以下预设的字段数据:特征同步头,用于表征原子任务属性的目标操作码,与所述目标操作码对应的原子任务信息,所述原子任务信息包括非易失性存储操作对象地址步长、非易失性存储操作对象起始地址、非易失性存储操作对象结束地址和非易失性存储编程数据队列,所述非易失性存储编程数据队列用于存放所述目标操作码对应的任务数据;

5、解析并提取所述数据包中的各所述字段数据;

6、根据所述字段数据中的目标操作码将所述数据包缓存到通道阵列中的对应任务通道,其中所述通道阵列中的任务通道包括:用于擦除任务处理的擦除任务通道,用于编程任务处理的编程任务通道,用于读访问任务处理的读访问任务通道,以及用于校准任务处理的校准任务通道;

7、根据所述目标操作码建立对应的任务连接,并创建对应的若干原子操作,基于所述任务连接依次对非易失性存储执行各所述原子操作。

8、优选地,各任务通道为以下任意一种缓存结构:fifo,block ram堆叠+block ram读写块地址管理。

9、优选地,所述非易失性存储控制方法还包括:实时获取各任务通道对所述数据包的缓冲状态:空、满、快空、快满;

10、根据所述字段数据中的目标操作码将所述数据包缓存到通道阵列中的对应任务通道,包括:根据所述缓存状态和所述字段数据中的目标操作码,将所述数据包缓存到通道阵列中的对应任务通道,防止所述数据包缓存到对应任务通道时发生上溢。

11、优选地,所述数据包缓存到对应任务通道的方式包括:单任务独立模式或者多任务并发模式,其中所述单任务独立模式为在通道阵列中的各任务通道中,当所有任务通道均无数据包时,所述数据包缓存到对应任务通道;所述多任务并发模式为在通道阵列中的各任务通道中,无论各任务通道有无数据包,所述数据包缓存到不存在上溢的对应任务通道。

12、优选地,当根据所述字段数据中的目标操作码确定出所述原子任务为对通道阵列进行全局配置任务时,所述非易失性存储控制方法还包括:配置所述任务数据中的操作码与所述通道阵列中的各任务通道的对应关系,并根据所述任务数据中的优先级配置所述通道阵列中的各任务通道对应的调度优先级,其中所述任务数据包括以下至少一种数据:擦除操作码、编程操作码、读访问操作码、校准操作码、优先级。

13、优选地,在完成全局配置任务后,根据已配置的调度优先级依次从对应任务通道中获取已缓存在对应任务通道中的所述数据包。

14、本技术还提供一种非易失性存储校准方法,其特征在于,包括:

15、基于本技术中任意一项所述的非易失性存储控制方法,在对非易失性存储执行当前的原子操作中,当接收到的数据包为校准数据包时,暂停下一个原子操作,并从校准通道中获取非易失性存储校准任务对应的数据包;

16、建立非易失性存储校准任务对应的任务连接,并创建校准任务对应的若干校准原子操作,基于所述任务连接依次对非易失性存储的目标校准地址的存储空间执行各校准原子操作。

17、优选地,所述非易失性存储校准方法还包括:完成当前的校准任务时,监视校准任务通道是否非空;若校准任务通道为空,则结束本次校准任务,并将暂停的下一个原子操作重启;若校准任务通道非空,则继续执行下一次校准任务。

18、优选地,所述非易失性存储校准方法还包括:将原子操作的启动信号转换成输出事件或者输出中断,以通过事件或中断方式进行状态反馈。

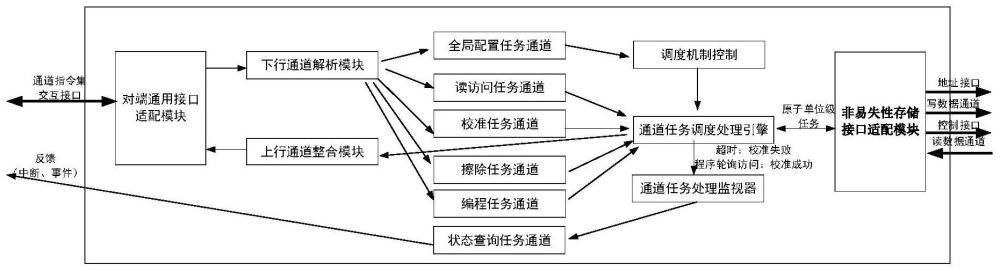

19、本技术还提供一种非易失性存储控制装置,包括:对端通用接口适配模块、下行通道解析模块、通道阵列、任务调度处理引擎和非易失性存储接口适配模块;

20、对端通用接口适配模块通过通道指令集交互接口与对端装置连接,并用于接收对端装置发送的原子任务对应的数据包,其中所述原子任务为对非易失性存储操作的原子任务,所述数据包包括以下预设的字段数据:特征同步头,用于表征原子任务属性的目标操作码,与所述目标操作码对应的原子任务信息,所述原子任务信息包括非易失性存储操作对象地址步长、非易失性存储操作对象起始地址、非易失性存储操作对象结束地址和非易失性存储编程数据队列,所述非易失性存储编程数据队列用于存放所述目标操作码对应的任务数据;

21、下行通道解析模块用于解析并提取所述数据包中的各所述字段数据,并根据所述字段数据中的目标操作码将所述数据包缓存到通道阵列中的对应任务通道,其中所述通道阵列中的任务通道包括:用于擦除任务处理的擦除任务通道,用于编程任务处理的编程任务通道,用于读访问任务处理的读访问任务通道,以及用于校准任务处理的校准任务通道;

22、任务调度处理引擎用于根据下行通道解析模块提取的所述目标操作码,与非易失性存储接口适配模块建立对应的任务连接,并创建对应的若干原子操作;

23、非易失性存储接口适配模块与非易失性存储连接,基于所述任务连接依次对非易失性存储执行各所述原子操作。

24、优选地,下行通道解析模块在解析并提取所述数据包中的各所述字段数据前,通过识别所述数据包中的特征同步头和所述目标操作码的方式,确定所述数据包的有效性;

25、和/或,下行通道解析模块在解析并提取所述数据包中的各所述字段数据前,通过识别所述数据包中的特征同步头,界定对端装置对非易失性存储的操作任务数据的原子性。

26、优选地,所述非易失性存储控制装置还包括全局配置任务通道和调度机制控制模块;

27、全局配置任务通道用于当下行通道解析模块解析并提取到所述字段数据中的目标操作码确定出所述原子任务为对通道阵列进行全局配置任务时,配置所述任务数据中的操作码与所述通道阵列中的各任务通道的对应关系;,其中所述任务数据包括以下至少一种数据:擦除操作码、编程操作码、读访问操作码、校准操作码、优先级;

28、调度机制控制模块用于根据所述任务数据中的优先级配置所述通道阵列中的各任务通道对应的调度优先级,以引导通道任务调度处理引擎按照指定的优先级或轮询调度权重,对所述通道阵列中的读访问任务通道、校准任务通道、擦除任务通道、编程任务通道内的数据包进行调度处理。

29、优选地,任务调度处理引擎创建对应的若干原子操作,包括:根据所述原子任务信息中的非易失性存储操作对象地址步长、非易失性存储操作对象起始地址和非易失性存储操作对象结束地址,分解产生n个用于对非易失性存储原子操作任务,其中n=(操作对象结束地址-操作对象起始地址+1)/操作对象步长;

30、以及,任务调度处理引擎还用于依次将n个非易失性存储原子操作任务压入任务队列,传递至非易失性存储接口适配模块,由非易失性存储接口适配模块依次响应n个任务产生相应的n个非易失性存储的控制操作。

31、优选地,非易失性存储原子操作任务包括以下至少一个任务:对非易失性存储指定sector的擦除任务,对非易失性存储指定page的擦除任务,对非易失性存储chip的擦除任务,对非易失性存储指定地址的编程任务,对非易失性存储指定地址的读访问任务,对非易失性存储指定地址的校准编程任务。

32、本技术还提供一种非易失性存储校准装置,包括:如本技术中任意一项所述的非易失性存储控制装置,其中所述非易失性存储控制装置分别与对端装置和非易失性存储连接,所述非易失性存储控制装置在对非易失性存储执行当前的原子操作中,当接收到的数据包为校准数据包时,暂停下一个原子操作,并从校准通道中获取非易失性存储校准任务对应的数据包,以及建立非易失性存储校准任务对应的任务连接,并创建校准任务对应的若干校准原子操作,基于所述任务连接依次对非易失性存储的目标校准地址的存储空间执行各校准原子操作。

33、优选地,所述非易失性存储控制装置还包括通道任务处理监视器,以及所述非易失性存储控制装置中的通道阵列还包括状态查询任务通道;其中,所述非易失性存储控制装置中的通用任务调度处理引擎还用于产生非易失性存储原子操作任务的启动信号,并将非易失性存储原子操作任务的启动信号实时输出至通道任务处理监视器;通道任务处理监视器用于将非易失性存储原子操作任务的启动信号转换成输出事件或者输出中断,经过状态查询任务通道处理反馈至对端装置。

34、本技术还提供一种电子设备,包括:至少一个处理器;以及,与所述至少一个处理器通信连接的存储器;其中,所述存储器存储有可被所述至少一个处理器执行的指令,所述指令被所述至少一个处理器执行,以使所述至少一个处理器能够执行:本技术中任一项所述的非易失性存储控制方法,或,本技术7-9中任一项所述的非易失性存储校准方法。

35、本技术还提供一种计算机存储介质,所述计算机存储介质存储有计算机可执行指令,所述计算机可执行指令被处理器执行时执行:本技术中任一项所述的非易失性存储控制方法,或,本技术中任一项所述的非易失性存储校准方法。

36、与现有技术相比,本说明书实施例采用的上述至少一个技术方案能够达到的有益效果至少包括:

37、针对非易失性存储访问控制,本技术基于通道处理和通道指令集接口实现原子级的操作任务处理,直接在数据通道基础上对数据包封装和解析,不需要考虑过多地址映射关系,就能够实现非易失性存储的擦除、编程、读访问、校准等操作,实施策略更方便,实施难度更简易,能够达到直接操作非易失性存储接口的效果。

本文地址:https://www.jishuxx.com/zhuanli/20240731/184391.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 YYfuon@163.com 举报,一经查实,本站将立刻删除。

上一篇

一种智能播放器的制作方法

下一篇

返回列表