非易失性存储器及其块擦除方法与流程

- 国知局

- 2024-07-31 19:50:44

本发明涉及存储器,尤其涉及一种非易失性存储器及其块擦除方法。

背景技术:

1、non-volatile(非易失性)存储器常涉及erase(擦除)操作,目前存储器的擦除操作一般通过fowler-nordheim tunneling(福勒-诺德海姆隧道)效应实现:通过在存储器的存储单元的gate(栅极)施加负高压,例如-10v(伏特),并在bulk(体)或p-well(p-肼)上施加正高压,例如+8v,以从存储单元中移除存储的电荷或电子,将其重置为unprogrammed s(未编程)状态或擦除状态。目前对存储器的块擦除(包括half block和block erase)操作有两种方式:并行擦除和串行擦除,所谓并行擦除是指块包括的所有sector(扇区)同时执行擦除操作,串行擦除是指块包括的所有sector一个接一个逐一执行擦除操作。由于诸如工艺变动、磨损和损耗以及被program/erase(编程/擦除)的次数多少等各种因素,一些存储单元可能会保留一定水平的电荷,第一种并行擦除的方式会导致存储器的存储块内非均匀的vt电压分布,这种不均匀性对存储器的耐久性和读取速度等性能参数会产生不利影响;第二种串行擦除的方式虽然可以减轻存储块内非均匀的vt电压分布的问题,但是擦除时间较长,并且随着program/erase cycling(编程/擦除循环)次数的增加,可能会超过块擦除规定的允许时长;此外,对于每个扇区需要执行一次从擦除状态切换到逐位擦除验证状态,给扇区提供电压的充电泵充电、放电,以及负高压与正高压之间的切换,也会增加总擦除时间的开销。

技术实现思路

1、本发明要解决的技术问题是为了克服现有技术中的缺陷,提供一种。

2、本发明是通过下述技术方案来解决上述技术问题:

3、本发明要解决的技术问题是为了克服现有技术中的上述缺陷,提供一种非易失性存储器及其块擦除方法。

4、本发明是通过下述技术方案来解决上述技术问题:

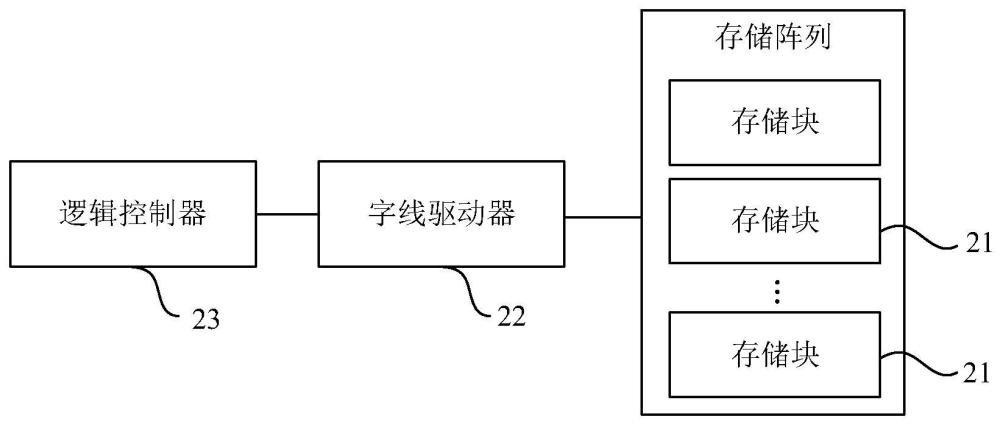

5、第一方面,提供一种非易失性存储器,包括:存储块、字线驱动器和逻辑控制器;每个存储块包括多个扇区,每个扇区对应多个字线驱动器;

6、逻辑控制器与所述字线驱动器连接;所述逻辑控制器用于在执行块擦除命令的擦除阶段,触发与目标扇区对应的字线驱动器对所述目标扇区执行擦除操作和擦除验证操作,并通过所述字线驱动器存储所述擦除验证操作的验证结果;其中,所述目标扇区为选中擦除且所述验证结果为验证未通过的扇区;所述存储块包含的其他扇区处于非擦除状态;所述其他扇区为所述存储块包含的所有扇区中除了所述目标扇区之外的扇区。

7、可选地,所述逻辑控制器同时触发与各个目标扇区对应的字线驱动器对所述目标扇区执行擦除操作;

8、和/或,所述逻辑控制器还用于在所述存储块的所有扇区的验证结果均为验证通过的情况下,清除所述字线驱动器存储的验证结果。

9、可选地,所述字线驱动器包括标志寄存器电路和电压施加电路;

10、所述标志寄存器电路的输入端与所述逻辑控制器的第一输出端连接,所述标志寄存器电路的输出端与所述电压施加电路的第一输入端连接;

11、所述电压施加电路的第二输入端与逻辑控制器的第二输出端连接,所述电压施加电路的输出端与所述扇区连接;

12、所述逻辑控制器通过所述第一输出端输出所述验证结果至所述标志寄存器电路,以触发所述标志寄存器电路输出与所述验证结果相匹配的验证电平信号至所述电压施加电路;

13、所述逻辑控制器还通过所述第二输出端输出所述扇区的地址信号至所述电压施加电路;

14、所述电压施加电路根据所述验证电平信号和所述地址信号输出与所述擦除操作相匹配的电压和/或所述擦除验证操作相匹配的电压。

15、可选地,所述标志寄存器电路包括标志寄存器和非门;

16、所述标志寄存器的输入端作为所述标志寄存器电路的输入端,所述标志寄存器的输出端与所述非门的输入端连接,所述非门的输出端作为所述标志寄存器电路的输出端。

17、可选地,所述标志寄存器包括静态随机存取存储器或锁存器或掉电不丢失的寄存器。

18、第二方面,提供一种非易失性存储器的块擦除方法,所述非易失性存储器包含多个存储块,每个存储块包含多个扇区,每个扇区对应多个字线驱动器,每个字线驱动器与对应的扇区连接;所述块擦除方法包括:

19、在执行块擦除命令的擦除阶段,触发与目标扇区连接的字线驱动器对所述目标扇区执行擦除操作和擦除验证操作;

20、通过所述字线驱动器存储所述擦除验证操作的验证结果;

21、其中,所述目标扇区为选中擦除且所述验证结果为验证未通过的扇区;所述存储块包含的其他扇区处于非擦除状态;所述其他扇区为所述存储块包含的所有扇区中除了所述目标扇区之外的扇区。

22、可选地,触发与目标扇区连接的字线驱动器对所述目标扇区执行擦除操作,包括:

23、对于每次擦除操作,同时触发与各个目标扇区连接的字线驱动器对所述目标扇区执行擦除操作。

24、可选地,所述触发与目标扇区连接的字线驱动器对所述目标扇区执行擦除操作和擦除验证操作,包括:

25、输出验证结果和所述扇区的地址信号至所述字线驱动器,以触发所述字线驱动器根据所述输出验证结果和所述地址信号输出与所述擦除操作相匹配的电压或者与所述擦除验证操作相匹配的电压。

26、可选地,其特征在于,触发与目标扇区连接的字线驱动器对所述目标扇区执行擦除验证操作,包括:

27、触发与目标扇区连接的字线驱动器施加与所述擦除验证操作相匹配的电压至所述目标扇区;

28、对于每个目标扇区,逐位读取并验证所述目标扇区包含的位线上的电压是否落入与预期擦除状态相匹配的电压范围;

29、在有目标位线的电压未落入与所述预期擦除状态相匹配的电压范围的情况下,确定包含所述目标位线的目标扇区的验证结果为验证不通过,对所有的所述目标扇区继续执行擦除操作和擦除验证操作;

30、和/或,在当前验证的位线的电压落入与所述预期擦除状态相匹配的电压范围的情况下,判断所述当前验证的位线是否为当前验证的位线所在的所述目标扇区的最后一个位线;并在判断结果为是时,将当前验证的位线所在的所述目标扇区的验证结果存储为验证通过;在判断结果为否时,返回逐位读取并验证所述目标扇区包含的位线上的电压的。

31、可选地,通过所述字线驱动器存储所述擦除验证操作的验证结果的步骤之后,还包括:

32、在所述存储块的所有扇区的验证结果均为验证通过的情况下,清除所述字线驱动器存储的验证结果。

33、本发明的积极进步效果在于:本发明对扇区执行擦除验证操作后,会记录扇区的验证结果,后续仅对待擦除的块所包括的选中擦除且验证结果为验证未通过的扇区即目标扇区执行擦除操作和擦除验证操作,对待擦除的块所包括的验证结果为验证通过的扇区即其他扇区不再执行擦除操作和擦除验证操作,从而一方面可以避免对其他扇区执行多余擦除操作而导致减少其他扇区的使用寿命,避免其他扇区被过度擦除导致存储块内非均匀的电压分布现象;另一方面,逻辑控制器同时触发多个字线驱动器对多个目标扇区执行擦除操作,以缩短存储块的整体擦除时长。

本文地址:https://www.jishuxx.com/zhuanli/20240731/184319.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 YYfuon@163.com 举报,一经查实,本站将立刻删除。