一种新型抗辐照加固SRAM单元电路

- 国知局

- 2024-07-31 19:50:41

本发明涉及集成电路,尤其涉及一种新型抗辐照加固sram单元电路。

背景技术:

1、随着集成电路技术和航空航天行业的迅猛发展,对于具有高可靠性和高性能的抗辐射集成电路的需求日益增长。在这个领域中,静态随机存储器(sram)因其卓越的性能特性,已成为集成电路的关键组成部分,且在芯片总面积中占有显著比例。

2、然而,sram存储器面临着重大的挑战,主要是由于太空环境中高能辐射粒子的轰击,这些粒子会造成单粒子瞬态效应。高能粒子轰击存储器中的半导体器件时,其电离产生的自由电荷会被存储器电路敏感节点吸收,导致存储数据发生翻转或节点逻辑状态发生改变,直接或间接影响系统的正常运转,进而导致存储器数据的紊乱和电子设备功能异常。此外,随着集成电路工艺的不断发展,器件的尺寸及其间距已显著缩小,从而导致sram单元的临界电荷下降,增加了其受单粒子效应影响的可能性。

技术实现思路

1、本发明通过提供一种新型抗辐照加固sram单元电路,解决了现有技术中器件的尺寸和间距显著缩小,且sram单元的临界电荷下降的问题,实现了利用电路中未受到影响节点的反馈作用将其恢复至正确逻辑值,完成逻辑状态出错到自恢复的容错过程,有效提高sram单元抵抗单粒子效应的能力。

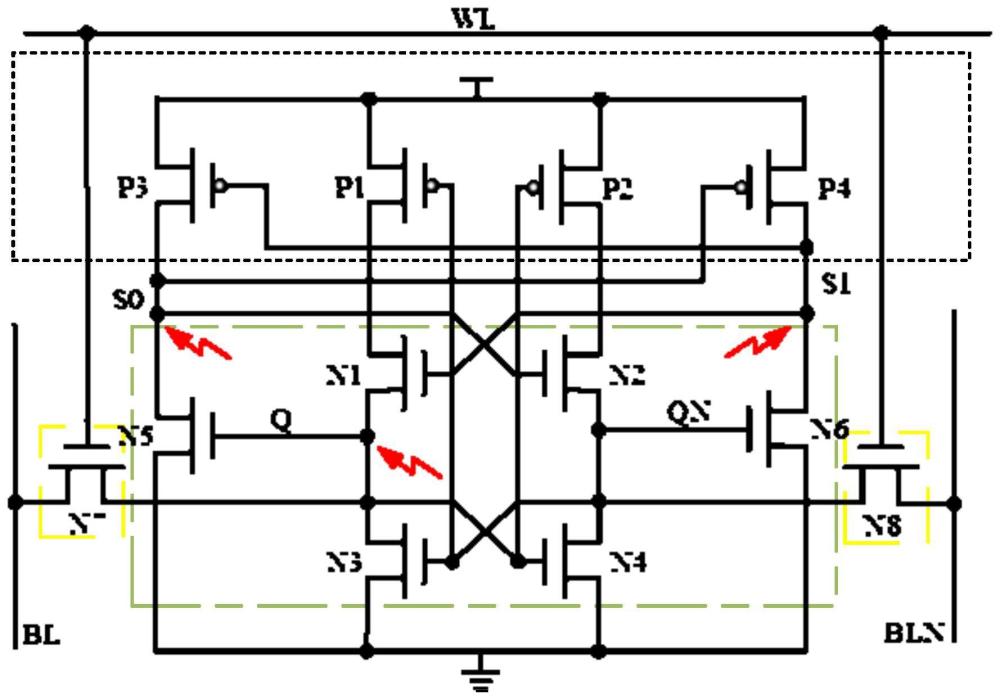

2、本发明提供了一种新型抗辐照加固sram单元电路,该电路包括:上拉电路、下拉电路、存取管电路、字线和位线;

3、所述上拉电路用于利用vdd将存储节点维持在稳定的高电平;

4、所述下拉电路用于利用gnd将存储节点维持在稳定的低电平;

5、所述存取管电路用于控制存储单元数据的读取和写入;

6、所述字线用于利用不同的电位控制所述存取管电路的导通状态,确定所述存取管电路的开闭;

7、所述位线用于控制对单元进行读取或写入的具体数据。

8、在一种可能的实现方式中,所述存取管电路用于控制存储单元数据的读取和写入,包括:

9、所述存取管电路被激活时,所述存储单元进行读取和写入操作;

10、所述存取管电路被关闭时,所述存储单元进行保持操作。

11、在一种可能的实现方式中,所述上拉电路,包括:pmos1、pmos2、pmos3和pmos4;

12、所述pmos1的源极与vdd端连接,漏极与nmos1的漏极连接,栅极与所述下拉电路中nmos3的栅极连接;

13、所述pmos2的源极与vdd端连接,漏极与nmos2的漏极连接,栅极与所述下拉电路中nmos4的栅极连接;

14、所述pmos3的源极与vdd端连接,漏极与所述下拉电路中nmos5的漏极连接,栅极与所述下拉电路中nmos6的漏极连接;

15、所述pmos4的源极与vdd端连接,漏极与所述下拉电路中nmos6的漏极连接,栅极与所述下拉电路中nmos5的漏极连接。

16、在一种可能的实现方式中,所述下拉电路,包括:nmos1、nmos2、nmos3、nmos4、nmos5和nmos6;

17、所述nmos1的源极与所述nmos3的漏极连接,漏极与所述上拉电路中的pmos1的漏极连接,栅极与所述上拉电路中的pmos1的栅极连接;

18、所述nmos2的源极与所述nmos4的漏极连接,漏极与所述上拉电路中的pmos2的漏极连接,栅极与所述上拉电路中的pmos4的栅极连接;

19、所述nmos3的源极与gnd连接,漏极与所述nmos5的栅极连接,栅极与所述上拉电路中pmos1的栅极连接;

20、所述nmos4的源极与gnd连接,漏极与所述nmos6的栅极连接,栅极与所述上拉电路中pmos2的栅极连接;

21、所述nmos5的源极与gnd连接,漏极与所述上拉电路中的pmos3的漏极连接,栅极与所述nmos3漏极连接;

22、所述nmos6的源极与gnd连接,漏极与所述上拉电路中的pmos4的漏极连接,栅极与所述nmos4的漏极。

23、在一种可能的实现方式中,所述存取管电路,包括:nmos7和nmos8;

24、所述nmos7的源极与位线bl连接,漏极与所述下拉电路中的nmos3的漏极连接,栅极与字线wl连接;

25、所述nmos8的源极与位线bln连接,漏极与所述下拉电路中的nmos4的漏极连接,栅极与字线wl连接。

26、在一种可能的实现方式中,所述位线,包括:位线bl和反位线bln;

27、所述位线bl与所述存取管电路中nmos7的源极连接;

28、所述bln与所述存取管电路中nmos8的源极连接。

29、在一种可能的实现方式中,所述字线连接所述存取管电路中nmos7和nmos8的栅极。

30、本发明中提供的一个或多个技术方案,至少具有如下技术效果或优点:

31、本发明提供的一种该新型抗辐照加固sram单元电路通过增加额外的nmos1、nmos2、nmos5、nmos6、pmos3和pmos4晶体管使得加固单元具备两个冗余节点s0和s1,当敏感节点(q、qn、s0和s1节点之一)遭受高能粒子轰击发生储存数据翻转现象时,电路可以通过其它未受到影响节点的电压反馈机制将其恢复至原来的正确逻辑值,完成逻辑状态出错到自恢复的容错过程,有效提高sram单元抵抗单粒子效应的能力。

技术特征:1.一种新型抗辐照加固sram单元电路,其特征在于,包括:上拉电路、下拉电路、存取管电路、字线和位线;

2.根据权利要求1所述的新型抗辐照加固sram单元电路,其特征在于,所述存取管电路用于控制存储单元数据的读取和写入,包括:

3.根据权利要求1所述的新型抗辐照加固sram单元电路,其特征在于,所述上拉电路,包括:pmos1、pmos2、pmos3和pmos4;

4.根据权利要求1所述的新型抗辐照加固sram单元电路,其特征在于,所述下拉电路,包括:nmos1、nmos2、nmos3、nmos4、nmos5和nmos6;

5.根据权利要求1所述的新型抗辐照加固sram单元电路,其特征在于,所述存取管电路,包括:nmos7和nmos8;

6.根据权利要求1所述的新型抗辐照加固sram单元电路,其特征在于,所述位线,包括:位线bl和反位线bln;

7.根据权利要求1所述的新型抗辐照加固sram单元电路,其特征在于,所述字线连接所述存取管电路中nmos7和nmos8的栅极。

技术总结本发明提供一种新型抗辐照加固SRAM单元电路,解决了现有技术中器件的尺寸和间距显著缩小,且SRAM单元的临界电荷下降的问题,该电路包括:上拉电路、下拉电路、存取管电路、字线和位线;上拉电路用于利用VDD将存储节点维持在稳定的高电平;下拉电路用于利用GND将存储节点维持在稳定的低电平;存取管电路用于控制存储单元数据的读取和写入;字线用于利用不同的电位控制存取管电路的导通状态,确定存取管电路的开闭;位线用于控制对单元进行读取或写入的具体数据;实现了利用电路中未受到影响节点的反馈作用将其恢复至正确逻辑值,完成逻辑状态出错到自恢复的容错过程,有效提高SRAM单元抵抗单粒子效应的能力。技术研发人员:吕红亮,杨曹振,严思璐受保护的技术使用者:西安电子科技大学技术研发日:技术公布日:2024/4/22本文地址:https://www.jishuxx.com/zhuanli/20240731/184313.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 YYfuon@163.com 举报,一经查实,本站将立刻删除。

下一篇

返回列表