基于ReRAM的FPGA用非易失性配置RAM的制作方法

- 国知局

- 2024-07-31 19:47:37

本发明涉及一种非易失性配置ram,尤其是一种基于reram的fpga用非易失性配置ram。

背景技术:

1、fpga(field programmable gate array,现场可编程逻辑门阵列)是一种硬件可编程逻辑器件,除了应用于移动通信、数据中心等领域,还广泛应用于集成电路设计中的原型验证,能够有效验证电路功能的正确性,同时加快电路设计速度。

2、对采用常规易失性sram的fpga,存在掉电信息丢失、上电数据重新加载和sram单粒子翻转等缺点,可靠性较低,难以应用在航空等粒子干扰较强,且又对可靠性有较高要求的领域。

3、采用flash技术实现的fpga,解决了上述的难点,但是由于flash工艺需要高压器件来实现擦除和编程电路,因此,基于flash技术的fpga很难与最先进的cmos工艺兼容,尺寸很难做到40nm以下,这就限制了flash型fpga的规模和速度,难以满足大数据量处理能力的应用需求。

技术实现思路

1、本发明的目的是克服现有技术中存在的不足,提供一种基于reram的fpga用非易失性配置ram,其可配置得到非易失性ram,与现有cmos工艺兼容,可有效提高fpga的规模和速度。

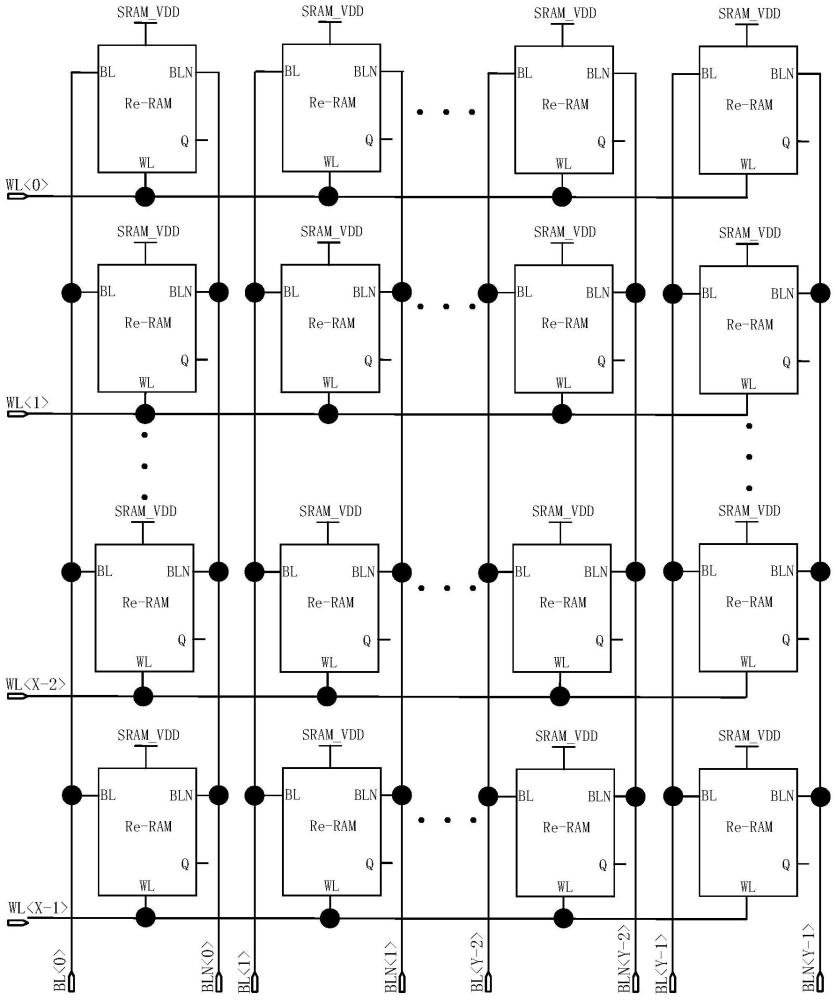

2、按照本发明提供的技术方案,一种基于reram的fpga用非易失性配置ram,所述非易失性配置ram至少包括reram阵列,所述reram阵列包括若干reram单元,其中,

3、对reram阵列中的任一reram单元,包括用于数据存储的可变阻值电阻r0以及与所述可变阻值电阻r0适配连接的存储控制电路,其中,可变阻值电阻r0的电阻状态受加载到所述可变阻值电阻r0上的可变电阻控制电压控制;

4、同一行的reram单元连接至同一字线wl,同一列的reram单元连接至同一位线bl以及同一反位线bln;

5、对一reram单元,将一预设的可变电阻控制电压加载到所述reram单元内可变阻值电阻r0,且基于字线wl以及位线bl配置所对应适配连接reram单元的操作状态,其中,所述操作状态至少包括电形成、存储操作、读取操作以及恢复操作;

6、利用一reram单元进行数据存储前,基于与所述reram单元连接的字线wl以及位线bl配置对所述reram单元内进行电形成,以使得所述可变阻值电阻r0从高阻状态切换为低阻状态;

7、对reram单元的操作状态为存储操作时,通过位线bl以及反位线bln将待存储的数据传输至reram单元内,并配置可变阻值电阻r0的电阻状态,以基于所配置所述可变阻值电阻r0的电阻状态控制数据的存储;

8、对reram单元的操作状态为读取操作时,通过位线bl以及反位线bln读取可变阻值电阻r0的存储状态;

9、对reram单元的操作状态为恢复操作时,配置加载到可变阻值电阻r0的可变电阻控制电压,并通过位线bl以及反位线bln确定可变阻值电阻r0的存储状态。

10、所述可变阻值电阻r0呈mim结构,包括:

11、可变电阻第一金属电极板,用于形成可变阻值电阻r0的上电极te;

12、可变电阻第二金属电极板,用于形成可变阻值电阻r0的下电极be;

13、开关介质层,位于可变电阻第一金属电极板与可变电阻第二金属电极板之间,包括hfo2层以及位于所述hfo2层上的ti层,其中,hfo2层位于可变电阻第二金属电极板上,ti层与可变电阻第一金属电极板接触;

14、在启用可变阻值电阻r0进行数据存储前,对所述可变阻值电阻r0进行电形成。

15、所述存储控制电路包括:

16、反相器单元,具有互为反相的反相器第一输出端以及反相器第二输出端,其中,所述反相器单元的反相器第一输出端与第一开关管以及第三开关管适配连接,反相器单元的反相器第二输出端与第二开关管适配连接,且基于反相器单元的反相器第一输出端形成reram单元的信号开关控制端q;

17、第一开关管,与位线bl以及字线wl适配连接,基于字线wl配置所述第一开关管导通时,位线bl与反相器单元的反相器第一输出端以及第三开关管连接;

18、第二开关管,与反位线bln以及字线wl适配连接,基于字线wl配置第二开关管导通时,反位线bln与反相器单元的反相器第二输出端连接;

19、第三开关管,与可变阻值电阻r0的上电极te适配连接,其中,第三开关管的开关状态受控制信号ctrl1控制,可变阻值电阻r0的下电极be接控制信号ctrl2;其中,基于控制信号ctrl1、控制信号ctrl2配置加载到可变阻值电阻r0上的可变电阻控制电压。

20、所述反相器单元包括pmos管p0、pmos管p1、nmos管n0以及nmos管n1,其中,

21、pmos管p0的漏极端、pmos管p1的漏极端均与电压sram_vdd连接;

22、pmos管p0的源极端与nmos管n0的漏极端、pmos管p1的栅极端以及nmos管n1的栅极端连接,以形成反相器单元的反相器第一输出端;

23、pmos管p1的源极端与nmos管n1的漏极端、pmos管p0的栅极端以及nmos管n0的栅极端连接,以形成反相器单元的反相器第二输出端;

24、第一开关管、第二开关管以及第三开关管均采用nmos管时,反相器单元的反相器第一输出端与第一开关管的源极端以及第三开关管的源极端连接,且反相器单元的反相器第二输出端与第二开关管的源极端连接。

25、对reram单元进行电形成后,且在进行存储操作前,还包括对reram单元进行预处理操作,其中,

26、所述预处理操作包括写“0”操作、复位操作、读操作、写“1”操作、置位操作、关闭操作和/或恢复操作。

27、还包括与reram阵列适配的信号开关阵列,其中,所述信号开关阵列包括若干存储数据加载单元;

28、所述存储数据加载单元包括信号开关选择器以及与所述信号开关选择器适配的信号加载驱动电路;

29、通过信号开关控制端q配置信号开关选择器的选通状态,以通过信号开关选择器将加载到所述信号开关选择器的n个信号数据选通,并通过信号加载驱动电路将选通的信号数据输出。

30、还包括与reram阵列适配的字线电路,其中,

31、字线电路的输出端与reram阵列的字线wl呈一一对应连接;

32、字线电路包括依次连接的地址寄存器、地址译码器以及字线输出驱动电路;

33、所述字线输出驱动电路包括若干字线输出单元,一字线输出单元的输出端与reram阵列的一字线wl对应连接;

34、所述字线输出单元包括字线输出电平转换电路以及与所述字线输出电平转换电路适配连接的与非门,与非门的一输入端与字线输出电平转换电路的输出端连接,与非门的另一输入端接收使能信号en1;

35、字线输出电平转换电路的电源端、与非门的电源端均接第一电荷泵输出的电压cp1。

36、还包括与reram阵列适配的位线电路,其中,

37、所述位线电路包括数据寄存器以及与所述数据寄存器适配的位线输出驱动电路;

38、位线输出驱动电路包括若干位线输出单元,其中,一位线输出单元的输出端分别与一reram单元的位线bl以及所述reram单元的反位线bln适配连接;

39、位线输出单元包括与位线bl对应的位线输出第一子单元以及反位线bln对应的位线输出第二子单元;

40、位线输出第一子单元包括位线输出第一电平转换电路以及与所述位线输出第一电平转换电路适配连接的第一或非门,第一或非门的输出端与reram单元的位线bl适配连接;

41、位线输出第二子单元包括位线输出第二电平转换电路以及与所述位线输出第二电平转换电路适配连接的第二或非门,第二或非门的输出端与reram单元的反位线bln适配连接;

42、第一或非门、第二或非门相应的输入端还接收时钟脉冲电路产生的时钟脉冲信号;

43、位线输出第一电平转换电路、位线输出第二电平转换电路、第一或非门以及第二或非门相应的电源端接第二电荷泵产生的电压cp2。

44、所述时钟脉冲电路包括依次连接的振荡器、计数器、编码器、脉冲处理电路以及脉冲生成电平转换电路,其中,

45、计数器还接收使能信号en2;

46、脉冲生成电平转换电路的输出端与第一或非门、第二或非门相应的输入端连接,以向第一或非门、第二或非门相应的输入端加载时钟脉冲信号。

47、所述第二电荷泵包括若干并联的电压产生电路,其中,

48、对任一电压产生电路,包括若干依次级联的电压产生单元;

49、所述电压产生单元包括电压生成第一nmos管、电压生成第二nmos管以及电压生成第三nmos管;

50、电压生成第一nmos管的栅极端与电压生成第二nmos管的源极端、第二电容的一端以及电压生成第三nmos管的栅极端连接;

51、电压生成第二nmos管的栅极端与电压生成第一nmos管的源极端、第一电容的一端连接;

52、电压生成第一nmos管的漏极端、电压生成第二nmos管的漏极端与电压生成第三nmos管的漏极端相互连接,以形成电压产生单元的第一内节点;

53、电压生成第三nmos管的源极端与第三电容的一端连接;

54、第一电容的另一端、第二电容的另一端以及第三电容的另一端分别接收相应的时钟信号。

55、本发明的优点:对reram单元采用可变阻值电阻r0以及存储控制电路,基于reram技术的非挥发性fpga可以与最先进的cmos工艺兼容,提高了fpga的系统规模、速度和可靠性;

56、reram为非挥发性存储,掉电后信息不丢失,减少了fpga外围的配置电路,可简化了板级设计和外围空间以及可减低系统的重量;

57、基于reram技术的非挥发性fpga上电启动速度快,无需从外围的flash存储器中读取数据再写入到配置ram中,也即基于reram技术的fpga能够快速的进行用户逻辑的工作状态;

58、基于reram技术的fpga在上电过程中,配置ram不会出现像sram型fpga在清零前配置ram中的值会出现随机状态,且不会导致fpga的上电启动大电流,可省去门控配置,节省了芯片的面积。

59、基于reram技术的fpga抗辐射性能要明显优于sram型fpga,sram型fpga中的配置sram容易被单粒子打翻,而基于reram技术的fpga中,配置ram由于信号开关控制端q通过pmos管p0、pmos管1连接了reram单元到sram_vdd的通路,因此,信号开关控制端q不容易受到单粒子的影响。

60、基于reram技术的fpga中,配置ram中用于lut(查找表)的sram,同样可以像sram型fpga的中用法一样,作为分布式sram来使用,并且在系统掉电前可以将信息保存到reram中。

本文地址:https://www.jishuxx.com/zhuanli/20240731/184064.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 YYfuon@163.com 举报,一经查实,本站将立刻删除。

下一篇

返回列表