一种片上大容量双端口同步存储器的制作方法

- 国知局

- 2024-07-31 19:47:36

本发明涉及一种片上大容量双端口同步存储器,特别是涉及一种片上4k×72规模的双端口同步读写存储器,可作为片上海量数据处理传输过程的存储缓冲,属于集成电路领域。

背景技术:

1、作为电子系统中的重要资源,存储器在电路中通常扮演着输入数据缓冲、中间数据暂存、输出结果存储与访问等角色。为了确保处理器、ad\da转换器、高速接口管理器等电路系统的正常工作,通常需要配置大量存储器,以实现电路的高速、高效、大规模的数据处理任务,是确保高性能电路系统正常工作的重要电路模块。

2、随着5g技术、人工智能、大数据的飞速进步,需要性能更好、运行速度更快的集成电路和电子系统承载。这种急迫切的需求促使了集成电路工艺的高速发展,主要体现在集成电路上单个晶体管尺寸不断缩小。得益于器件尺寸的持续缩减,集成电路表现出了功耗更低、速度更快、价格更低的优势。片上静态存储器(sram)作为集成电路的重要组成部分,其深刻的受到工艺尺寸缩减所带来的好处。然而仅依赖于器件性能改善从而提高存储器的性能,其存储容量、端口控制等功能难以跟得上片上数据处理机构的需求,因此在新工艺节点下存储器的大容量、多端口读写设计方法一直是存储器领域的热点研究问题之一。

技术实现思路

1、本发明的技术解决问题是:克服现有技术的不足,提供一种大容量、可以双端口同步读写的片上存储器,能够实现4k×72的存储容量和读写宽度,并可以内部产生两个端口的时序控制信号实现双端口读写,同时还具有存储阵列时序反馈路径,能够实时测量存储阵列的最大工作频率,保证存储器不会因时钟频率过高出现时序紊乱的现象,确保了高速读写特性和存储数据的可靠性,满足集成电路系统对于存储器高速、大容量、双端口灵活读写等方面的需求。

2、本发明的技术解决方案是:

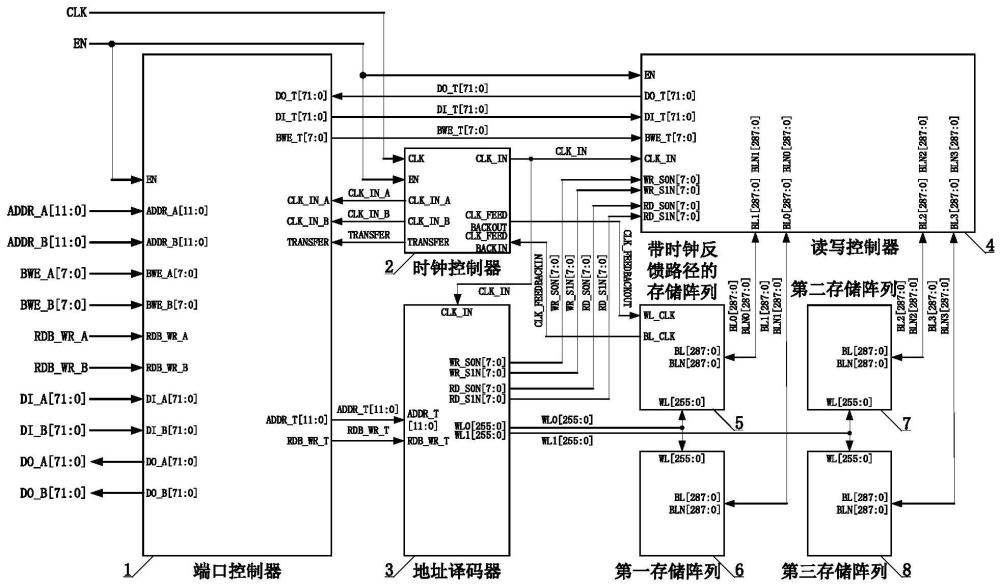

3、一种片上大容量双端口同步存储器,包括端口控制器、时钟控制器、地址译码器、读写控制器、带时钟反馈路径的存储阵列、第一存储阵列、第二存储阵列、第三存储阵列;

4、端口控制器:接收两个外部端口的地址信号、字节宽度写使能信号、读写控制信号、输入数据信号,并根据时钟控制器发出的内部时钟信号将其转换为内部地址信号、内部字节宽度写使能信号、内部读写控制信号、内部输入数据信号,将内部地址信号、内部读写控制信号发送至地址译码器,将内部读写控制信号、内部输入数据信号、内部字节宽度写使能信号发送至读写控制器;同时将读写控制器输出的内部输出数据信号转换为对外数据输出信号并输出;

5、时钟控制器:用于接收外部时钟和使能信号,产生时钟反馈信号输出至带时钟反馈路径的存储阵列;根据带时钟反馈路径的存储阵列反馈的延时后的时钟信号,产生内部时钟信号驱动存储器其他模块运行;

6、地址译码器:根据内部时钟信号将内部地址信号、读写控制信号转换为字线驱动信号和读写控制信号,所述字线驱动信号传输至四个存储阵列用来控制字线打开,读写控制信号传输至读写控制器用来控制读写单元执行写或读操作;

7、读写控制器:接收内部读写控制信号、内部时钟信号、内部输入数据信号、内部字节宽度写使能信号,根据信号状态将内部输入数据信号写入存储阵列,或者将存储阵列中的数据读出并转换为内部输出数据信号发送至端口控制器;

8、第一存储阵列、第二存储阵列、第三存储阵列:根据字线打开情况和位线数据传输情况,将位线上的数据存入存储单元,或将存储单元内的数据输出至位线;

9、带时钟反馈路径的存储阵列:根据字线打开情况和位线数据传输情况,将位线上的数据存入存储单元,或将存储单元内的数据输出至位线;接收时钟反馈信号,向时钟控制器反馈延时后的时钟信号。

10、优选的,存储器根据外部时钟信号clk、外部使能信号en、a端口读写控制信号rdb_wr_a、b端口读写控制信号rdb_wr_b的状态,将a端口输入数据信号di_a[71:0]写入a端口地址addr_a[11:0]对应的存储单元中,将b端口输入数据信号di_b[71:0]写入b端口地址addr_b[11:0]对应的存储单元中;或将a端口地址addr_a[11:0]对应的存储单元中的数据读出,通过a端口对外数据输出信号do_a[71:0]输出,将b端口地址addr_b[11:0]对应的存储单元中的数据读出,通过b端口对外数据输出信号do_b[71:0]输出;

11、en为1时进行读写操作,en为0时不能进行任何操作;写操作或读操作需要在clk的上升沿进行;

12、rdb_wr_x为1时为写操作,为0时为读操作;bwe_x[7:0]分别为x端口的字节宽度写使能信号,用来实现x端口在写操作时对应字节是否写入;其中x为a或b;

13、控制关系为:在写操作开始时,若bwe_x[0]为1,则di_x[7:0]、di_x[64]写入存储器;若bwe_x[1]为1,则di_x[15:8]、di_x[65]写入存储器;若bwe_x[2]为1,则di_x[23:16]、di_x[66]写入存储器;若bwe_x[3]为1,则di_x[31:24]、di_x[67]写入存储器;若bwe_x[4]为1,则di_x[39:32]、di_x[68]写入存储器;若bwe_x[5]为1,则di_x[47:40]、di_x[69]写入存储器;若bwe_x[6]为1,则di_x[55:48]、di_x[70]写入存储器;若bwe_x[7]为1,则di_x[63:56]、di_x[71]写入存储器。

14、优选的,端口控制器输入信号包括外部使能信号en、a端口地址addr_a[11:0]、b端口地址addr_b[11:0]、a端口字节宽度写使能信号bwe_a[7:0]、b端口字节宽度写使能信号bwe_b[7:0]、a端口读写控制信号rdb_wr_a、b端口读写控制信号rdb_wr_b、a端口输入数据信号di_a[71:0]、b端口输入数据信号di_b[71:0]、内部输出数据信号do_t[71:0]、a端口内部时钟信号clk_in_a、b端口内部时钟信号clk_in_b、a\b端口切换信号transfer,其中en、addr_a[11:0]、addr_b[11:0]、bwe_a[7:0]、bwe_b[7:0]、rdb_wr_a、rdb_wr_b、di_a[71:0]、di_b[71:0]用于连接外部信号,do_t[71:0]、clk_in_a、clk_in_b、transfer用于连接内部信号;

15、端口控制器输出信号包括a端口对外数据输出信号do_a[71:0]、b端口对外数据输出信号do_b[71:0]、内部输入数据信号di_t[71:0]、内部字节宽度写使能信号bwe_t[7:0]、内部地址信号addr_t[11:0]、内部读写控制信号rdb_wr_t,其中do_a[71:0]、do_b[71:0]连接外部信号,di_t[71:0]、bwe_t[7:0]、addr_t[11:0]、rdb_wr_t连接内部信号。

16、优选的,端口控制器包括锁存器lat9、lat10、lat13、lat14、lat16、lat17、lat19、lat20、lat22;二输入多路器mux12、mux15、mux18、mux21;

17、do_t[71:0]同时连接锁存器lat9、lat10的d端,en同时连接锁存器lat9、lat10的cd端,clk_in_a连接锁存器lat9的cp端,clk_in_b连接锁存器lat10的cp端,锁存器lat9的q端连接do_a[71:0],锁存器lat10的q端连接do_b[71:0];

18、di_a[71:0]连接lat11的d端,clk_in_a连接锁存器lat11的cp端,en连接锁存器lat11、lat13的cd端,锁存器lat11的q端连接二输入多路器mux12的a1端,di_b[71:0]连接二输入多路器mux12的a0端,transfer连接二输入多路器mux12的s端,二输入多路器mux12的z端连接锁存器lat13的d端,clk_in_b连接锁存器lat13的cp端,锁存器lat13的q端连接di_t[71:0];

19、addr_a[11:0]连接锁存器lat14的d端,clk_in_a连接锁存器lat14的cp端,en连接锁存器lat14、lat16的cd端,锁存器lat14的q端连接二输入多路器mux15的a1端,addr_b[11:0]连接二输入多路器mux15的a0端,transfer连接二输入多路器mux15的s端,二输入多路器mux15的z端连接锁存器lat16的d端,clk_in_b连接锁存器lat16的cp端,锁存器lat16的q端连接addr_t[11:0];

20、bwe_a[7:0]连接锁存器lat17的d端,clk_in_a连接锁存器lat17的cp端,en连接锁存器lat17、lat19的cd端,锁存器lat17的q端连接二输入多路器mux18的a1端,bwe_b[7:0]连接二输入多路器mux18的a0端,transfer连接二输入多路器mux18的s端,二输入多路器mux18的z端连接锁存器lat19的d端,clk_in_b连接锁存器lat19的cp端,锁存器lat19的q端连接bwe_t[7:0];

21、rdb_wr_a连接锁存器lat20的d端,clk_in_a连接锁存器lat20的cp端,en连接锁存器lat20、lat22的cd端,锁存器lat20的q端连接二输入多路器mux21的a1端,rdb_wr_b连接二输入多路器mux21的a0端,transfer连接二输入多路器mux21的s端,二输入多路器mux21的z端连接锁存器lat22的d端,clk_in_b连接锁存器lat22的cp端,锁存器lat22的q端连接rdb_wr_t。

22、优选的,时钟控制器包括锁存器lat23、lat26、lat30、lat31,寄存器dff36,延时器dly24、dly25、dly27,异或门xor28,pmos管p29,同或门xnor32,反相器inv33、inv35,缓冲器buf34;

23、en连接锁存器lat23、lat26、lat30、lat31的d端,clk连接锁存器lat23的cp端和延时器dly24的输入端,延时器dly24的输出端连接锁存器lat23的cd端,锁存器lat23的q端连接锁存器lat31的cp端和异或门xor28的一个输入端,锁存器lat23的qn端连接延时器dly25的输入端;延时器dly25的输出端连接锁存器lat26的cp端和延时器dly27的输入端,延时器dly27的输出端连接锁存器lat26的cd端,锁存器lat26的q端连接xor28的另一个输入端、pmos管p29的栅极和锁存器lat30的cp端;xor28的输出端连接时钟反馈信号clk_feedbackout;延时后的时钟信号clk_feedbackin连接pmos管p29的漏极和锁存器lat30、lat31的cd端,锁存器lat30的q端连接同或门xnor32的一端和clk_in_b,锁存器lat31的q端连接同或门xnor32的另一端和clk_in_a;同或门xnor32的输出端连接缓冲器buf34的输入端和clk_in,反相器inv33的输出端连接寄存器dff36的cd端,缓冲器buf34的输出端连接寄存器dff36的cp端,寄存器dff36的q端连接transfer,qn端连接反相器inv35的输入端,反相器inv35的输出端连接寄存器dff36的d端。

24、优选的,地址译码器由字线译码器和读写控制译码器构成;

25、字线译码器根据addr_t[11:3]和clk_in,在每次时钟到来时将内部地址信号转换为字线打开信号,包括:第一字线信号wl0[255:0],第二字线信号wl1[255:0],每一个地址码对应一个字线打开的状态,其中第一字线信号wl0[255:0]连接带时钟反馈路径的存储阵列和第一存储阵列的wl[255:0]端口,第二字线信号wl1[255:0]连接第二存储阵列和第三存储阵列的wl[255:0]端口;读写控制译码器根据addr_t[6]、addr_t[2:0]、rdb_wr_t和clk_in,在每次时钟信号到来时将内部地址信号转换为位线读写控制信号,包括:第一位线写控制信号wr_s0n[7:0]、第二位线写控制信号wr_s1n[7:0]、第一位线读控制信号rd_s0n[7:0]、第二位线读控制信号rd_s1n[7:0];每个地址码对应一个位线读写控制有效的状态。

26、优选的,读写控制器由72个读写单元构成;

27、第i个读写单元的内部输入数据信号di_t端口连接端口控制器di_t[i],内部输出数据信号do_t端口分别连接端口控制器do_t[i],输入时钟clk_in端口连接时钟控制器的clk_in,en端口连接外部使能信号en,第一位线写控制端口wr_s0n[7:0]连接地址译码器的第一位线写控制信号wr_s0n[7:0],第二位线写控制端口wr_s1 n[7:0]连接地址译码器的第二位线写控制信号wr_s1 n[7:0],第一位线读控制端口rd_s0n[7:0]连接地址译码器的第一位线读控制信号rd_s0n[7:0],第二位线读控制端口rd_s1n[7:0]连接地址译码器的第二位线读控制信号rd_s1n[7:0];

28、端口控制器内部字节宽度写使能信号bwe_t[j]连接第j×8—j×8+7个读写单元的字节宽度写使能端口bwe_t,0≤j≤7,0≤i≤71;

29、当0≤i≤35时,第i个读写单元的第一位线正驱动端口bl0[7:0]连接带时钟反馈路径的存储阵列的正位线bl0[(i+1)×8-1:i×8],第二位线正驱动端口bl1[7:0]连接第一存储阵列的正位线bl1[(i+1)×8-1:i×8];当36≤i≤71时,第i个读写单元的第一位线正驱动端口bl0[7:0]连接第二存储阵列的正位线bl2[(i-35)×8-1:(i-36)×8],第二位线正驱动端口bl1[7:0]连接第三存储阵列的正位线bl3[(i+1)×8-1:i×8];

30、当0≤i≤35时,第i个读写单元的第一位线负驱动端口bln0[7:0]连接带时钟反馈路径的存储阵列的负位线bln0[(i+1)×8-1:i×8],第二位线负驱动端口bln1[7:0]连接第一存储阵列的负位线bln1[(i+1)×8-1:i×8];当36≤i≤71时,第i个读写单元的第一位线负驱动端口bln0[7:0]连接第二存储阵列的负位线bln2[(i-35)×8-1:(i-36)×8],第二位线负驱动端口bln1[7:0]连接第三存储阵列的负位线bln3[(i+1)×8-1:i×8]。

31、优选的,第一存储阵列、第二存储阵列、第三存储阵列结构相同,均包含256条字线wl[255:0],288对位线,73728个存储单元,288对位线包括正位线bl[287:0]、负位线bln[287:0],每条字线上连接288个存储单元,每对位线上连接256个存储单元,73728个存储单元以256×288的矩阵形式排布,每个存储单元能够存储一个二进制位。

32、优选的,带时钟反馈的存储阵列除包含第一存储阵列的全部结构,还额外包含一行时钟反馈行,时钟反馈行用于接收来自时钟控制器时钟反馈信号,对其进行延时处理,得到延时处理后的时钟信号反馈给时钟控制器。

33、优选的,存储单元包括nmos管n214、n217、反相器inv215、inv216;位线端口wl连接nmos管n214、n217的栅极,n214漏极连接正位线bl、负位线bln;nmos管n214的源极连接反相器inv215的输入端和反相器inv216的输出端;nmos管n217的源极连接反相器inv216的输入端和反相器inv215的输出端。

34、优选的,时钟反馈行包括6个时钟反馈单元、250个填充单元;

35、6个时钟反馈单元的字线端口wl连接时钟反馈信号clk_feedbackout,位线端口bl连接延时后的时钟信号clk_feedbackin;

36、250个填充单元的输出端连接延时后的时钟信号clk_feedbackin。

37、优选的,时钟反馈单元包括nmos管n220、n221、反相器inv218、inv219;wl连接n220的栅极,n220的漏极连接反相器inv218的输出端,源极连接bl;nmos管n221的漏极连接反相器inv219的输出端,inv218、inv219的输入端接高电平。

38、优选的,填充单元由nmos管n224、n225、反相器inv222、inv223构成,nmos管n224的漏极连接反相器inv222的输出端,nmos管n225的漏极连接反相器inv223的输出端,inv222、inv223的输入端接高电平。

39、上述方案的原理是:时序控制器接收时钟信号,产生时钟反馈信号,时钟反馈信号经由带时钟反馈路径的存储阵列返回时钟控制器,确定了存储阵列的最大工作延时,时钟控制器根据最大工作延时产生内部时序信号,驱动端口控制器、读写控制器、地址译码器工作;端口控制器接收两个外部端口的地址、字节宽度写使能、读写控制、输入数据信号,根据时钟信号将外部信号转换为可驱动存储器读写操作的内部信号并传输,同时根据时钟信号将内部输出数据信号转换为输出数据信号并输出;地址译码器接收内部地址信号,根据时钟信号将其转换为字线打开信号和读写控制信号并传输;读写控制器时钟信号、读写控制信号,将内部输入数据信号写入存储阵列,或将存储阵列内的数据读出并传输。所有电路模块相互连接配合,完成了存储器在高频时钟下的正常读写功能。

40、本发明与现有技术相比的优点在于:

41、(1)本发明在新工艺节点下实现了一种片上大容量双端口同步存储器,实现了72位的读写宽度,4096个读写深度,实现了片上大容量数据存储,为海量数据吞吐和高速数据处理应用提供了实现条件。

42、(2)本发明实现了在单个时钟输入端口的条件下,内部自动测量存储阵列的最大工作频率,自动生成两个端口的控制时序,实现了双端口同步读写,具有高速工作、灵活读写的特性。

本文地址:https://www.jishuxx.com/zhuanli/20240731/184063.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 YYfuon@163.com 举报,一经查实,本站将立刻删除。

下一篇

返回列表