电流输入模拟内容可寻址存储器的制作方法

- 国知局

- 2024-07-31 19:47:35

背景技术:

1、复杂计算领域中的一个常见计算动作是向量矩阵乘法。此外,密集矩阵计算(诸如向量矩阵乘法)主导了大多数机器学习算法。然而,对于许多工作负载,尤其是在神经网络算法和线性变换(例如,离散傅立叶变换)中,向量矩阵乘法通常会大量消耗计算时间和能量。一种方法已经开始出现,其中利用忆阻器横杆来尝试改善这种与向量矩阵乘法相关联的计算繁重性。通过利用忆阻器横杆的自然电流积累方面,点积引擎(dpe)可以被设计为用于近似矩阵向量乘法的高密度、高功率效率加速器。

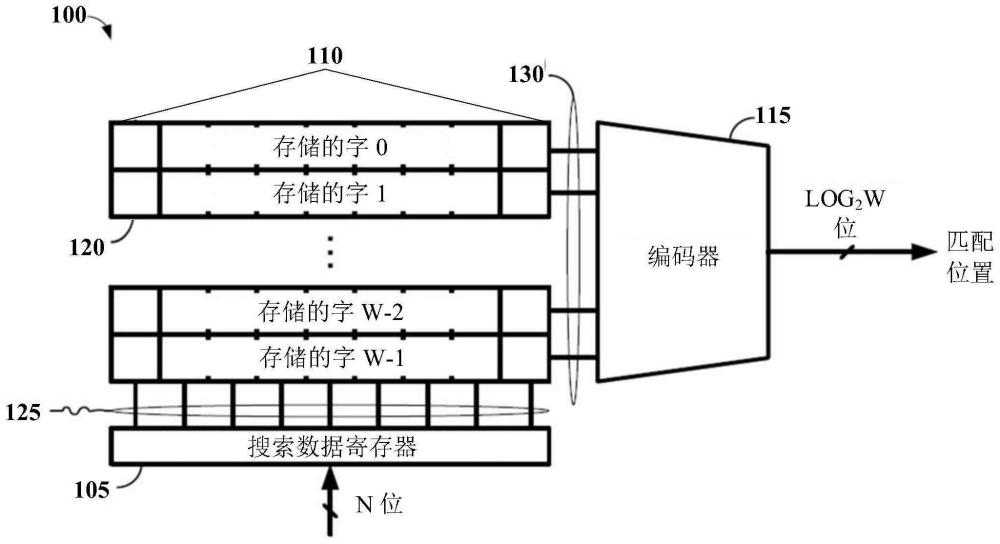

2、内容可寻址存储器(“cam”)是一种类型的计算存储器,其中存储的数据不是通过其位置而是通过其内容来被访问的。字或“标签”被输入到cam,cam在其内容中搜索该标签,当找到时,cam返回找到的内容所驻留的位置的地址。cam功能强大,效率高,速度快。然而,cam也相对较大,消耗大量功率,并且相对昂贵。这些缺点限制了它们在选定应用中的适用性,在这些应用中,它们的功率、效率和速度足以胜过它们的尺寸、成本和功耗。尽管如此,可能有一些应用直接受益于dpe和cam独特功能的结合。

技术实现思路

技术特征:1.一种电路,包括:

2.根据权利要求1所述的电路,其中,所述电路包括耦接到所述匹配线并且具有与第二晶体管相关联的栅极电压的所述第二晶体管。

3.根据权利要求1所述的电路,其中,所述匹配包括具有电荷的所述匹配线,包括在25μa和75μa范围内的值的所述电流信号,以及包括在0v和0.05v范围内的值的与所述第二晶体管相关联的所述栅极电压。

4.根据权利要求1所述的电路,其中,所述电路包括第一忆阻器和第二忆阻器。

5.根据权利要求4所述的电路,其中,所述匹配包括具有电荷的所述匹配线,以及在由所述第一忆阻器和所述第二忆阻器设置的模拟值范围内的所述输入信号。

6.根据权利要求1所述的电路,其中,不匹配包括所述匹配线被放电,包括在0.05μa和0.5μa范围内的值的所述电流信号,以及包括在1v和10v范围内的值的与所述第二晶体管相关联的栅极电压。

7.根据权利要求6所述的电路,其中,当所述输入信号基于所述输入信号产生不匹配时,所述电路在所述匹配线上输出已经放电的信号。

8.根据权利要求1所述的电路,其中,所述输入线耦接到点积引擎(dpe)电路的输出线,所述输出线接收所述电流信号作为来自所述dpe电路的输出。

9.一种电路,包括:

10.根据权利要求9所述的电路,其中,所述dpe电路包括以行和列排列的多个电阻存储器元件的忆阻器交叉矩阵。

11.根据权利要求10所述的电路,其中,所述多个电阻存储器元件确定矩阵乘法值,并且进一步其中所述忆阻器交叉矩阵包括多列输出线以收集从所述电阻存储器元件输出的所有电流,每列上所收集的电流等于相对应的矩阵乘法值。

12.根据权利要求11所述的电路,其中,所述ci-acam阵列包括多个ci-acam电路。

13.根据权利要求12所述的电路,其中,所述多个ci-acam电路中的每一个耦接到所述忆阻器交叉矩阵的多个列中的一列。

14.根据权利要求13所述的电路,其中,所述多个ci-acam电路中的每一个包括耦接到晶体管的输入线。

15.根据权利要求14所述的电路,其中,所述多个ci-acam电路的每条输入线接收所述忆阻器交叉矩阵的输出线的每个相对应耦接的列上的所收集的电流。

16.一种方法,包括:

17.根据权利要求16所述的方法,其中,所述电路块包括点积引擎(dpe)电路,并且所述附加电路块包括电流输入模拟内容可寻址存储器(ci-acam)阵列电路。

18.根据权利要求17所述的方法,其中,所述(dpe)电路包括具有列的忆阻器交叉矩阵,并且所述ci-acam阵列电路包括多个单独的ci-acam电路,每个单独的ci-acam电路耦接到所述忆阻器交叉矩阵的相对应的一列。

19.根据权利要求18所述的方法,包括:

20.根据权利要求19所述的方法,其中,输出所述输出信号包括:

技术总结本公开涉及电流输入模拟内容可寻址存储器。提供了采用电流输入模拟内容可寻址存储器(CI‑aCAM)的系统和方法。CI‑aCAM特别构造为aCAM,允许输入到aCAM单元中的模拟信号作为电流被接收。使用所公开的CI‑aCAM还可以实现组合了两个核心模拟计算电路的更大的硬件架构,即用于矩阵乘法的点积引擎(DPE)电路和用于搜索操作的aCAM电路。例如,输出电流信号的DPE电路可以直接与CI‑aCAM的输入连接,CI‑aCAM被设计成以消除转换步骤和电路(例如,模拟到数字和电流到电压)的方式接收电流信号。通过利用CI‑aCAM,组合的DPE‑aCAM硬件架构可以实现为相当紧凑的结构。技术研发人员:C·格雷夫斯,G·佩德雷蒂受保护的技术使用者:慧与发展有限责任合伙企业技术研发日:技术公布日:2024/3/31本文地址:https://www.jishuxx.com/zhuanli/20240731/184062.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 YYfuon@163.com 举报,一经查实,本站将立刻删除。

下一篇

返回列表