基于8T-SRAM和电流镜的存内计算电路

- 国知局

- 2024-07-31 19:27:53

本发明涉及集成电路,更具体的,涉及基于8t-sram和电流镜的存内计算电路。

背景技术:

1、深度学习推动了广泛的人工智能(ai)应用,从图像分类到语音识别。人工智能边缘设备依赖高精度的本地计算进行推理操作,并依赖云计算进行训练。将其部署到边缘终端设备有如下问题,首先,大多数涉及在云端静态训练模型的应用,如果不适应用户依赖的个人数据和操作情况,就无法实现高精确度。第二,许多用户不愿意将个人数据发送到云端重新训练模型。第三,许多远程应用缺乏对云的访问,无法针对现场遇到的新情况实时进行重新训练。在这些条件下,在ai边缘设备上的学习(或芯片上的训练)是一种可取的方法。

2、但是部署到边缘设备资源有限要求网络轻量化,目前流行的大型神经网络很难部署到边缘设备中,因此轻量化网络应运而生。神经网络二值化能够最大程度地降低模型的存储占用和模型的计算量,将神经网络中原本32位浮点数参数量化至1位定点数,降低了模型部署的存储资源消耗,同时极大加速了神经网络的推断过程。

3、在二值神经网络中,卷积运算只是‘+1’和‘-1’的乘累加操作,因此衍生出了采用同或(xnor)运算替代传统卷积操作的新方法。前人提出的基于sram实现同或计算电路结构存在如下不足:

4、1、现有实现同或计算电路结构中,其bitcell主动引入了电容这一非线性器件,会影响计算结果精度;由于bitcell使用过多mos管或加入电容,增大了阵列面积,降低了单位面积下阵列的运算能力;

5、2、在电压域下由于充放电速率不匹配,导致计算位线积累结果不准确;而且未考虑传输管阈值损失影响,这也是导致计算位线积累结果不准确的一个重要原因。

技术实现思路

1、基于此,有必要针对现有基于sram实现同或计算电路结构存在单元面积偏大、计算结果误差大的问题,提供基于8t-sram和电流镜的存内计算电路。

2、本发明采用以下技术方案实现:

3、本发明提供了基于8t-sram和电流镜的存内计算电路,用于实现5bit带符号数乘以1bit权重的同或累加计算。

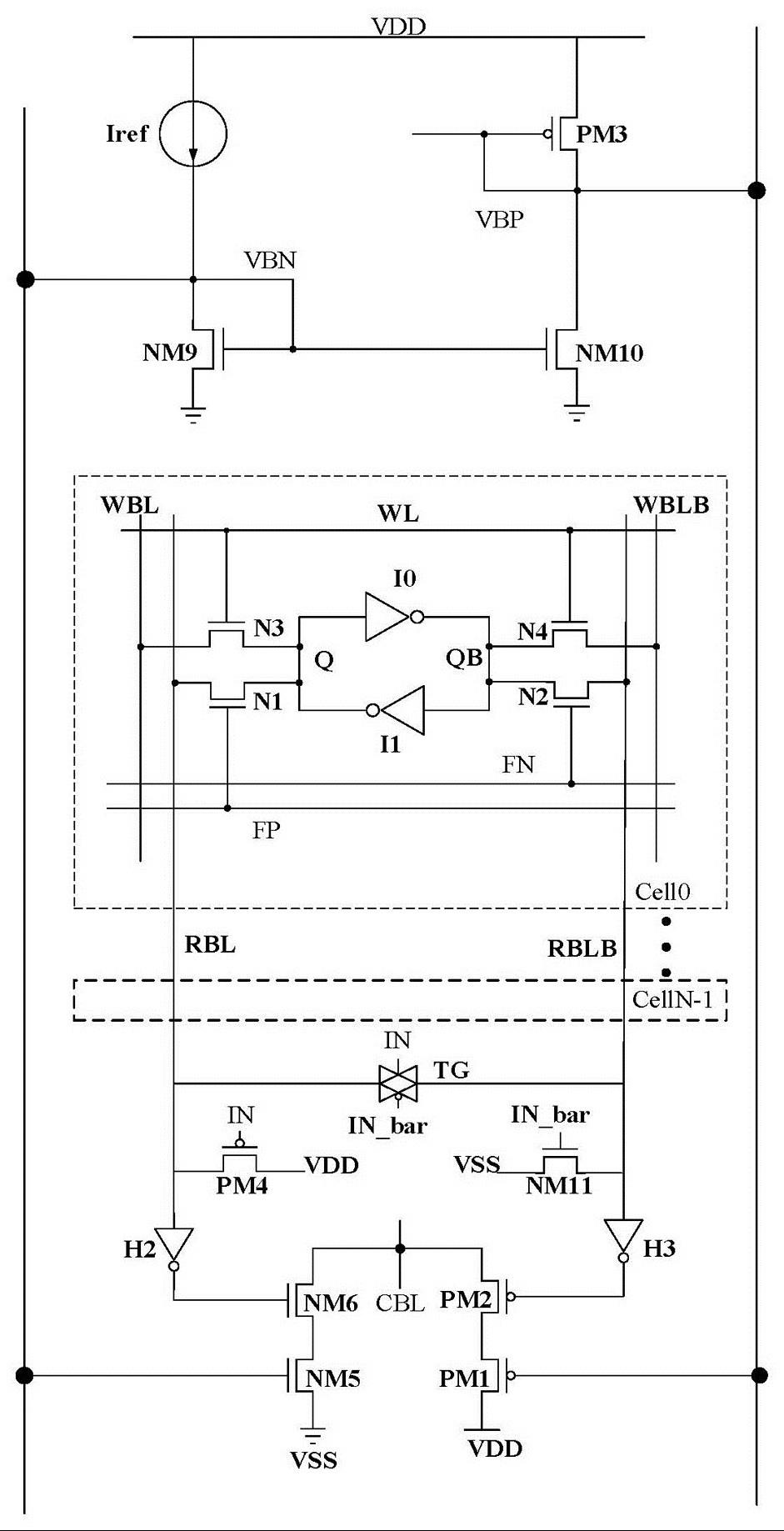

4、基于8t-sram和电流镜的存内计算电路包括:存储部、存内计算部、传输控制部、电流镜部、反相器部、关断控制部。

5、存储部包括n个8t-sram单元,n≥1。每个8t-sram单元用于存储1个1bit权重;n个8t-sram单元共用同一条位线rbl、同一条位线rblb、同一条写位线wbl、同一条写位线wblb。存内计算部用于对计算位线cbl进行充电或放电,实现5bit带符号数乘以1bit权重的同或累加计算。传输控制部用于在进行同或累加计算时将rbl、rblb连通,在不计算时将rbl、rblb断开。电流镜部用于复制参考电流源iref,使计算位线cbl在充电或放电时通过的电流均等于iref。反相器部将存内计算部与rbl、rblb连接,用于对rbl或rblb的电平进行反相输出。关断控制部用于在不计算时关断存内计算部。

6、在进行同或累加计算时,5bit带符号数分成1bit符号位和4bit无符号数;每次开启一个8t-sram单元、并向该8t-sram单元输入1bit符号位,同时向传输控制部输入4bit无符号数;存内计算部依据该8t-sram单元存储的1bit权重及输入的1bit符号位、传输控制部输入的4bit无符号数,进行5bit带符号数乘以1bit权重的计算,对计算位线cbl进行相应时长的充电或放电,实现将计算结果累加到计算位线cbl上。

7、该种基于8t-sram和电流镜的存内计算电路的实现根据本公开的实施例的方法或过程。

8、与现有技术相比,本发明具备如下有益效果:

9、1,本发明提供了基于8t-sram和电流镜的存内计算电路,一方面将1bit权重存储在8t-sram单元内,另一方面将5bit带符号数分为1bit符号位和4bit无符号数两部分、并分别输入到8t-sram单元、传输控制部,从而在近存内计算的方式下实现5bit带符号数与1bit权重相乘,并进而在计算位线cbl上实现同或累加。

10、2,本发明的存内计算电路无需对8t-sram结构进行修改,没有引入电容等非线性器件,可以保证计算结果精度,避免单元面积变大。

11、3,本发明采用电流镜复制参考电流源iref,使存内计算部进行充放电时电流均等于iref,使充放电速度相等,可以极大程度减少充放电非线性,保证计算结果的准确性;此外,关断控制部在不计算时,将存内计算部的充放电通路完全关断,从而保证计算位线cbl零泄露。

技术特征:1.基于8t-sram和电流镜的存内计算电路,其用于实现5bit带符号数乘以1bit权重的同或累加计算;其特征在于,

2.根据权利要求1所述的基于8t-sram和电流镜的存内计算电路,其特征在于,所述8t-sram单元包括:

3.根据权利要求2所述的基于8t-sram和电流镜的存内计算电路,其特征在于,n=8。

4.根据权利要求2或3所述的基于8t-sram和电流镜的存内计算电路,其特征在于,所述电流镜部包括:

5.根据权利要求4所述的基于8t-sram和电流镜的存内计算电路,其特征在于,所述传输控制部包括:

6.根据权利要求5所述的基于8t-sram和电流镜的存内计算电路,其特征在于,所述反相器部包括:

7.根据权利要求6所述的基于8t-sram和电流镜的存内计算电路,其特征在于,所述关断控制部包括:

8.根据权利要求7所述的基于8t-sram和电流镜的存内计算电路,其特征在于,在不计算时,

9.根据权利要求7所述的基于8t-sram和电流镜的存内计算电路,其特征在于,在进行5bit带符号数乘以1bit权重时,

10.根据权利要求7所述的基于8t-sram和电流镜的存内计算电路,其特征在于,所述8t-sram单元处于sram工作模式时,n1、n2关断,n3、n4导通,字线wl置为高电平,存储节点q通过n3、wbl完成数据写入或读出,存储节点qb通过n4、wblb完成数据写入或读出。

技术总结本发明涉及集成电路技术领域,更具体的,涉及基于8T‑SRAM和电流镜的存内计算电路。本发明包括存储部、存内计算部、传输控制部、电流镜部、反相器部、关断控制部。本发明一方面将1bit权重存储在8T‑SRAM单元内,另一方面将5bit带符号数分为1bit符号位和4bit无符号数两部分、并分别输入到8T‑SRAM单元、传输控制部,从而在近存内计算的方式下实现5bit带符号数与1bit权重相乘及同或累加。本发明没有引入电容等非线性器件,可以保证计算结果精度,避免单元面积变大。本发明采用电流镜复制参考电流源Iref,使存内计算部充放电速度相等,可以极大程度减少充放电非线性,保证计算结果的准确性。技术研发人员:彭春雨,李嘉祥,关立军,闫声远,王雅娜,卢文娟,赵强,李鑫,吴秀龙,周永亮受保护的技术使用者:安徽大学技术研发日:技术公布日:2024/1/15本文地址:https://www.jishuxx.com/zhuanli/20240731/182601.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 YYfuon@163.com 举报,一经查实,本站将立刻删除。

下一篇

返回列表