基于锁存交叉耦合的自控制型SRAM灵敏放大器电路、模块

- 国知局

- 2024-07-31 19:47:31

本发明涉及灵敏放大器设计,更具体的,涉及基于锁存交叉耦合的自控制型sram灵敏放大器电路,以及基于该电路设计的灵敏放大器模块。

背景技术:

1、随着可穿戴设备的普及和cmos工艺关键尺寸的不断缩小,芯片的集成度的不断提高,大容量高密度存储芯片的需求日益提升。但大容量高密度的存储阵列将在一条位线上挂载更多的存储单元,这使得位线电容不断增大,并极大增加了位线全摆幅放电的延时及其动态功耗。

2、为避免由于位线放电缓慢导致存储信息读取延时过大的问题,在静态随机存储器(sram)中,通常采用灵敏放大器来感应位线两端的电压差,并进行存储数据的快速放大和读取操作。同时,由于能够规避存储阵列中读半选问题带来的数据翻转风险,读写分离独立读位线的设计方式愈发常见,因此能够识别单端读位线电压信息变化的灵敏放大器也愈发受到青睐。

3、目前,凭借结构简单、内部通过交叉耦合正反馈能够快速放大位线压差信息的优势,锁存器型灵敏放大器被广泛应用于sram电路中。锁存型灵敏放大器以两对交叉耦合的反相器组成数据放大的核心结构结构:通过一对压控传输管控制位线信息的输入,并通过一个nmos晶体管作为电路的使能控制端和供电电流源。但由于锁存型灵敏放大器的内部为差分结构,因此会引入失调电压——即当位线压差信号小于一定电压时,锁存型灵敏放大器将无法识别或识别错误;并且随着工艺尺寸的减小,失调电压偏大,其干扰会越发严重。

4、另外,发明人检索到现有专利cn202310410709.8公开了一种基于下交叉耦合的自适应关断型sram灵敏放大器电路,该专利虽然可以降低灵敏放大器的失调电压,但其由于是内外奇数个反相器控制信号级联耦合,在位线压差接近情况下存在发生电路振荡的风险。

技术实现思路

1、基于此,有必要针对现有锁存器型灵敏放大器存在偏大的失调电压、以及现有专利存在振荡风险的问题,提供基于锁存交叉耦合的自控制型sram灵敏放大器电路、模块。

2、本发明采用以下技术方案实现:

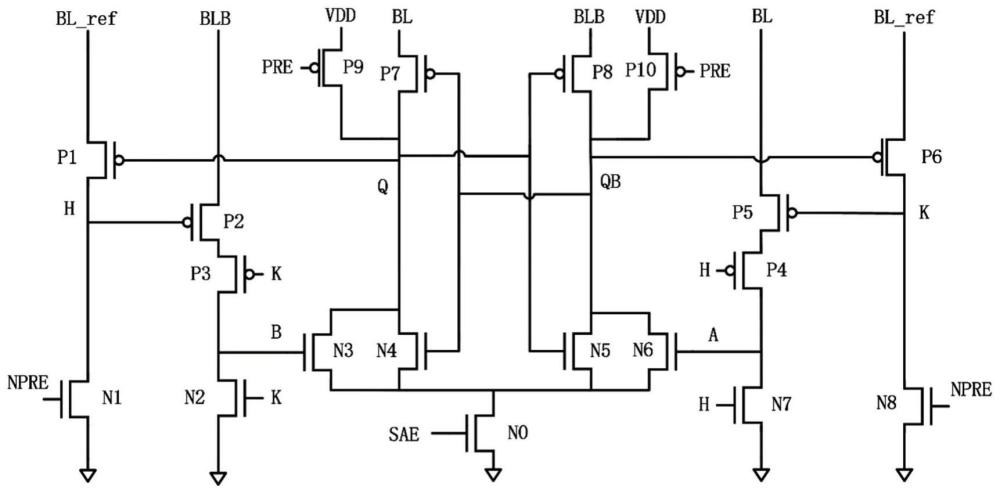

3、第一方面,本发明提供了基于锁存交叉耦合的自控制型sram灵敏放大器电路,包括:使能控制部、锁存耦合部、自控制输入部、预充电路部。

4、使能控制部用于控制灵敏放大器电路工作与否。

5、锁存耦合部用于依据位线bl、blb通过正反馈耦合快速放大输出节点q、qb的电压差。其中,锁存耦合部包括2个nmos管和2个pmos管,记为n4、n5、p7、p8。n4的栅极连接qb,n4的漏极连接q;n5的栅极连接q,n5的漏极连接qb,n5的源极与n4的源极相连接、并共同连接到使能控制部;p7的栅极连接qb,p7的源极连接bl,p7的漏极连接q;p8的栅极连接q,p8的源极连接blb,p8的漏极连接qb。

6、自控制输入部用于根据q、qb的电压变化自适应切断blb或bl对锁存耦合部的影响。其中,自控制输入部包括6个pmos管和4个nmos晶体管,记为p1、p2、p3、p4、p5、p6、n2、n3、n6、n7。p1的栅极连接q,p1的源极连接基准电压bl_ref,p1的漏极连接控制节点h;p2的栅极连接h,p2的源极连接blb;p3的栅极连接控制节点k,p3的源极连接p2的漏极,p3的漏极连接输入节点b;p4的栅极连接h,p4的漏极连接输入节点a;p5的栅极连接k,p5的源极连接bl,p5的漏极连接p4的源极;p6的栅极连接qb,p6的源极连接bl_ref,p6的漏极连接k;n2的栅极连接k,n2的源极连接vss,n2的漏极连接b;n3的栅极连接b,n3的漏极连接q,n3的源极连接使能控制部;n6的栅极连接a,n6的漏极连接qb,n6的源极连接使能控制部;n7的栅极连接h,n7的源极连接vss,n7的漏极连接a。

7、预充电路部用于在灵敏放大器电路不工作时将h、k通过vss预充到低电平,将q、qb通过vdd预充到高电平。

8、该种基于锁存交叉耦合的自控制型sram灵敏放大器电路的实现根据本公开的实施例的方法或过程。

9、第二方面,本发明公开了一种灵敏放大器模块,采用了如第一方面的基于锁存交叉耦合的自控制型sram灵敏放大器电路的电路布局。

10、该种灵敏放大器模块的实现根据本公开的实施例的方法或过程。

11、与现有技术相比,本发明具备如下有益效果:

12、1,本发明提供的基于锁存交叉耦合的自控制型sram灵敏放大器电路,是对基于电路结构层面的直接改进,其结构简洁明了、方便实现。

13、2,本发明采用自控制输入部与锁存耦合部并联的方式,减少了vdd到vss间过多晶体管串联,节约了电压余度,避免了过多mos管串联导致电压余度较小的问题,能够适应0.9v电压的工作环境;本发明采用自控制输入部,根据q、qb的电压变化,自适应控制目标位线的信号输入与非目标位线的信号关断,避免非目标位线对q、qb产生影响,从而降低失调电压和放大延时;本发明采用锁存耦合部放大电压信号,避免了反相器级联的控制方式,从而规避了现有专利的振荡风险。

技术特征:1.基于锁存交叉耦合的自控制型sram灵敏放大器电路,其特征在于,包括:

2.根据权利要求1所述的基于锁存交叉耦合的自控制型sram灵敏放大器电路,其特征在于,所述使能控制部包括1个nmos晶体管,记为n0;

3.根据权利要求2所述的基于锁存交叉耦合的自控制型sram灵敏放大器电路,其特征在于,sae为低电平时,所述灵敏放大器电路不工作;sae为高电平时,所述灵敏放大器电路工作。

4.根据权利要求2所述的基于锁存交叉耦合的自控制型sram灵敏放大器电路,其特征在于,所述预充电路部包括2个pmos管和2个nmos晶体管,记为p9、p10、n1、n8;

5.根据权利要求4所述的基于锁存交叉耦合的自控制型sram灵敏放大器电路,其特征在于,所述灵敏放大器电路与单读位线sram存储单元配合使用时,bl、blb中的其中一条连接单读位线sram存储单元的单端读位线、另一条连接bl_ref并作为基准位线使用;bl_ref连接vdd-3σ;σ表示失调电压的方差;

6.根据权利要求4所述的基于锁存交叉耦合的自控制型sram灵敏放大器电路,其特征在于,所述灵敏放大器电路未工作时,sae为低电平,n0关断;pre为低电平,npre为高电平;p9、p10导通,q预充到高电平,qb预充到高电平;n1、n8导通,h预充至低电平,k预充至低电平;

7.根据权利要求4所述的基于锁存交叉耦合的自控制型sram灵敏放大器电路,其特征在于,所述灵敏放大器电路工作时,sae为高电平,n0导通;pre为高电平,npre为低电平,p9、p10、n1、n8关断;

8.根据权利要求5所述的基于锁存交叉耦合的自控制型sram灵敏放大器电路,其特征在于,所述灵敏放大器电路工作时,sae为高电平,n0导通;pre为高电平,npre为低电平,p9、p10、n1、n8关断;

9.一种灵敏放大器模块,其特征在于,采用了如权利要求1-8任一所述的基于锁存交叉耦合的自控制型sram灵敏放大器电路的电路布局。

10.根据权利要求9所述的灵敏放大器模块,其特征在于,所述灵敏放大器模块的引脚包括:

技术总结本发明涉及灵敏放大器设计技术领域,更具体的,涉及基于锁存交叉耦合的自控制型SRAM灵敏放大器电路、模块。本发明包括:使能控制部、锁存耦合部、自控制输入部、预充电路部。本发明采用自控制输入部,根据Q、QB的电压变化,自适应控制目标位线的信号输入与非目标位线的信号关断,避免非目标位线对输出节点Q、QB产生影响,从而降低失调电压和放大延时。本发明采用锁存耦合部放大电压信号,避免了反相器级联的控制方式,从而规避了现有专利的振荡风险。本发明解决了现有锁存器型灵敏放大器存在偏大的失调电压、以及现有专利存在振荡风险的问题。技术研发人员:关立军,于天褀,卢文娟,彭春雨,蔺智挺,吴秀龙受保护的技术使用者:安徽大学技术研发日:技术公布日:2024/3/31本文地址:https://www.jishuxx.com/zhuanli/20240731/184057.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 YYfuon@163.com 举报,一经查实,本站将立刻删除。