一种一次性可编程的存储电路及存储器的制作方法

- 国知局

- 2024-07-31 19:57:51

本发明涉及集成电路领域,具体涉及一种一次性可编程的存储电路及存储器。

背景技术:

1、在集成电路中,存储器电路主要用于存储数据信息,其中一次性可编程的存储电路是一种非易失性存储器,该类存储器是基于反熔丝机理进行编程,主要通过一次性编程将数据固化到其中,编程后存储器内部数据不可以改变且一直有效,使用时能够直接快速地读取其中的数据。当前存在许多一次性可编程非易失性存储器电路,但是在在编程和读取数据时电路所需要的步骤非常繁琐,控制电路需要在编程和读取之前通过各种方式进行相关的操作准备,对于一些电路的使用来说,读写过程过于复杂。

2、因此,如何提供一种读写简单的一次性可编程的存储电路,是目前亟需解决的技术问题。

技术实现思路

1、鉴于以上所述现有技术的缺点,本发明提供一种一次性可编程的存储电路及存储器,以解决上述技术问题中的至少之一。

2、为达到上述目的及其他相关目的,本技术提供的技术方案如下。

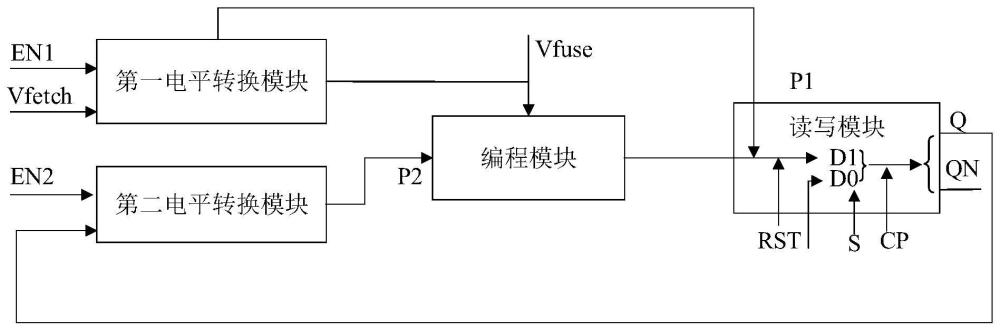

3、根据本技术实施例的一个方面,提供了一种一次性可编程的存储电路,包括:

4、编程模块,输入端接编程电压,控制端接第二控制信号;

5、第一电平处理模块,接第一使能信号及读取电压,对所述第一使能信号进行高低电平转化,得到第一控制信号,所述第一控制信号对所述编程模块的输入端所述编程电压或所述读取电压的选择控制;

6、读写模块,接所述编程模块的输出端、所述第一控制信号、输入选择信号、时钟触发信号、复位信号及编程数据信号,在所述第一控制信号、所述输入选择信号、所述时钟触发信号及所述复位信号的控制下,对输入的所述编程数据信号进行寄存并对外输出,或者读取所述编程模块的编程数据,得到编程读取信号,并对所述编程读取信号进行寄存和输出;

7、第二电平处理模块,接所述编程模块、所述读写模块及第二使能信号,对所述读写模块的输出信号及所述第二使能信号进行高低电平转换,得到所述第二控制信号;

8、其中,当所述输入选择信号及所述第一控制信号为第一状态时,所述读写模块对输入的所述编程数据信号进行寄存并对外输出,所述编程模块的输入端接入所述编程电压,通过所述第二使能信号使能所述编程模块进入编程状态,通过所述第二控制信号对所述编程模块进行编程操作;当所述输入选择信号及所述第一控制信号为第二状态时,将所述编程模块的输入端上拉至所述读取电压,通过所述第二使能信号将所述编程模块的状态切换为读取状态,所述读写模块读取所述编程模块的编程数据,得到所述编程读取信号。

9、于本发明的一实施例中,所述第一电平处理模块包括:第一缓冲器、第二缓冲器、第三缓冲器、第一非门、第一pmos管、第二pmos管、第一nmos管、第二nmos管及第三nmos管,所述第一缓冲器的输出端与所述第二缓冲器的输入端、所述第三缓冲器的输入端及所述第一非门的输入端相接,所述第二缓冲器的输出端接所述第一nmos管的栅极,所述第一nmos管的漏极接所述第一pmos管的漏极,所述第一pmos管的源极接电源电压,所述第一pmos管的源极还接所述第二pmos管的源极,所述第二pmos管的栅极接所述第一pmos管的漏极,所述第二pmos管的漏极接所述第二nmos管的漏极,所述第二nmos管的栅极接所述第一非门的输出端,所述第二nmos管的源极接所述第一nmos管的源极,所述第二nmos管的源极还接地,所述第三缓冲器的电源端接所述读取电压,所述第三缓冲器的地端接地,所述第三缓冲器的输出端接所述第三nmos管的漏极,所述第三nmos管的栅极接所述第二nmos管的漏极,其中,所述第一缓冲器的输入端接所述第一使能信号,所述第三nmos管的源极接编程模块的输入端,所述第三nmos管的栅极输出所述第一控制信号。

10、于本发明的一实施例中,所述第二电平处理模块包括或非门、第三pmos管、第四pmos管、第四nmos管、第五nmos管及第二非门,所述或非门的输出端接所述第四nmos管的栅极,所述或非门的栅极还接所述第二非门的输入端,所述第二非门的输出端接所述第五nmos管的栅极,所述第四nmos管的源极接所述第五nmos管的源极,所述第四nmos管的源极还接地,所述第四nmos管的漏极接所述第三pmos管的漏极,所述第三pmos管的源极接所述电源电压,所述第三pmos管的源极还接所述第四pmos管的源极,所述第四pmos管的栅极接所述第三pmos管的漏极,所述第四pmos管的漏极接所述第三pmos管的栅极,所述第四pmos管的漏极接所述第五nmos管的漏极,其中,所述或非门的第一输入端接所述第二使能信号,所述或非门的第二输入端接所述编程数据信号,所述第四pmos管的漏极输出所述第二控制信号。

11、于本发明的一实施例中,所述编程模块包括第六nmos管及编程器,所述编程器的一端接所述编程电压,所述编程器的另一端接所述第六nmos管的漏极,所述第六nmos管的栅极接所述第二控制信号,所述第六nmos管的源极接地,其中,所述编程器的一端为所述编程模块的输入端,所述第六nmos管的栅极为所述编程模块的控制端,所述第六nmos管的源极为所述编程模块的输出端。

12、于本发明的一实施例中,所述编程器为pmos管,pmos管的源极接pmos管的漏极构成所述编程器的另一端,pmos管的栅极为所述编程器的一端。

13、于本发明的一实施例中,所述读写模块包括第七nmos管、第八nmos管、第三非门及触发器,所述第七nmos管的源极接所述第八nmos管的漏极,所述第七nmos管的源极还接所述第三非门的输入端,所述第八nmos管的源极接地,所述第三非门的输出端接所述触发器的第二数据输入端,其中,所述第八nmos管的栅极接所述复位信号,所述第七nmos管的漏极接所述编程器的另一端,所述触发器的第一数据输入端接所述编程数据信号,所述触发器的第二数据输入端接所述编程读取信号,所述触发器的输入控制端接所述输入控制信号,所述触发器的触发端接所述时钟触发信号,所述触发器的输出端输出所述编程数据信号,所述触发器的反相输出端输出所述编程读取信号。

14、于本发明的一实施例中,所述第六nmos管的n阱设置于所述编程器的n型衬底中,与所述编程器的另一端相接,所述第七nmos管的n阱设置于所述编程器的n型衬底中。

15、根据本技术实施例的另一个方面,还提供了一种一次性可编程的存储器,包括:多个如前所描述的一次性可编程存储电路,通过多个一次性可编程存储电路对多个所述存储数据进行一一对应的编程操作及数据读取。

16、本技术提供一种一次性可编程的存储电路及存储器,该电路包括:读写模块接输入选择信号、时钟触发信号及复位信号;编程模块的输入端接编程电压,控制端接第二控制信号;第一电平处理模块基于第一使能信号产生第一控制信号并对编程模块的输入端进行控制;第二电平处理模块基于编程数据信号及第二始能信号产生第二控制信号,当输入选择信号及第一控制信号为第一状态时,读写模块对输入的编程数据信号进行寄存输出,编程模块的输入端电压接入编程电压,基于第二使能信号使能编程模块编程进入编程状态;当输入选择信号及第一控制信号为第二状态时,将编程模块的输入端上拉至读取电压,基于第二使能信号将编程模块的状态切换为读取状态,读写模块对编程模块的数据进行读取,得到编程读取信号。本技术提供的一次性可编程的存储电路,通过切换数据输入通道并调节编程模块状态,对编程模块进行外部的数据写入和读出,存储器不仅设计结构简单,在进行读写过程中,可快速并简洁完成读写。

17、应当理解的是,以上的一般描述和后文的细节描述仅是示例性和解释性的,并不能限制本发明。

本文地址:https://www.jishuxx.com/zhuanli/20240731/184792.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 YYfuon@163.com 举报,一经查实,本站将立刻删除。

下一篇

返回列表