存储芯片、存储芯片控制方法和存储系统与流程

- 国知局

- 2024-07-31 20:03:27

本公开涉及存储,特别涉及一种存储芯片、存储芯片控制方法和存储系统。

背景技术:

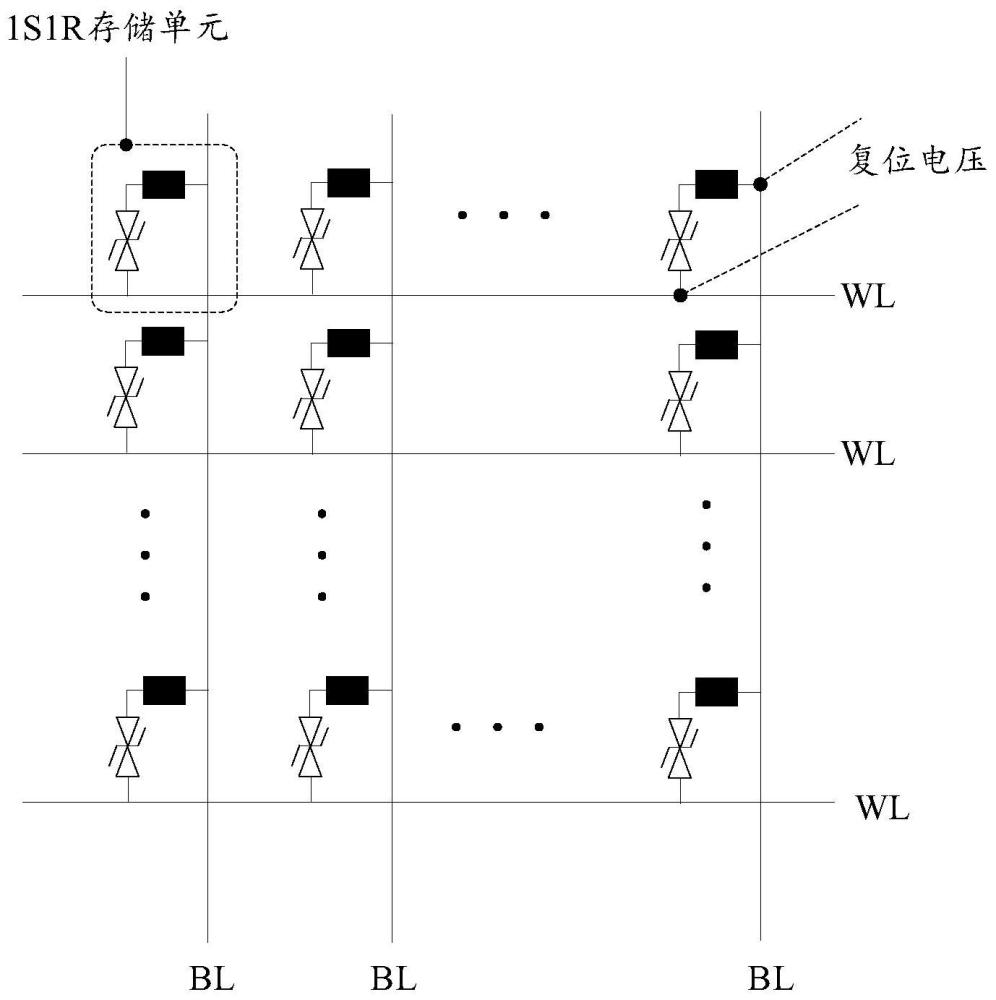

1、相变存储芯片中的单一选通管单一电阻器(one selector one resistor,1s1r)存储单元由一个相变存储器(phase change memory,pcm)和一个双向阈值开关(ovonicthresholdswitch,ots)组成。

2、1s1r存储单元在存储“0”时,1s1r存储单元具有较高的阈值电压,1s1r存储单元在存储“1”时,1s1r存储单元具有较低的阈值电压。因此,可以通过检测1s1r存储单元的阈值电压,确定1s1r存储单元中存储的数据。

3、1s1r存储单元的阈值电压与pcm的阈值电压以及ots的阈值转换电压相关,pcm的阈值电压或ots阈值转换电压的改变都会影响1s1r存储单元的阈值电压。

4、ots的阈值转换电压具有明显的漂移现象,如每次对1s1r存储单元进行读写操作后,ots的阈值转换电压都会有一个明显的下降,且在较长的时间内无法恢复,如一般恢复需要几个小时甚至几天。如此,ots的阈值转换电压漂移现象会对1s1r存储单元的阈值电压产生影响,增大了对1s1r存储单元进行读取的出错概率。

技术实现思路

1、本公开实施例提供了一种存储芯片、存储芯片控制方法和存储系统,可以降低对存储单元进行读取的出错概率,相应的技术方案如下:

2、第一方面,提供了一种存储芯片的控制方法,应用于存储芯片,存储芯片包括多个存储单元,每个存储单元包括双向阈值开关ots和存储介质,ots具有阈值转变电压,根据阈值转变电压对存储单元施加读写电压以对存储介质进行读写操作。该控制方法包括:

3、当侦测到预设条件时,对多个存储单元中的第一存储单元施加复位电压,当多个存储单元中的第一存储单元为处于低阻状态的存储单元时,复位电压开启第一存储单元的ots,以使第一存储单元的ots的阈值转变电压降低。

4、在本公开提供的控制方法中,通过向第一存储单元施加复位电压,能够开启低阻状态的存储单元的ots,可以使得低阻状态的存储单元中ots的阈值转变电压维持在一个较低的水平,如此能够避免ots阈值转换电压漂移导致读电压无法区分低阻状态和高阻状态的存储单元的问题,能够降低对存储单元进行读取的出错概率。

5、在一种可实现的方式中,复位电压大于存储芯片的读电压。

6、在本公开提供的控制方法中,由于存储芯片的读电压大于低阻状态的存储单元对应的阈值电压。所以向存储单元施加复位电压,至少能够使得低阻状态的存储单元中的ots开启,使得低阻状态的存储单元中ots的阈值转变电压维持在一个较低的水平,能够降低对存储单元进行读取的出错概率。

7、在一种可实现的方式中,侦测到预设条件包括侦测到预设的时间,预设的时间为指定的时间间隔到达后的时间。

8、在本公开提供的控制方法中,可以按照指定的时间间隔向第一存储单元施加复位电压,如此可以一直将第一存储单元中ots的阈值转变电压维持在一个较低的水平,能够降低对存储单元进行读取的出错概率。

9、在一种可实现的方式中,预设条件为侦测到复位请求。其中,在复位请求可以携带有第一存储单元的地址信息,能够实现灵活的对第一存储单元施加复位电压。

10、在一种可实现的方式中,第一存储单元为存储芯片所包括的所有存储单元。

11、在一种可实现的方式中,第一存储单元为存储芯片所包括的部分存储单元。

12、在一种可实现的方式中,第一存储单元为存储芯片中统计的在指定时间内进行读操作和写操作次数小于次数阈值的存储单元。

13、在本公开提供的控制方法中,当第一存储单元为存储芯片所包括的部分存储单元时,第一存储单元可以是存储芯片中统计的在指定时间内进行读操作和写操作次数小于次数阈值的存储单元,即第一存储单元为进行读操作和写操作不频繁的存储单元。这样,对于读操作和写操作不频繁的存储单元施加复位电压,能够使得该部分存储单元的ots的阈值转变电压维持在一个较低的水平,可以避免该部分存储单元的ots的阈值转变电压由于长时间未操作漂移至比较高的阈值转变电压。

14、在一种可实现的方式中,第一存储单元为存储芯片中在指定时长内未进行过读操作和写操作的存储单元。

15、在本公开提供的控制方法中,在对各存储单元进行读操作和写操作后,可以对存储单元进行计时,当存储单元在指定时长内未进行过读操作和写操作时,可以向该存储单元施加复位电压,可以避免该部分存储单元的ots的阈值转变电压由于长时间未操作漂移至比较高的阈值转变电压。

16、在一种可实现的方式中,对多个存储单元中的第一存储单元施加复位电压,包括:对第一存储单元耦合的字线施加第一电压,对第一存储单元耦合的位线施加第二电压,第一电压和第二电压在第一存储单元上形成的压差等于复位电压。

17、在一种可实现的方式中,指定的时间间隔小于低阻状态的存储单元的阈值电压漂移到存储芯片的读电压的时长。

18、在本公开提供的控制方法中,当按照指定的时间间隔向第一存储单元施加复位电压时,该指定的时间间隔不会大于低阻状态的存储单元的阈值电压漂移到存储芯片的读电压的时长。这样可以避免存储单元的阈值电压受ots的阈值转变电压漂移影响,复位电压无法开启ots的问题出现。

19、在一种可实现的方式中,侦测到预设条件之前,还包括:获取存储芯片当前的目标温度;在温度和时长的对应关系中,确定目标温度对应的目标时长,其中,在温度和时长的对应关系中温度与时长负相关;将目标时长确定为指定的时间间隔。

20、在本公开提供的控制方法中,ots阈值转变电压的向上漂移速度与温度相关,温度越高,ots阈值转变电压的向上漂移速度的越快。因此上述指定的时间间隔可以根据当前的目标温度灵活调整。在温度低时可以延长该时间间隔,能降低存储芯片的功耗,在温度高时,可以缩短该时间间隔,能够避免ots的阈值转变电压漂移至较高的阈值转变电压,复位电压无法开启ots的问题出现。

21、在一种可实现的方式中,对多个存储单元中的第一存储单元施加复位电压之前,还包括:获取存储芯片对应的疲劳次数;在次数与电压的对应关系中,确定疲劳次数对应的目标电压,其中,在次数与电压的对应关系中次数与电压负相关;将目标电压确定为复位电压。

22、在本公开提供的控制方法中,疲劳次数是指对存储芯片进行读操作和写操作的次数。锁着存储芯片中的存储单元进行读操作和写操作的次数增多,存储单元中存储介质会发生衰变,导致存储单元的阈值电压降低。因此,在向第一存储单元施加复位电压时,可以根据存储芯片的疲劳次数动态调整复位电压大小,能够降低存储芯片的施加复位电压的功耗。

23、在一种可实现的方式中,对多个存储单元中的第一存储单元施加复位电压,包括:按照预设顺序分批向各第一存储单元施加复位电压,其中,每批施加复位电压的第一存储单元的个数与存储芯片的温度正相关。

24、在本公开提供的控制方法中,ots阈值转变电压的向上漂移速度与温度相关,温度越高,ots阈值转变电压的向上漂移速度的越快。这样在温度高时可以增加施加复位电压的第一存储单元的个数,能够使得各第一存储单元整体施加复位电压的时长变短,可以避免ots的阈值转变电压漂移至较高的阈值转变电压。

25、第二方面,提供了一种存储芯片,该存储芯片包括外围电路和多个存储单元,外围电路通过存储芯片中的字线和位线与每个存储单元连接,每个存储单元包括双向阈值开关ots和存储介质,ots具有阈值转变电压,根据阈值转变电压对存储单元施加读写电压以对存储介质进行读写操作;

26、外围电路用于:当侦测到预设条件时,对多个存储单元中的第一存储单元施加复位电压,当多个存储单元中的第一存储单元为处于低阻状态的存储单元时,复位电压开启第一存储单元的ots,以使第一存储单元的ots的阈值转变电压降低。

27、在一种可实现的方式中,复位电压大于存储芯片的读电压。

28、在一种可实现的方式中,侦测到预设条件包括侦测到预设的时间,预设的时间为指定的时间间隔到达后的时间。

29、在一种可实现的方式中,预设条件为侦测到复位请求。

30、在一种可实现的方式中,第一存储单元为存储芯片所包括的所有存储单元。

31、在一种可实现的方式中,第一存储单元为存储芯片所包括的部分存储单元。

32、在一种可实现的方式中,第一存储单元为存储芯片中统计的在指定时间内进行读操作和写操作次数小于次数阈值的存储单元。

33、在一种可实现的方式中,第一存储单元为存储芯片中在指定时长内未进行过读操作和写操作的存储单元。

34、在一种可实现的方式中,外围电路用于:对第一存储单元耦合的字线施加第一电压,对第一存储单元耦合的位线施加第二电压,第一电压和第二电压在第一存储单元上形成的压差等于复位电压。

35、在一种可实现的方式中,指定的时间间隔小于低阻状态的存储单元的阈值电压漂移到存储芯片的读电压的时长。

36、在一种可实现的方式中,外围电路还用于:获取存储芯片当前的目标温度;在温度和时长的对应关系中,确定目标温度对应的目标时长,其中,在温度和时长的对应关系中温度与时长负相关;将目标时长确定为指定的时间间隔。

37、在一种可实现的方式中,外围电路还用于:获取存储芯片对应的疲劳次数;在次数与电压的对应关系中,确定疲劳次数对应的目标电压,其中,在次数与电压的对应关系中次数与电压负相关;将目标电压确定为复位电压。

38、在一种可实现的方式中,外围电路还用于:按照预设顺序分批向各第一存储单元施加复位电压,其中,每批施加复位电压的第一存储单元的个数与存储芯片的温度正相关。

39、第三方面,提供了存储系统包括:一个或多个如上述第二方面所述的存储芯片;与所述存储芯片连接,且用于对所述存储芯片进行控制的存储控制器。

本文地址:https://www.jishuxx.com/zhuanli/20240731/185251.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 YYfuon@163.com 举报,一经查实,本站将立刻删除。

下一篇

返回列表