一种14T-TFET-SRAM单元电路、模块及阵列

- 国知局

- 2024-07-31 20:14:50

本发明涉及集成电路设计,更具体的,涉及:1、一种14t-tfet-sram单元电路,2、一种基于该种14t-tfet-sram单元电路设计的模块,3、一种基于该种14t-tfet-sram单元电路构建的阵列。

背景技术:

1、隧穿场效应晶体管(tfet)作为非玻尔兹曼分布器件,具有陡峭亚阈值摆幅,这使得tfet器件在低电压低功耗领域具有广阔的应用前景,拥有巨大的潜力,成为近些年关注的焦点。

2、相比 mosfet 器件而言,teft 器件工艺简单,可靠性高。由于teft 器件基于隧穿机制而具有的优点,能使集成电路工作在低压环境,使低功耗技术有很大的突破。

3、但由于teft器件的源极和漏极掺杂不均匀,具有单向导通性,这导致其在工作时可能出现不受栅极电压控制的正向偏置电流,这将极大增大现有sram(6t-tfet-sram、8t-tfet-sram)的静态功耗,并破坏存储节点的电压稳定性。同时,由于tfet器件相对mosfet器件的导通电流更小,导致其写能力和写稳定性较弱,写噪声容限较低。

技术实现思路

1、基于此,有必要针对现有tfet-sram单元写噪声容限较低、静态功耗大的问题,提供一种14t-tfet-sram单元电路、模块及阵列。

2、本发明采用以下技术方案实现:

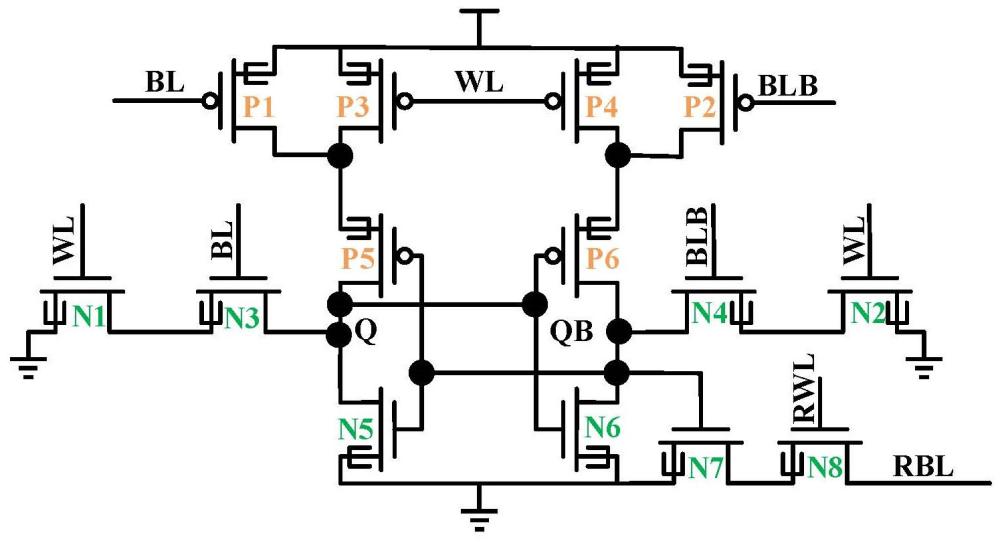

3、第一方面,本发明提供了一种14t-tfet-sram单元电路,包括:6个ptfet晶体管p1~p6、8个ntfet晶体管n1~n8;

4、p1的源极电连接电源vdd,p1的栅极电连接写字线bl。p2的源极电连接电源vdd,p2的栅极电连接写位线blb。p3的源极电连接电源vdd,p3的栅极电连接写字线wl。p4的源极电连接电源vdd,p4的栅极电连接写字线wl。p5的源极电连接p1、p3的漏极。p6的源极电连接p2、p4的漏极。n1的源极电连接地线gnd,n1的栅极电连接写字线wl。n2的源极电连接地线gnd,n2的栅极电连接写字线wl。n3的源极电连接n1的漏极,n3的栅极电连接写字线bl,n3的漏极电连接p5的漏极。n4的源极电连接n2的漏极,n4的栅极电连接写位线blb,n4的漏极电连接p6的漏极。n5的源极电连接地线gn,n5的漏极电连接p5的漏极、并设置有存储节点q,n5的栅极电连接p5的栅极、p6的漏极。n6的源极电连接地线gnd,n6的漏极电连接p6的漏极、并设置有存储节点qb,n6的栅极电连接p6的栅极、p5的漏极。n7的源极电连接地线gnd,n7的栅极电连接n6的漏极。n8的源极电连接n7的漏极,n8的栅极电连接读字线rwl,n8的漏极连接读位线rbl。

5、该种14t-tfet-sram单元电路的实现根据本公开的实施例的方法或过程。

6、第二方面,本发明公开了一种14t-tfet-sram模块,采用了第一方面公开的14t-tfet-sram单元电路的布局。

7、该种14t-tfet-sram模块的实现根据本公开的实施例的方法或过程。

8、第三方面,本发明公开了一种基于14t-tfet-sram单元电路构建的阵列,包括2i2j个、呈阵列分布的如第一方面公开的14t-tfet-sram单元电路;i、j≥1。

9、其中,同一行的14t-tfet-sram单元电路共用同一个n1、同一个n2;

10、同一行的14t-tfet-sram单元电路共用同一根wl、同一根rwl;

11、同一列的14t-tfet-sram单元电路共用同一根bl、同一根blb、同一根rbl。

12、该种基于14t-tfet-sram单元电路构建的阵列的实现根据本公开的实施例的方法或过程。

13、与现有技术相比,本发明具备如下有益效果:

14、1,本发明提出的14t-tfet-sram单元电路充分利用了低电压下tfet晶体管具有更好开关特性和更低的亚阈值摆幅的优势,添加了p1、p2作为写辅助管,大大提高了单元电路的写能力;通过电路设计,使得传输管n1、n2、n3、n4的漏极电压始终不低于源极电压,不仅提高了单元电路的写能力,而且消除了tfet器件的正向偏置电流,降低了单元电路的静态功耗,增大单元电路的噪声容限。

15、2,本发明提出的14t-tfet-sram单元电路在组成阵列时,可以同一行共用同一个n1、同一个n2,能够减少阵列中晶体管的数量,降低面积占用。

技术特征:1.一种14t-tfet-sram单元电路,其特征在于,包括:

2.根据权利要求1所述的14t-tfet-sram单元电路,其特征在于,n7、n8作为读操作管;p5、p6为上拉晶体管,n5、n6为下拉晶体管;p5、n5构成一个反相器,p6、n6构成另一个反相器,两个反相器组成锁存结构;p1、p2作为写辅助晶体管;p3、p4作为防悬空晶体管;n1、n2、n3、n4作为单位传输管。

3.根据权利要求1所述的14t-tfet-sram单元电路,其特征在于,在保持状态下,wl、rwl为低电平,bl、blb为低电平,rbl为低电平,n1、n2、n3、n4、n8关闭,p1、p2、 p3、p4导通,使锁存结构处于稳定状态。

4.根据权利要求1所述的14t-tfet-sram单元电路,其特征在于,在保持状态下,n1的漏极电压始终不低于n1的源极电压,n2的漏极电压始终不低于n2的源极电压,n3的漏极电压始终不低于n3的源极电压,n4的漏极电压始终不低于n4的源极电压。

5.根据权利要求1所述的14t-tfet-sram单元电路,其特征在于,在读操作阶段,rbl连接有灵敏放大器;wl为低电平,bl、blb为低电平,n1、n2、n3、n4关闭,p1、p2、 p3、p4导通;rwl为高电平,n8打开;rbl被预充为高电平;

6.根据权利要求1所述的14t-tfet-sram单元电路,其特征在于,进行写“0”操作时,wl为高电平,bl为高电平,blb为低电平,n1、n2、n3、p2导通,p1、p3、p4、n4关断;

7.根据权利要求1所述的14t-tfet-sram单元电路,其特征在于,进行写“1”操作时,wl为高电平,blb为高电平,bl为低电平,p1、n1、n2、n4导通,p2、p3、p4、n3关断;

8.一种14t-tfet-sram模块,其特征在于,采用了如权利要求1-7中任一所述的14t-tfet-sram单元电路的布局。

9.一种基于14t-tfet-sram单元电路构建的阵列,其特征在于,包括2i2j个、呈阵列分布的如权利要求1-7中任一所述的14t-tfet-sram单元电路; i、j≥1;

10.根据权利要求9所述的基于14t-tfet-sram单元电路构建的阵列,其特征在于,在阵列中,通过控制bl、blb实现列向的打开或关闭,通过控制wl实现行向的打开或关闭。

技术总结本发明涉及集成电路设计技术领域,更具体的,涉及一种14T‑TFET‑SRAM单元电路、模块及阵列。本发明的单元电路包括6个PTFET晶体管P1~P6、8个NTFET晶体管N1~N8。本发明充分利用了低电压下TFET晶体管具有更好开关特性和更低的亚阈值摆幅的优势,添加了P1、P2作为写辅助管,大大提高了单元电路的写能力;通过电路设计,使得传输管N1、N2、N3、N4的漏极电压始终不低于源极电压,不仅提高了单元电路的写能力,而且消除了TFET器件的正向偏置电流,降低了单元电路的静态功耗,增大单元电路的噪声容限。本发明解决了现有TFET‑SRAM单元写噪声容限较低、静态功耗大的问题。技术研发人员:卢文娟,张其众,胡薇,吴秀龙受保护的技术使用者:安徽大学技术研发日:技术公布日:2024/7/18本文地址:https://www.jishuxx.com/zhuanli/20240731/185541.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 YYfuon@163.com 举报,一经查实,本站将立刻删除。

上一篇

一种计算机内存条清理装置

下一篇

返回列表