一种存储结构、存储模块、存储系统以及制备方法与流程

- 国知局

- 2024-07-31 20:15:03

本发明涉及半导体,特别是一种存储结构、存储单元、存储模块、存储系统以及制备方法。

背景技术:

1、随着当前科技的飞速发展,国内外市场对电子产品提出了更高的要求。数据存储器作为关键器件,也面临着新的挑战。

2、其中,易失性存储器,包括静态随机存储器(sram)和动态随机存储器(dram)的读写虽然很快,速度达到纳秒级,但缺点是在断电情况下信息容易丢失,从而限制其即插即用,不能长时间保存数据,并且占用面积较大,成本较高,且不能做成3d结构来提升存储密度。而闪存存储器(flash)等非易失性存储器虽然可以长时间保存数据,成本低、可做成3d结构来实现高存储密度,但写入速度慢,甚至为毫秒级,可擦写次数少,无法满足实时处理系统中高速、高可靠性写入和无限次数擦写的要求。

3、以上两种传统存储器的功耗也较高,无法满足未来物联网应用的低功耗需求。

技术实现思路

1、本部分的目的在于概述本发明的实施例的一些方面以及简要介绍一些较佳实施例。在本部分以及本技术的说明书摘要和发明名称中可能会做些简化或省略以避免使本部分、说明书摘要和发明名称的目的模糊,而这种简化或省略不能用于限制本发明的范围。

2、鉴于现有技术的问题,提出了本发明。

3、因此,本发明的第一个目的是提供一种存储单元,其读写速度很快,可达到纳秒级,且具有高可靠性和低功耗。本发明的第二个目的是提供一种存储结构,采用三维立体结构,结构上突破传统二维结构的局限,实现三维架构的堆叠,从而实现存储密度质的飞跃。而存储单元的高性能与存储结构高密度的结合是现今存储器研发的最大挑战,因此本发明的第三个目的是提供一种制备方法,其利用环绕栅极晶体管和三维自发极化电容的方式来实现数据的存储,这种存储系统具有优异的存储性能,且拥有极高的数据容量。

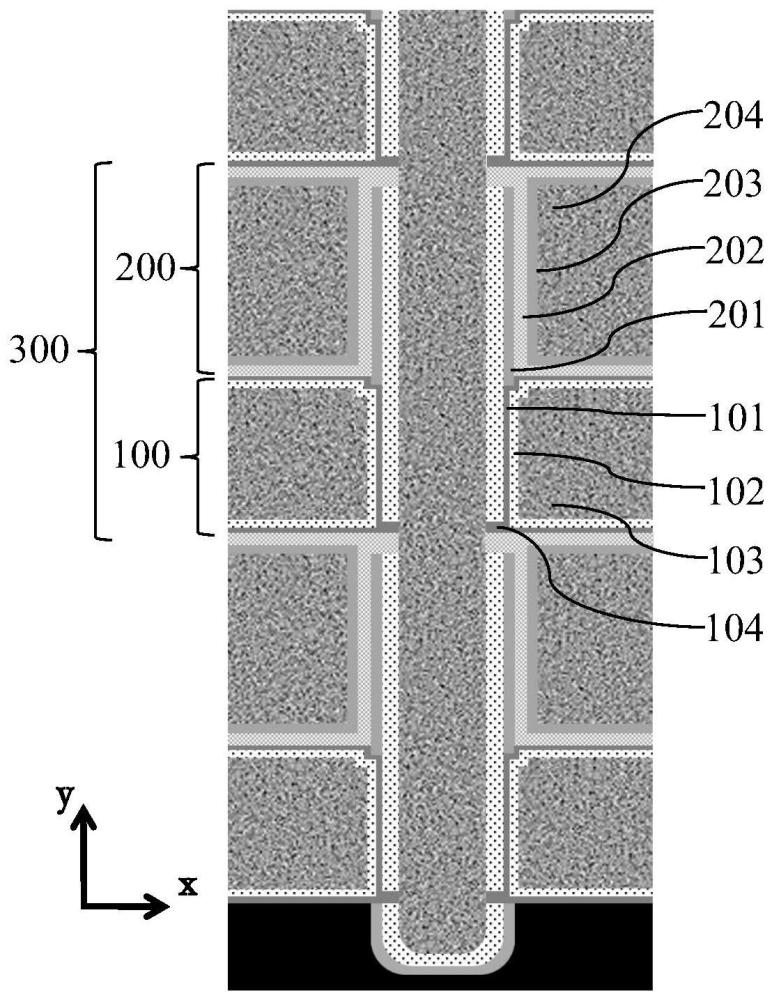

4、为解决上述技术问题,本发明提供如下技术方案:一种存储结构,包括,存储元件;开关元件;以及,位线,所述开关元件的其中一极与所述存储元件的一个电极相连接,另一极连接至所述位线;所述存储元件与其相邻的开关元件构成存储单元,在晶圆表面垂直方向上,形成存储元件与开关元件交替排列。

5、作为本发明所述存储结构的一种优选方案,其中:所述存储元件采用三维自发极化电容,且所述存储元件包括有第一电极和第二电极,所述第一电极和所述第二电极间设有自发极化高介电常数材料。

6、作为本发明所述存储结构的一种优选方案,其中:所述开关元件采用环绕栅极晶体管,且所述开关元件包括薄膜沟道;所述薄膜沟道的一端与所述位线相连,另一端与所述存储元件的一个电极相连接。

7、为解决上述技术问题,本发明提供如下技术方案:一种存储模块,还包括,字线、板线;其中,存储单元的存储元件的一个电极连接一个对应的板线;所述存储单元的开关元件的栅极连接一个对应的字线。

8、作为本发明所述存储模块的一种优选方案,其中:多个所述存储单元共用一条位线,多个所述存储单元围绕于所述位线的周围,在与晶圆表面垂直方向上排列成筒状三维结构;所述位线为柱状或筒状结构。

9、作为本发明所述存储模块的一种优选方案,其中:还包括存储阵列,所述存储阵列包括多组存储模块,每组所述存储模块的多个存储单元共用一条位线,不同组所述存储模块的同一层多个存储单元共用一个字线与和一个板线。

10、作为本发明所述存储模块的一种优选方案,其中:还包括台阶结构;所述台阶结构靠近所述存储阵列边缘;所述台阶结构中的每两层相邻台阶的上表面分别对应一个字线和一个板线;所述台阶结构中的每层台阶沿着垂直于晶圆表面方向堆叠,每层台阶分别连接一个金属触点。

11、作为本发明所述存储模块的一种优选方案,其中:还包括台阶结构;所述台阶结构靠近所述存储阵列边缘,分为两个区域;其中一个所述区域中台阶结构的每层台阶的上表面分别对应一个板线;另一个所述区域中台阶结构的每层台阶的上表面分别对应一个字线;所述台阶结构中的每层台阶沿着垂直于晶圆表面方向堆叠,每层台阶分别连接一个金属触点。

12、为解决上述技术问题,本发明提供如下技术方案:一种制备方法,包括有,沉积阻挡层以及多组复合膜层形成三维堆叠膜层;在三维堆叠膜层内构建孔洞,并在孔洞内设置位线;在存储阵列边缘构建台阶结构;在位线外侧设置环绕栅极晶体管并形成与所述环绕栅极晶体管连接的三维自发极化电容。

13、作为本发明所述制备方法的一种优选方案,其中:所述形成三维堆叠膜层的方法包括,在已完成周边电路的晶圆上沉积第一阻挡层;在第一阻挡层上重复沉积多组复合膜层;再在复合膜层上沉积第二阻挡层所述复合膜层为多层结构,由下至上包括第一牺牲层、第二牺牲层和第三牺牲层。

14、作为本发明所述制备方法的一种优选方案,其中:所述三维堆叠膜层上构建孔洞是通过干法刻蚀的方式,所述阻挡层的刻蚀速率低于所述复合膜层的刻蚀速率的一半。

15、作为本发明所述制备方法的一种优选方案,其中:所述设置位线的方法包括,

16、采用原子沉积或化学气相沉积的方式在孔洞内壁依次沉积底电极和位线绝缘层;再通过化学气相沉积或离子化物理气相沉积或其他高阶梯覆盖率的沉积方式在所述孔洞内沉积位线金属,直至填满整个孔洞。

17、作为本发明所述制备方法的一种优选方案,其中:所述构建台阶结构的方法包括,

18、使用光刻掩膜,以光刻胶覆盖存储阵列区域以及其它需要保护的区域;进行牺牲层刻蚀,采用至少两种高选择比刻蚀相配合,其中一种高选择比刻蚀中第二牺牲层的刻蚀速率大于第三牺牲层的刻蚀速率的二倍,另一种高选择比刻蚀中第二牺牲层的刻蚀速率小于第三牺牲层的刻蚀速率的一半;通过干法刻蚀进行光刻胶削薄,每次削薄使光刻胶膜层周边在平行于晶圆的平面上向内缩小一个阶梯的宽度。

19、作为本发明所述制备方法的一种优选方案,其中:在所述位线外侧设置环绕栅极晶体管并形成与所述环绕栅极晶体管连接的三维自发极化电容,包括,

20、通过干法刻蚀形成隙缝停在第一阻挡层;

21、通过隙缝进行各向同性高选择比刻蚀,依次去除第一牺牲层、底电极和位线绝缘层;

22、采用原子沉积或化学气相沉积在已经除去的第一牺牲层、底电极和位线绝缘层的位置填充第三牺牲层材料,再进行各向同性高选择比刻蚀除去第二牺牲层和底电极;

23、进行各向同性高选择比刻蚀打薄第三牺牲层,露出位线和一部分底电极;

24、通过原子层沉积法依次沉积薄膜沟道材料、栅氧化层以及字线材料层;

25、进行各向同性高选择比刻蚀的移除第三牺牲层;

26、通过原子层沉积或化学气相沉积依次沉积自发极化高介电常数材料、顶电极以及板线材料层。

27、本发明的有益效果:采用环绕栅极晶体管和三维自发极化电容组成存储单元围绕于位线的周围,在与晶圆表面垂直方向上排列成筒状三维结构实现高密度的数据存储。结构上突破传统二维结构的局限,实现三维架构的堆叠,从而实现存储密度质的飞跃。其读写速度很快,可达到纳秒级,且具有高可靠性和低功耗。解决了现今存储器研发的最大挑战,即存储单元的高性能与存储结构高密度的结合。

本文地址:https://www.jishuxx.com/zhuanli/20240731/185546.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 YYfuon@163.com 举报,一经查实,本站将立刻删除。

下一篇

返回列表