在可配置PAM电平处的读取时钟切换的制作方法

- 国知局

- 2024-07-31 20:15:33

背景技术:

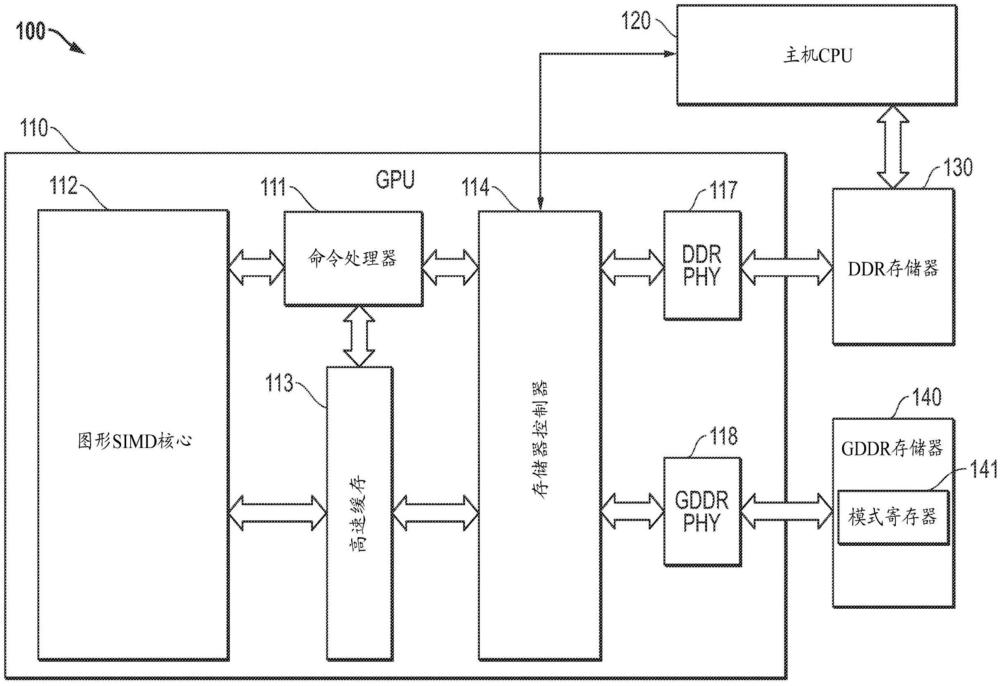

1、现代动态随机存取存储器(dram)通过增加连接dram和诸如图形处理单元(gpu)、中央处理单元(cpu)等一个或多个数据处理器的总线上的数据传输速度来提供高存储器带宽。dram通常为便宜且高密度的,从而使得每个设备能够集成大量的dram。现今销售的大多数dram芯片与由联合电子设备工程委员会(jedec)发布的各种双倍数据速率(ddr)dram标准兼容。通常,若干ddr dram芯片被组合到单个印刷电路板衬底上,以形成不仅可以提供相对较高的速度还可以提供可缩放性的存储器模块。然而,虽然这些增强已改进用于计算机系统的主存储器的ddr存储器的速度,但仍期望进一步的改进。

2、一种类型的ddr dram,称为图形双数据速率(gddr)存储器,已突破了数据传输速率的界限,以适应图形应用所需的高带宽。随着新gddr标准的开发,它们往往会支持更高的数据速率。用于支持更高的数据速率的一种技术是多电平脉冲振幅调制(pam)数据传输和接收模式,而不是常规的两电平传输系统。利用更多的pam电平,可以在给定的时钟速度下增加数据传输带宽。然而,在这些高速下连续传输数据会导致相对高的功耗。

技术实现思路

技术特征:1.一种用于通过存储器总线从存储器向存储器控制器选择性地提供读取时钟信号的读取时钟电路,所述读取时钟电路包括:

2.根据权利要求1所述的读取时钟电路,其中所述两个所选择的电平基于所述模式寄存器中的一个或多个值。

3.根据权利要求1所述的读取时钟电路,其中所述数字控制电路能够操作以使所述pam驱动器在所述初始切换状态之前在所述前导码中提供至少一个静态状态。

4.根据权利要求1所述的读取时钟电路,其中在所述最终切换状态中的所述两个所选择的电平是在所述读取操作期间用于所述读取时钟信号的所述电平。

5.根据权利要求1所述的读取时钟电路,其中所述初始切换状态期间的所述两个所选择的电平不同于所述最终切换状态中的所述电平。

6.根据权利要求1所述的读取时钟电路,其中所述数字控制电路能够被配置为包括在所述初始切换状态与所述最终切换状态之间的第二切换状态,所述第二切换状态以在所述初始切换状态与所述最终切换状态的速率之间的速率切换。

7.一种用于通过存储器总线从存储器向存储器控制器选择性地提供读取时钟信号的方法,所述方法包括:

8.根据权利要求7所述的方法,其中所述两个所选择的电平基于所述模式寄存器中的一个或多个值。

9.根据权利要求7所述的方法,所述方法还包括在所述初始切换状态之前在所述前导码中提供至少一个静态状态。

10.根据权利要求7所述的方法,其中在所述最终切换状态中的所述两个所选择的电平是在读取操作期间用于所述读取时钟信号的所述电平。

11.根据权利要求7所述的方法,其中所述初始切换状态期间的所述两个所选择的电平不同于所述最终切换状态中的所述电平。

12.根据权利要求7所述的方法,所述方法还包括提供在所述初始切换状态与所述最终切换状态之间的第二切换状态,所述第二切换状态以在所述初始切换状态与所述最终切换状态的速率之间的速率切换。

13.根据权利要求7所述的方法,其中所述pam驱动器能够驱动四个电平,所述四个电平指示相对于1.2伏的信令供电电压的相应两位数字值。

14.根据权利要求7所述的方法,其中所述读取时钟的切换速率基于在所述存储器处从所述存储器控制器接收的写入时钟的切换速率。

15.一种数据处理系统,所述数据处理系统包括:

16.根据权利要求15所述的数据处理系统,其中所述两个所选择的电平基于所述模式寄存器中的一个或多个值。

17.根据权利要求15所述的数据处理系统,其中所述数字控制电路能够操作以使所述pam驱动器在所述初始切换状态之前在所述前导码中提供至少一个静态状态。

18.根据权利要求15所述的数据处理系统,其中在所述最终切换状态中的所述两个所选择的电平是在所述读取操作期间用于所述读取时钟信号的所述电平。

19.根据权利要求15所述的数据处理系统,其中所述初始切换状态期间的所述两个所选择的电平不同于所述最终切换状态中的所述电平。

20.根据权利要求15所述的数据处理系统,其中所述数字控制电路能够被配置为包括在所述初始切换状态与所述最终切换状态之间的第二切换状态,所述第二切换状态包括以在所述初始切换状态与所述最终切换状态的速率之间的速率切换。

技术总结一种读取时钟电路,该读取时钟电路通过存储器总线从存储器向存储器控制器选择性地提供读取时钟信号。脉冲振幅调制(PAM)驱动器,该PAM驱动器包括能够驱动指示相应数字值的至少三个电平的输入端和输出端。一种数字控制电路耦接到该PAM驱动器,并且能够操作以使该PAM驱动器在该读取时钟信号之前提供前导码信号,该前导码信号包括初始切换状态和最终切换状态,在该初始切换状态中,该PAM驱动器以第一速率在两个所选择的电平之间切换,在该最终切换状态中,该PAM驱动器以高于该第一速率的第二速率在两个所选择的电平之间切换,其中该初始切换状态的长度和该最终切换态的长度基于模式寄存器中的值。技术研发人员:亚伦·约翰·尼格伦,迈克尔·约翰·利特,卡西克·戈帕拉克里希南,刘俊豪受保护的技术使用者:超威半导体公司技术研发日:技术公布日:2024/7/23本文地址:https://www.jishuxx.com/zhuanli/20240731/185596.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 YYfuon@163.com 举报,一经查实,本站将立刻删除。

下一篇

返回列表