上电自动校正VCO增益的CDR电路的制作方法

- 国知局

- 2024-08-02 15:10:45

本发明涉及集成电路领域,具体涉及一种上电自动校正vco增益的cdr电路。

背景技术:

1、时钟数据恢复(clock data recover,cdr)电路应用于高速互联芯片中,数据信号经过信道衰减后,数据信号质量已经严重变形,数据信号的误码率大大增加。这需要通过cdr电路将数据信号和时钟信号恢复出来并整形后送到下级模块,提升信号质量。

2、cdr电路是一种用于从输入数据流中提取和重建时钟信号的电子电路。cdr电路在通信系统、存储系统和高速数据传输中具有重要作用。

3、cdr电路主要包括如下步骤:(1)锁相过程;cdr电路常用锁相环来锁定输入数据流中的频率和相位,生成一个与数据流同步的时钟信号。(2)数据采样;利用恢复的时钟信号对输入数据进行采样,以提取出准确的数据信号。(3)误差检测和校正;通过检测时钟和数据之间的相位误差,调整时钟以确保采样点与数据的中心对齐,从而最小化误码率。

4、图1展示了cdr电路在前级芯片和后级芯片间所起作用的示意图。为了不让信号传输质量变差,在前级芯片和后级芯片之间插入cdr电路,用于恢复和整形信号波形,提升信号质量。

5、cdr电路中包括压控振荡器(voltage controlled oscillator,vco),而vco则受工艺、电源电压和温度的变化影响,导致vco增益发生变化或存在差异,从而影响cdr电路的稳定性和带宽大小,数据抖动增大,降低数据恢复时的误码率。

6、目前现有技术中,尚没有较好的可以改善cdr电路中数据抖动的方法。

技术实现思路

1、为了缓解或部分缓解上述技术问题,本发明的解决方案如下所述:

2、一种上电自动校正vco增益的cdr电路,包括:vco,所述vco包括n个可变电容,分别为:第一可变电容至第n可变电容,第i可变电容是所述n个可变电容中的任一个,n为正整数,i属于1至n中任一个正整数;工艺偏差检测电路,所述工艺偏差检测电路包括n个电路单元,分别为:第一电路单元至第n电路单元;其中,所述n个电路单元的电路结构均相同,且第i电路单元包括第i镜像可变电容和第i比较器,所述第i镜像可变电容与vco中的第i可变电容在规格上相同;所述工艺偏差检测电路连接所述vco,并向vco输出用于指示选定可变电容的信息;根据用于指示选定可变电容的信息,vco将选定可变电容接入vco;此外,当cdr电路上电时,在预设时长内以恒定的电流对第i镜像可变电容充电,并将第i镜像可变电容的电压和参考电压作为第i比较器的输入,第i比较器输出第i比较器输出信号,所述工艺偏差检测电路共获得n个比较器输出信号;根据所述n个比较器输出信号,所述工艺偏差检测电路将所述n个可变电容中的一个可变电容确定为所述选定可变电容。

3、进一步地,从第一可变电容的电容值至第n可变电容的电容值,电容值依次减小或增加。

4、进一步地,在预设时长内以恒定的电流对第i镜像可变电容充电之前,先对第i镜像可变电容放电。

5、进一步地,若所述n个比较器输出信号中的第j比较器输出信号是最后一个发生翻转的比较器输出信号,则选择第j可变电容为选定可变电容;其中,j为一个正整数且j不大于n。

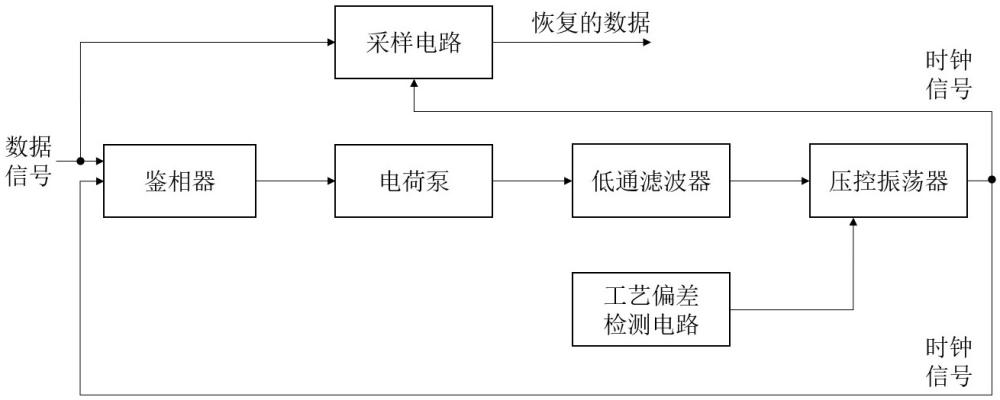

6、进一步地,所述cdr电路还包括鉴相器、电荷泵、低通滤波器和采样电路;cdr电路接收的数据信号和vco输出的时钟信号被送入鉴相器,鉴相器输出误差信号至电荷泵,电荷泵的输出信号被低通滤波器过滤后所生成的控制信号被送入vco;所述数据信号和vco输出的时钟信号还被送入采样电路,以获得恢复的数据。

7、进一步地,所述恒定的电流是由电流源提供。

8、本发明技术方案,具有如下有益的技术效果之一或多个:

9、(1)提供了一种可以对抗温度、电压、工艺等变化而消除vco增益差异的技术方案。

10、(2)改善cdr电路输出信号抖动性能。

11、此外,本发明还具有的其它有益效果将在具体实施例中提及。

技术特征:1.一种上电自动校正vco增益的cdr电路,其特征在于,包括:

2.根据权利要求1所述的上电自动校正vco增益的cdr电路,其特征在于:

3.根据权利要求2所述的上电自动校正vco增益的cdr电路,其特征在于:

4.根据权利要求3所述的上电自动校正vco增益的cdr电路,其特征在于:

5.根据权利要求4所述的上电自动校正vco增益的cdr电路,其特征在于:

6.根据权利要求5所述的上电自动校正vco增益的cdr电路,其特征在于:

技术总结本发明公开了一种上电自动校正VCO增益的CDR电路。为解决VCO增益存在差异或变化的技术问题,本发明中的CDR电路,通过镜像VCO中的多个可变电容,并以恒定的电流和预设时长对镜像可变电容进行充电,通过比较镜像可变电容的电压的值和参考电压的值,获得一组比较器输出信号的翻转信息,由此确定VCO中的一个可变电容为选定可变电容,并将该选定可变电容接入VCO。本发明消除了VCO增益存在的差异或变化问题,改善了CDR电路的输出信号抖动性能。本发明适于集成电路领域。技术研发人员:请求不公布姓名,请求不公布姓名,请求不公布姓名,请求不公布姓名,请求不公布姓名受保护的技术使用者:成都电科星拓科技有限公司技术研发日:技术公布日:2024/7/15本文地址:https://www.jishuxx.com/zhuanli/20240801/245144.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 YYfuon@163.com 举报,一经查实,本站将立刻删除。

下一篇

返回列表