一种N位电容型数模转换器

- 国知局

- 2024-08-02 15:19:55

本发明属于模拟数字混合集成电路,具体为一种n位电容型数模转换器,适用于多电压域。

背景技术:

1、随着科学技术的进步,医学测量、无线通信等领域的高速发展,作为模拟信号与数字信号接口桥梁的模数转换器性能变得越来越重要。按照结构分类,模数转换器可以大致分为flash模拟数字转换器(flash adc)、逐次逼近型模拟数字转换器(saradc)、流水线型模拟数字转换器(pipeline adc)、sigma-delta模拟数字转换器(sigma-delta adc)等几类。在高速领域应用较多的是传统逐次逼近型模数转换器。

2、在传统逐次逼近型模数转换器量化过程中,电容型模数转换器(cdac)由sar控制逻辑下建立参考电压与采样的输入电压进行比较,sar控制逻辑根据比较结果控制dac阵列开关继续切换,将新建立的参考电压再次进行比较,重复以上步骤,最终将dac阵列产生的参考电压逐次逼近到输入电压。

3、随着工艺制程的进步,mos管尺寸的减小,越来越多的设计采用低电压域来提高电路的速度、减小电路面积和功耗。传统设计中,相同精度的adc在低电压域量化噪声更小,因此对于比较器来说需要分辨更小的电压差以实现相应的精度,但是在电路设计中受制于工艺等因素比较器的失调与噪声无法消除,比较器很难达到要求的精度。所以若能在不需要提高比较器性能的情况下来实现高速和高精度adc的指标要求,将会更加利于行业当前的发展需求。

技术实现思路

1、针对上述存在的问题或不足,本发明提供了一种n位电容型数模转换器,通过引入双电压域,提高输入电压范围,在不需要进一步提高比较器性能的情况下增加了量化噪声以实现比较要求,比较器及sar逻辑部分仍采用低电压域以满足高速的设计要求。

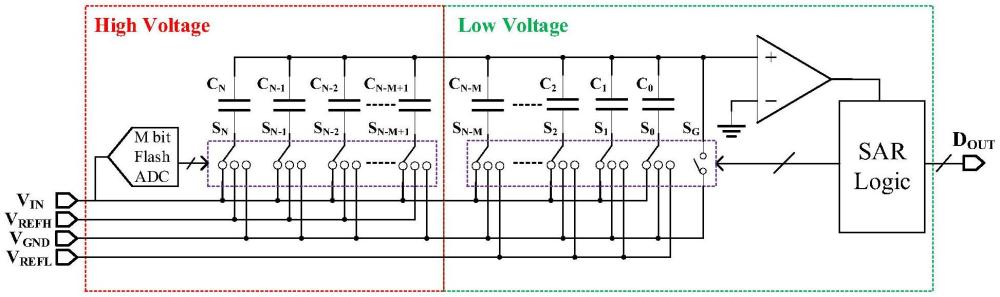

2、一种n位电容型数模转换器(如图1所示),包含高电压域和低电压域两部分电路。高电压域电路部分包含了m位flash adc和cdac的高m位开关电容。低电压域电路部分包含除cdac中高m位开关电容的剩余所有开关电容、比较器和sar逻辑部分。vrefh是高电压域的参考电压,vrefl是低电压域的参考电压,vgnd是地信号,vin是输入信号其输入范围是0~vrefh。

3、所述cdac包括n个量化电容c1-cn、补偿电容c0和上极板接地开关sg,电容共计n+1个;每个电容ci一一对应有一个三选一开关si,i在0-n中取值;其中c0=c1。

4、所述高电压域电路结构中,第1位量化电容cn下极板接三选一开关sn,三选一开关sn三个输入端分别接vin、vrefh和vgnd,其控制信号由m位flash adc提供;第2位量化电容cn-1下极板接三选一开关sn-1,三选一开关sn-1三个输入端分别接vin、vrefh和vgnd,其控制信号由m位flash adc提供;以此类推,第m位量化电容cn-m+1下极板接三选一开关sn-m+1,三选一开关sn-m+1三个输入端分别接vin、vrefh和vgnd,其控制信号由m位flash adc提供。

5、所述低电压域电路结构中,第m+1位量化电容cn-m下极板接三选一开关sn-m,三选一开关sn-m三个输入端分别接vin、vrefl和vgnd,其控制信号由sar逻辑提供;第m+2位量化电容cn-m-1下极板接三选一开关sn-m-1,三选一开关sn-m-1三个输入端分别接vin、vrefl和vgnd,其控制信号由sar逻辑提供;以此类推,第n位量化电容c1下极板接三选一开关s1,三选一开关s1三个输入端分别接vin、vrefl和vgnd,其控制信号由sar逻辑提供。补偿电容c0下极板接三选一开关s0,三选一开关s0三个输入端分别接vin、vrefl和vgnd,其控制信号由sar逻辑提供。

6、所有电容的上极板除了连接接地开关sg外,还连到比较器正输入端,在电压信号建立完成后传输给比较器。比较器负输入端接vgnd,输出端接sar逻辑模块。

7、进一步的,所述cdac中电容c0、c1外的其余量化电容取值根据具体设计选择,采用二进制取值或非二进制形式。

8、上述n位电容型数模转换器,其开关控制逻辑如下:

9、1、在采样阶段,cdac中cn~c0所有电容的下极板通过三选一开关接到输入信号vin,上极板通过接地开关sg接到vgnd,通过电容对输入信号vin进行采样,将电荷储存在上极板上。在采样阶段m位flash adc同时对输入信号vin进行采样,在采样阶段内完成对输入信号高m位的量化,并将高m位的量化结果提供给cdac高m位电容三选一sn~sn-m+1开关作为其控制信号。

10、2、根据采样阶段输入信号vin的高m位量化结果,如果量化结果为‘1’,控制三选一开关sn~sn-m+1的输入端接到vrefh;如果量化结果为‘0’,控制三选一开关sn~sn-m+1的输入端接到vgnd。剩余三选一开关sn-m~s0的控制信号由sar逻辑提供,在采样完成后都接到vgnd,接地开关sg断开。

11、3、完成高m位的开关sn~sn-m+1切换后,开始低n-m位的量化,在低位量化过程中三选一开关sn~sn-m+1输入端电位保持不变。

12、量化第m+1位,首先将三选一开关sn-m的输入端接到vrefl,三选一开关sn-m-1~s0的输入端接到vgnd,在开关切换cdac上极板电压建立完成后,比较器将cdac的上极板电压vp与vgnd进行比较,根据比较结果判断第m+1位量化电容cn-m的下极板接vrefl还是vgnd。若vp>vgnd,三选一开关sn-m的输入端接vgnd;若vp<vgnd,三选一开关sn-m的输入端接vrefl。在三选一开关sn-m切换后,完成第m+1位的量化过程,得到相应量化结果。

13、量化第m+2位,将三选一开关sn-m-1的输入端接到vrefl,三选一开关sn-m-2~s0的输入端接到vgnd,三选一开关sn-m根据前面的量化结果(第m+1位)接到vrefl或vgnd。在开关切换cdac上极板电压建立完成后,比较器将cdac的上极板电压vp与vgnd进行比较,根据比较结果判断第m+2位量化电容cn-m-1的下极板接vrefl还是vgnd。若vp>vgnd,三选一开关sn-m-1的输入端接vgnd;若vp<vgnd,三选一开关sn-m-1的输入端接vrefl。在三选一开关sn-m-1切换后,完成第m+2位的量化过程,得到相应量化结果。

14、以此类推,量化第n位,将三选一开关s1的输入端接到vrefl,三选一开关s0的输入端接到vgnd,三选一开关sn-m~s2根据前面的量化结果接到vrefl或vgnd。在开关切换cdac上极板电压建立完成后,比较器将cdac的上极板电压vp与vgnd进行比较,根据比较结果判断第n位量化电容c1的下极板接vrefl还是vgnd。若vp>vgnd,把三选一开关s1的输入端接vgnd;若vp<vgnd,把三选一开关s1的输入vrefl。在三选一开关s1切换后,完成第n位的量化过程,得到相应量化结果。

15、4、在低n-m位量化完成后,结合m位flashadc的高m位量化结果,得到输入信号vin的n位量化结果,完成一个采样周期的量化过程。

16、综上所述,本发明基于奈奎斯特带宽内均方根量化噪声公式:(其中),对于相同精度的adc在输入电压范围越大量化噪声越大;从而通过引入双电压域,提高输入电压范围,在不需要进一步提高比较器性能的条件下增加了量化噪声以实现比较要求,比较器及sar逻辑部分仍采用低电压域以满足高速的设计要求。

本文地址:https://www.jishuxx.com/zhuanli/20240801/245658.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 YYfuon@163.com 举报,一经查实,本站将立刻删除。