一种基于FPGA的低资源消耗滤波器及实现方法与流程

- 国知局

- 2024-08-02 15:41:29

本发明涉及数字信号处理领域,特别是一种基于fpga的低资源消耗滤波器及实现方法。

背景技术:

1、fpga是一种将门阵列的通用结构与pld的现场可编程特性结合于一体的计算平台,具有集成度高、通用性好、设计灵活、产品上市快捷等多方面的优点,属于可编程的专用集成电路。

2、滤波器是一种典型的数字信号处理方法,滤波处理能够滤除干扰噪声,提取有用信号,在雷达、声纳、通信、地震勘探、生物医学、工业技术等领域广泛应用。滤波器通常分为无限冲激响应(iir)滤波器和有限冲激响应(fir)滤波器两种类型,iir型滤波器的传输函数含有零点和极点,可以使用不高的阶数来实现,但相位非线性;fir滤波器为全零点滤波器,高性能fir滤波器往往阶数较高,但具有稳定性,且相位特性是线性的。在数字信号处理系统中,因fir滤波器可以采用非递归方式实现,有限精度下能够避免震荡的产生,具备严格的线性相位特性,有丰富的辅助设计工具进行计算和设计,因此fpga处理平台中,fir滤波器的应用较为广泛。

3、fir滤波器的实现方法按照结构主要可以分为:直接型、转置型。直接型fir滤波器对数据进行乘法、加法运算,n阶直接型fir滤波器需要n次乘法和2n(1-(1/2)n)次加法,其实现结构如图1和图2所示。转置型fir滤波器对数据进行移位、乘法、加法操作,n阶直接型fir滤波器需要n次乘法和(n-1)次加法,其实现结构如图3所示。

4、实际工程应用中,为了获得陡峭的过渡带和线性相位特性,需要使用较高阶数fir滤波器,增加了乘法器资源的消耗。而数字化信道应用通常使用数个滤波器将宽带信道划分成多个独立的子信道,为了能够划分更多的子信道,往往需要大量使用陡峭边界的滤波器,其性能严重受到fpga中的乘法器资源限制。

技术实现思路

1、针对现有技术中存在的上述不足,本发明实施例提供一种基于fpga的低资源消耗fir滤波器及实现方法。

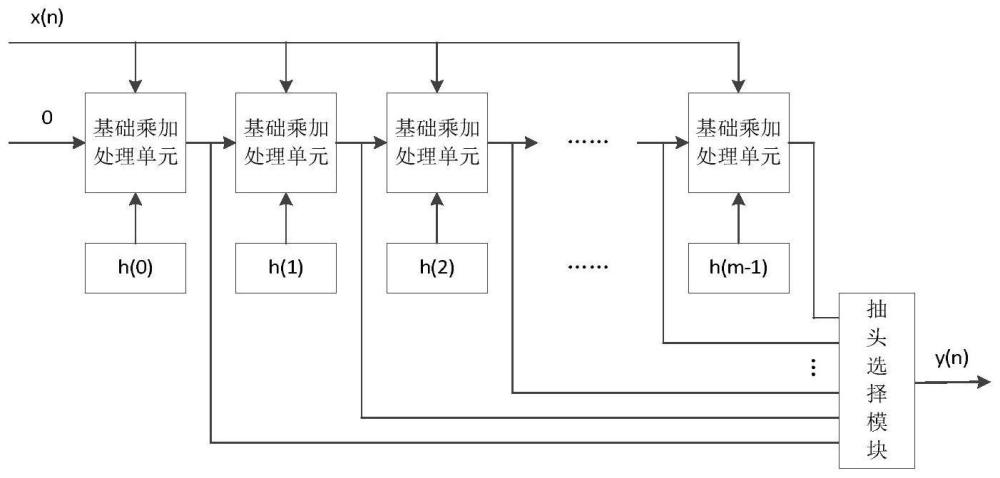

2、第一方面,本发明实施例还提供一种基于fpga的低资源消耗fir滤波器,其特征在于,包括:m个基础乘加处理单元以及抽头选择模块,所述基础处理单元为基础乘加处理单元,所述基础乘加处理单元包括乘法器和加法器,

3、所述基础乘加处理单元的一个输入端为输入信号x(n),其中n指输入信号的采样点数,各个基础乘加处理单元之间逐级连接,所述基础乘加处理单元的另一个输入端接收上一级基础乘加处理单元输出的求和结果s(m-1),输出本级求和结果s(m)到下一个连接的基础乘加处理单元;所述抽头选择模块的输入端为各级基础乘加处理单元的求和结果s(m),抽头选择模块进行抽头选择,选择从哪一级s(m)输出,输出结果y(n),实现任意长度滤波器的切换。

4、在一些实施例中,所述抽头选择模块为多路选通器,具备从多个输入信号中选择单个信号进行输出的功能,通过选通输出功能改变选择滤波器输出级数,实现任意长度滤波器的切换。

5、在一些实施例中,所述基础乘加处理单元的另一个输入端为滤波器系数h(m),抽头选择模块根据滤波器系数h(m)进行抽头选择,输出结果y(n)。

6、在一些实施例中,还包括:非均匀量化模块,所述基础处理单元为移加单元;

7、所述移加单元的一个输入端为输入信号x(n),其中n指输入信号的采样点数,各个移加单元之间逐级连接,所述移加单元的另一个输入端接收上一级移加单元输出的求和结果s(m-1),输出本级求和结果s(m)到下一个连接的移加单元;滤波器系数h(m)经过所述非均匀量化模块输出量化后的滤波器系数h′(m),抽头选择模块进行抽头选择,输出结果y(n),选择从哪一级s(m)输出,实现任意长度滤波器的切换。

8、在一些实施例中,所述非均匀量化模块包括非均匀量化计算模块和锁存模块;

9、所述非均匀量化计算模块用于将滤波器系数h(m)进行2的整数次幂量化,通过移位实现乘法运算,得到量化后的滤波器系数h′(m),滤波器系数量化后,基础乘加处理单元中的乘法改为移位;

10、所述锁存模块用于锁存和输出量化后的系数,实现滤波器系数的实时计算和更新。

11、在一些实施例中,所述基础乘加处理单元的另一个输入端为量化后的滤波器系数h′(m),抽头选择模块根据量化后的滤波器系数h′(m)进行抽头选择,输出结果y(n)。

12、第二方面,本发明实施例还提供一种基于fpga的低资源消耗fir滤波器实现方法,用于实现第一方面所述的基于fpga的低资源消耗fir滤波器,包括:

13、利用数字滤波器设计工具,设计滤波器系数h(m);

14、利用转置型架构对所述基于fpga的低资源消耗fir滤波器进行模块设计;

15、对所述基于fpga的低资源消耗fir滤波器的滤波器系数非均匀量化,得到量化后的滤波器系数h′(m)。

16、在一些实施例中,利用数字滤波器设计工具,设计滤波器系数h(m),包括:

17、根据滤波器类型、滤波器阶数、通带频率、阻带频率、通带波纹、阻带衰减设计滤波器系数h(m)。

18、在一些实施例中,进行滤波器资源优化后,阻带衰减范围为15db~20db。

19、在一些实施例中,对所述基于fpga的低资源消耗fir滤波器的滤波器系数非均匀量化,得到量化后的滤波器系数h′(m),包括;

20、将滤波器系数h(m)进行2的整数次幂量化,通过移位实现乘法运算,得到量化后的滤波器系数h′(m):

21、

22、滤波器系数量化后,基础乘加处理单元中的乘法改为移位,基础乘加处理单元改为移加单元。

23、本方明中,实现过程中采用模块化实现思路,先实现一个基础处理单元,通过基础处理单元的组合实现fir滤波器功能的实现。所述基础处理单元包括基础乘加处理单元和移加单元。从直接型的n次乘法和2n(1-(1/2)n)次加法降低为仅需要(n-1)次加法。该架构的fir滤波器除了低资源消耗的优点,还具备变阶数、变系数的功能,能够实时修改滤波器系数h(m)和输出结果y(n)的抽头选择,实现任意滤波器阶数和系数切换。

技术特征:1.一种基于fpga的低资源消耗fir滤波器,其特征在于,包括:m个基础处理单元以及抽头选择模块,所述基础处理单元为基础乘加处理单元,所述基础乘加处理单元包括乘法器和加法器,

2.根据权利要求1所述的基于fpga的低资源消耗fir滤波器,其特征在于,所述抽头选择模块为多路选通器,具备从多个输入信号中选择单个信号进行输出的功能,通过选通输出功能改变选择滤波器输出级数,实现任意长度滤波器的切换。

3.根据权利要求1所述的基于fpga的低资源消耗fir滤波器,其特征在于,所述基础乘加处理单元的另一个输入端为滤波器系数h(m),抽头选择模块根据滤波器系数h(m)进行抽头选择,输出结果y(n)。

4.根据权利要求1所述的基于fpga的低资源消耗fir滤波器,其特征在于,还包括:非均匀量化模块,所述基础处理单元为移加单元;

5.根据权利要求4所述的基于fpga的低资源消耗fir滤波器,其特征在于,所述非均匀量化模块包括非均匀量化计算模块和锁存模块;

6.根据权利要求5所述的基于fpga的低资源消耗fir滤波器,其特征在于,所述基础乘加处理单元的另一个输入端为量化后的滤波器系数h′(m),抽头选择模块根据量化后的滤波器系数h′(m)进行抽头选择,输出结果y(n)。

7.一种基于fpga的低资源消耗fir滤波器实现方法,其特征在于,用于实现权利要求1-6任意一项所述的基于fpga的低资源消耗fir滤波器,包括:

8.根据权利要求7所述的基于fpga的低资源消耗fir滤波器实现方法,其特征在于,利用数字滤波器设计工具,设计滤波器系数h(m),包括:

9.根据权利要求7所述的基于fpga的低资源消耗fir滤波器实现方法,其特征在于,进行滤波器资源优化后,阻带衰减范围为15db~20db。

10.根据权利要求7所述的基于fpga的低资源消耗fir滤波器实现方法,其特征在于,对所述基于fpga的低资源消耗fir滤波器的滤波器系数非均匀量化,得到量化后的滤波器系数h′(m),包括;

技术总结本发明公开了一种基于FPGA的低资源消耗FIR滤波器及实现方法,所述FIR滤波器包括:m个基础处理单元以及抽头选择模块,基础处理单元为基础乘加处理单元,基础乘加处理单元包括乘法器和加法器,基础乘加处理单元的一个输入端为输入信号x(n),其中n指输入信号的采样点数,各个基础乘加处理单元之间逐级连接,基础乘加处理单元的另一个输入端接收上一级基础乘加处理单元输出的求和结果s(m‑1),输出本级求和结果s(m)到下一个连接的基础乘加处理单元;抽头选择模块的输入端为各级基础乘加处理单元的求和结果s(m),抽头选择模块进行抽头选择,选择从哪一级s(m)输出,输出结果y(n),实现任意长度滤波器的切换。FIR滤波器除了低资源消耗的优点,还能够实现任意滤波器阶数和系数切换。技术研发人员:杨健,刘智成,魏云龙,苏毅,尚佳栋,包涵受保护的技术使用者:北京遥感设备研究所技术研发日:技术公布日:2024/7/25本文地址:https://www.jishuxx.com/zhuanli/20240801/247275.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 YYfuon@163.com 举报,一经查实,本站将立刻删除。

下一篇

返回列表