可选分辨率、可自适应校准时间的大量程时间数字转换器

- 国知局

- 2024-08-02 15:50:53

本技术的实施例涉及数字化测量,特别涉及一种可选分辨率、可自适应校准时间的大量程时间数字转换器。

背景技术:

1、时间数字转换器(time to digital converter,简称:tdc)是一种高精度的,能够将时间量转化为数字量的测量模块,广泛应用在医疗、工业和军事等领域之中,包括正电子发射断层成像(positron emission computed tomography,简称:pet)、荧光寿命成像、组织光学检测、扩散光学断层成像(diffuse optical tomography,简称:dot)、激光雷达测距、核物理和量子光学等。

2、tdc的实现架构包括两种,一种是特定应用集成电路(application-specificintegrated circuit,简称:asic)架构,另一种是现场可编程门阵列(field programmablegate array,简称:fpga)架构。目前市面上有基于asic实现的tdc,虽然具有线性度好、稳定可靠等优点,但其设计周期长、灵活性差、通道数固定、并且流片成本高。fpga本质上是一种半定制化的asic,由大量的可编程逻辑门和片内互连资源组成,用户可通过硬件描述语言更改其内部电路结构,实现所需功能。fpga可以实现与asic相近的功能,并且具有多通道并行处理、灵活性强的优势,tdc的分辨率需要达到皮秒级,基于fpga实现的tdc可以达到此量级。基于fpga实现的tdc,通常可以采用直接计数法、时钟分相法、差分延迟法和时钟内插法等方法实现,综合比较资源消耗量和实现难易度,时钟内插法是最佳方法。

3、tdc的核心参数包括动态范围(又称为量程)、分辨率、微分非线性(differentialnon-linearity,简称:dnl)和积分非线性(integral nonlinearity,简称:inl)。对于动态范围与分辨率这两个参数,不同的应用所需求的动态范围和分辨率是不同的,但业内使用的基于fpga实现的tdc的动态范围和分辨率在设计完成之后就已经确定,无法改变,对于不同动态范围和分辨率需求的场景只能重新设计。另外,基于fpga实现的tdc的延迟链的非线性相较于基于asic实现的tdc的较差,受温度、电压波纹和制作工艺等因素影响较大,一直使用一次标定的非线性并不科学,重新进行非线性标定则需要消耗大量的时间,并且重新标定的过程tdc需要暂停工作。

技术实现思路

1、本技术的实施例的主要目的在于提出一种可选分辨率、可自适应校准时间的大量程时间数字转换器,可适用于不同分辨率要求的场景中,实现大动态范围的时间数字转化,通过设置伴随链结构的方式,在不影响tdc正常工作的情况下及时更新延迟链结构的非线性,有效提升了tdc的转换性能。

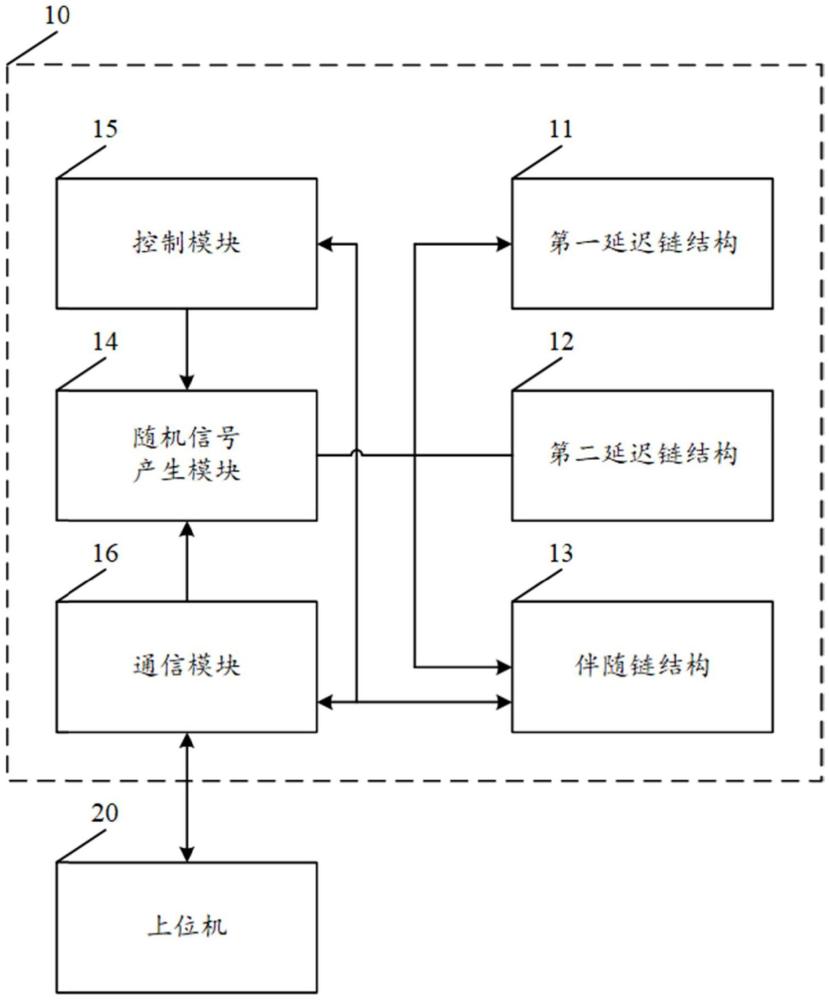

2、为实现上述目的,本技术的实施例提供了一种可选分辨率、可自适应校准时间的大量程时间数字转换器,包括结构相同的第一延迟链结构、第二延迟链结构和伴随链结构,以及随机信号产生模块,所述第一延迟链结构对应的分辨率大于所述第二延迟链结构对应的分辨率,所述第一延迟链结构和所述第二延迟链结构中均设置有大量程测量模块,所述大量程测量模块由一级寄存器和二级寄存器组成;在本次数据采集开始前,选择由所述第一延迟链结构或选择由所述第二延迟链结构来执行本次数据采集;在本次数据采集开始后,所述随机信号产生模块产生随机信号,所述伴随链结构采集所述随机信号,所选择的延迟链结构利用自身的大量程测量模块进行时间数字转换;其中,当所述大量程测量模块的一级寄存器存满后,二级寄存器的计数加1,同时对一级寄存器的计数清零;当所述伴随链结构的采集次数达到预设的分析阈值后,对所述伴随链结构进行非线性分析,若所述伴随链结构的非线性程度大于预设的校准阈值,则重新对所述所选择的延迟链结构进行非线性标定。

3、为实现上述目的,本技术的实施例还提供了一种时间数字转换系统,所述时间数字转换系统至少包括如上述所述的可选分辨率、可自适应校准时间的大量程时间数字转换器。

4、为实现上述目的,本技术的实施例还提供了一种时间数字转换方法,应用于如上述所述的可选分辨率、可自适应校准时间的大量程时间数字转换器,所述大量程时间数字转换器由结构相同的第一延迟链结构、第二延迟链结构和伴随链结构,以及随机信号产生模块组成,所述第一延迟链结构对应的分辨率大于所述第二延迟链结构对应的分辨率,所述第一延迟链结构和所述第二延迟链结构中均设置有大量程测量模块,所述大量程测量模块由一级寄存器和二级寄存器组成,所述方法包括:根据分辨率需要,选择由所述第一延迟链结构或选择由所述第二延迟链结构来执行本次数据采集;控制所述随机信号产生模块产生随机信号,通过所述伴随链结构采集所述随机信号,并通过所选择的延迟链结构基于所述随机信号,利用自身的大量程测量模块进行时间数字转换;其中,当所述大量程测量模块的一级寄存器存满后,所述寄存器的计数加1,同时对一级寄存器的计数清零;检测所述伴随链结构的采集次数是否达到预设的分析阈值,若检测到所述伴随链结构的采集次数达到所述分析阈值,则对所述伴随链结构进行非线性分析;检测所述伴随链结构的非线性程度是否大于预设的校准阈值,若检测到所述伴随链结构的非线性程度大于所述校准阈值,则重新对所述所选择的延迟链结构进行非线性标定。

5、为实现上述目的,本技术的实施例还提供了一种计算机可读存储介质,存储有计算机程序,所述计算机程序被处理器执行时实现上述所述的时间数字转换方法。

6、本技术的实施例提出的可选分辨率、可自适应校准时间的大量程时间数字转换器,针对于业内的基于fpga实现的tdc的量程和分辨率在设计完成时已固定、重新进行非均匀性标定需要消耗大量的时间并且重新标定的过程tdc需要暂停工作的问题,设置了由结构相同的第一延迟链结构、第二延迟链结构和伴随链结构,以及随机信号产生模块组成的时间数字转换器实现分辨率可选、大动态范围和非线性重新标定。两个延迟链结构中,第一延迟链结构对应的分辨率大于第二延迟链结构对应的分辨率,在时间数字转换器开始工作前,根据需要选择由第一延迟链结构或第二延迟链结构来执行本次数据采集,使得该时间数字转换器能够适用于不同分辨率要求的场景中。两个延迟链结构中都设置了由一级寄存器和二级寄存器组成的大量程测量模块,大量程测量模块的一级寄存器存满后,二级寄存器的计数加1,同时对一级寄存器的计数清零,量程大幅增加,能够实现大动态范围的时间数字转化。伴随链结构的设置则可以在不影响数字时间转换器的正常工作的情况下,及时更新所选择的延迟链结构的非线性,提升了数字时间转换器的延迟链结构的非线性的准确性,从而有效提升了数字时间转换器的转换性能。

7、在一些可选的实施例中,所述大量程时间数字转换器还包括控制模块,所述预设的校准阈值预先存储在所述控制模块内部的存储单元中;所述控制模块用于检测所述伴随链结构的采集次数是否达到预设的分析阈值,在检测到所述伴随链结构的采集次数达到所述分析阈值的情况下,基于所述校准阈值对所述伴随链结构进行非线性分析,若所述伴随链结构的非线性程度大于所述校准阈值,则重新对所述所选择的延迟链结构进行非线性标定。

8、在一些可选的实施例中,所述大量程时间数字转换器还包括通信模块,所述通信模块与上位机之间建立有通信连接,所述预设的校准阈值预先在所述上位机上进行设置;所述上位机用于检测所述伴随链结构的采集次数是否达到预设的分析阈值,在检测到所述伴随链结构的采集次数达到所述分析阈值的情况下,基于所述校准阈值对所述伴随链结构进行非线性分析,若所述伴随链结构的非线性程度大于所述校准阈值,则重新对所述所选择的延迟链结构进行非线性标定。

9、在一些可选的实施例中,所述控制模块还用于在本次数据采集开始前,通过所述随机信号产生模块,对所述第一延迟链结构和所述第二延迟链结构进行码密度检测,即对所述第一延迟链结构和所述第二延迟链结构进行非线性标定。

10、在一些可选的实施例中,所述所选择的延迟链结构中包括两条延迟链,一条作为start延迟链,另一条作为stop延迟链;所述所选择的延迟链结构在所述start延迟链收到start信号后,每来临一个时钟周期,将自身的大量程测量模块的一级寄存器的计数加1,当所述一级寄存器存满后,将自身的大量程测量模块的二级寄存器的计数加1,同时对所述一级寄存器的计数清零,直到所述stop延迟链收到stop信号时停止;所述所选择的延迟链结构最终的计数的数值,通过以下公式表示:

11、tfinal=(k×l+times)×tclk

12、其中,k表示所述一级寄存器存满时的容量,l表示所述一级寄存器存满的次数,times表示所述stop延迟链收到所述stop信号时所述一级寄存器的数值,tclk表示系统时钟的周期,tfinal表示所述所选择的延迟链结构最终的计数的数值。

13、在一些可选的实施例中,所述随机信号产生模块产生的随机信号的频率具有与系统时钟的频率完全不相关的特性。

14、在一些可选的实施例中,所述第一延迟链结构对应的分辨率是所述第二延迟链结构对应的分辨率的4倍。

本文地址:https://www.jishuxx.com/zhuanli/20240801/248146.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 YYfuon@163.com 举报,一经查实,本站将立刻删除。

下一篇

返回列表