用于四通道交织模数转换器的采样保持电路及模数转换器

- 国知局

- 2024-08-02 15:52:49

本文件涉及,尤其涉及一种用于四通道交织模数转换器的采样保持电路及模数转换器。

背景技术:

1、如今高速高精度模数转换器adc广泛应用于无线通信等领域,对采样输入信号的带宽提出了越来越高的要求,时间交织型adc目前已成为高速模数转换的主流架构之一,而采样保持电路作为输入信号转换传递过程中的最前级,对于adc整体性能来说至关重要,采样保持电路的作用一是用于隔离输入信号与量化网络,减少adc量化网络的回踢噪声对输入信号造成的非线性影响。二是对输出负载的较强驱动能力,可以使小功率的前级输入信号更易驱动后级高精度的量化ad电路。高带宽的采样保持电路已成为如今adc系统的设计瓶颈,研究者们采用一系列方式方法提高采样保持电路动态性能。

2、传统结构中为了提高线性度和带宽,采用的方法是增加直流偏置电流但是这种电流的增加往往会要求管子的尺寸变大,这反而又增加了寄生电容,即使传统缓冲器结构付出了功耗增大的代价,最终还是由于寄生电容的原因以及一些非理想效应和输入信号的依赖关系,限制了该结构可实现的最大线性度。并且输出端电压变化使得输入管的漏源vds电压变化,进而输出阻抗非线性更加严重。

技术实现思路

1、本发明提供了一种采样保持电路及模数转换器,旨在解决上述问题。

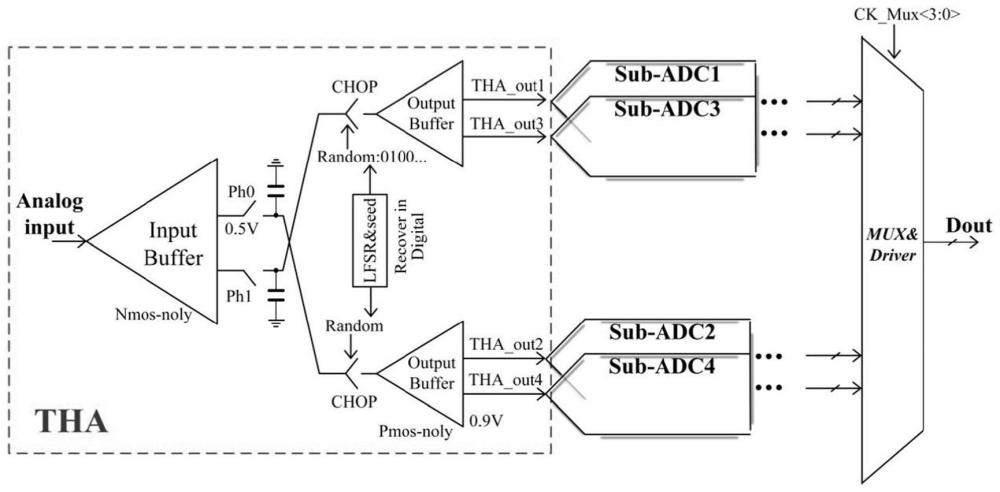

2、本发明提供了一种采样保持电路,包括:input buffer模块以及两通道outputbuffer模块,

3、input buffer模块对输入信号进行第一级双相位采样产生两相非交叠时钟,驱动两通道output buffer;根据prbs31随机码产生电路对信号进行两通道斩波采样,通过数字电压域进行采样斩波;

4、output buffer模块对信号进行再采样,驱动四通道子ad量化。

5、本发明提供了一种模数转换器,所述模数转换器包含上述任一实施例所述采样保持电路。

6、采用本发明实施例,提供了一种应用于四通道交织的高速模数转换器的采样保持电路结构,先将信号共模降低,通过数字电源域对其产生伪随机码,结合采用chop随机斩波技术,降低adc量化所产生的的低频噪声。分析源极跟随器非线性原因,input buffer模块使用nmos-noly结构、output buffer模块采用pmos-noly结构,结合正负双电压供电,并通过自举电路产生高电压供给栅压跟随,以提高整体adc系统的量化输入范围,并进一步提高采样保持电路的线性度及带宽。

技术特征:1.一种用于四通道交织模数转换器的采样保持电路,其特征在于,包括:input buffer模块以及两通道output buffer模块,

2.根据权利要求1所述的用于四通道交织模数转换器的采样保持电路,其特征在于,所述两通道斩波采样分别采用不同的伪随机码。

3.根据权利要求1所述的用于四通道交织模数转换器的采样保持电路,其特征在于,所述input buffer模块包括输入信号vin、输出信号vout、由vdd31电压产生id的偏置电路、主电路偏置电路、双电源vdd18、vddn06、电容c1、补偿电容c2、输入管m1、电流镜晶体管m4、反馈环路晶体管m3、m5、晶体管m2;

4.根据权利要求3所述的用于四通道交织模数转换器的采样保持电路,其特征在于,所述vdd31电压产生id的偏置电路包括:自举电路ph0、自举电路ph1以及输出电压ldo电路;

5.根据权利要求3所述的用于四通道交织模数转换器的采样保持电路,其特征在于所述vdd31电压产生电路实现输入管m2栅压对输入信号vin的高线性度跟随,以减小输入管的漏源电压vds的变化。

6.根据权利要求3所述的用于四通道交织模数转换器的采样保持电路,其特征在于,input buffer模块的主路电流镜及vdd31电压产生电路引入的电流镜均采用共源共栅结构,对输入管m1源端、vdd31及电源vdd抖动变化起到屏蔽作用。

7.据权利要求1所述的用于四通道交织模数转换器的采样保持电路,其特征在于,所述input buffer模块采用深n阱工艺,将输入管m1管衬底端与源端相连,以消除体效应对输入管m1的线性度影响。

8.根据权利要求1所述的用于四通道交织模数转换器的采样保持电路,其特征在于,所述两通道output buffer模块包括双电源vdd18、vddn06,电阻r1及r2,补偿电容c1,电容c2,输入管m3,晶体管m4,反馈环路晶体管m2、m5,电流镜晶体管m1;

9.根据权利要求1所述的用于四通道交织模数转换器的采样保持电路,其特征在于,所述两通道output buffer模块采用pmos-noly结构。

10.一种模数转换器,其特征在于,所述模数转换器包含权利要求1至权利要求9中任一项所述用于四通道交织模数转换器的采样保持电路。

技术总结本发明提供了一种用于四通道交织模数转换器的采样保持电路及模数转换器,其特征在于,采样保持电路包括:Input Buffer模块以及两通道Output Buffer模块,Input Buffer模块由两相非交叠时钟对输入信号进行第一级双相位采样,驱动两通道Output Buffer;根据PRBS31随机码对信号进行两通道随机斩波采样,其中通过数字电压域进行采样斩波;两路Output Buffer模块对信号进行再采样,驱动四通道子AD量化。本申请中主电路使用正负双电压供电,以提高整体ADC系统的量化输入范围,并通过自举电路产生3.1V高电压供给栅压跟随,进一步提高采样保持电路的线性度,并引入电流镜反馈环路;并结合采用CHOP随机斩波技术,降低ADC量化所产生的的低频噪声。技术研发人员:姜子林,吴旦昱,郭轩,贾涵博,陈鹏宇,王丹丹,刘新宇受保护的技术使用者:中国科学院微电子研究所技术研发日:技术公布日:2024/7/29本文地址:https://www.jishuxx.com/zhuanli/20240801/248339.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 YYfuon@163.com 举报,一经查实,本站将立刻删除。

下一篇

返回列表