一种防止共通的驱动电路的制作方法

- 国知局

- 2024-08-02 12:58:48

本发明涉及电子,具体但不限于涉及一种防止共通的驱动电路。

背景技术:

1、图1示出了一种常见的驱动电路。其中,mos管mp1、mn1构成一级反相器,mos管mp2、mn2构成二级反相器。它的工作原理如下:初始阶段,in处于低电平状态,mp2导通,mn2关断,a点电压维持在vcc,故mp1关断,mn1导通,out处于低电平状态。当in处于高电平状态,mp2关断,mn2导通,a点电压维持在gnd,故mp1导通,mn1关断,out处于高电平状态。

2、稳态下,经过一级反相器、二极反相器的放大,out处的电流远大于in处的电流,且out与in保持在同一状态,因此该驱动电路具备优秀的驱动能力。然而,当in处于低电平转为高电平这个过程中,a点电压不是由vcc瞬间转变成gnd,而是逐渐由vcc下降至gnd。因此,在某一短暂时段,存在mp1、mn1同时导通的情况,这种情况称呼为共通。当mp1、mn1共通,由于mp1、mn1导通时阻值很小,导致很大的共通电流,容易损坏mos管。

3、有鉴于此,需要提供一种新的结构或控制方法,以期解决上述至少部分问题。

技术实现思路

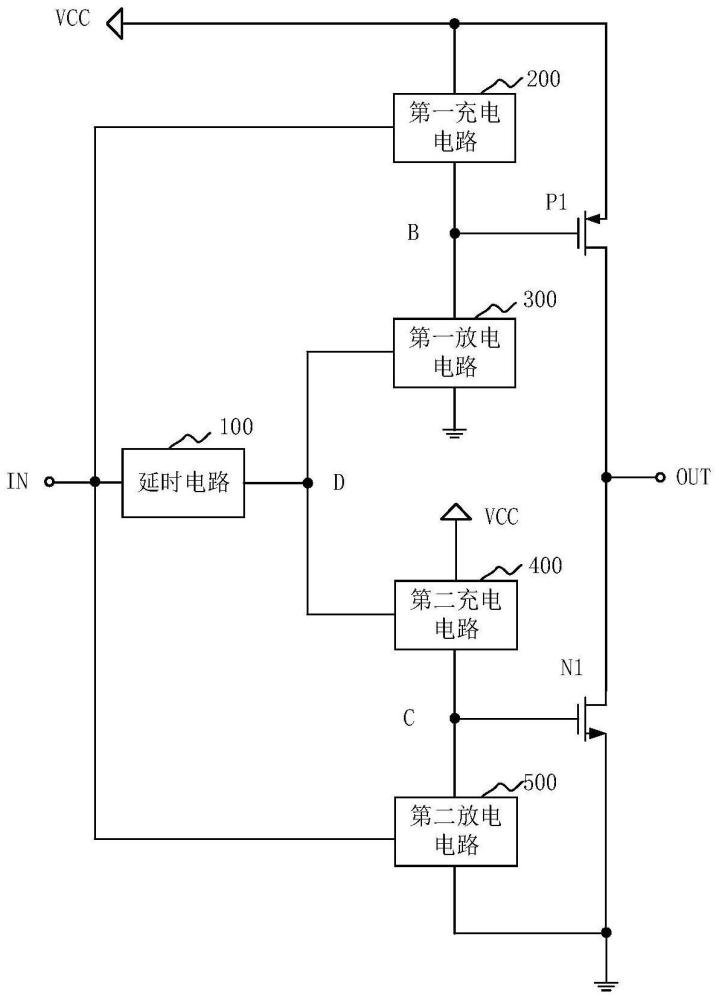

1、至少针对背景技术中的一个或多个问题,本发明提出了一种防止共通的驱动电路,能够避免共通的现象出现。

2、根据本发明的一个方面,一种防止共通的驱动电路,包括:

3、第一晶体管,所述第一晶体管在其控制端处于低电平状态下导通;

4、第二晶体管,所述第二晶体管在其控制端处于高电平状态下导通;

5、延时电路,用于延时输入信号,生成延时信号;

6、第一充电电路,具有输出端和控制端,其输出端耦接所述第一晶体管的控制端,其控制端耦接所述输入信号,所述第一充电电路用于在所述输入信号处于低电平状态时,对所述第一晶体管的控制端充电;

7、第一放电电路,具有输入端和控制端,其输出端耦接所述第一晶体管的控制端,其控制端耦接所述延时信号,所述第一放电电路用于在所述延时信号处于高电平状态时,对所述第一晶体管的控制端放电;

8、第二充电电路,具有输出端和控制端,其输出端耦接所述第二晶体管的控制端,其控制端耦接所述延时信号,所述第二充电电路用于在所述延时信号处于低电平状态时,对所述第二晶体管的控制端充电;

9、第二放电电路,具有输入端和控制端,其输入端耦接所述第二晶体管的控制端,其控制端耦接所述输入信号,所述第二放电电路用于在所述输入信号处于高电平状态时,对所述第二晶体管的控制端放电;

10、其中,所述第一充电电路的充电电流大于所述第一放电电路的放电电流,所述第二充电电路的充电电流小于所述第二放电电路的放电电流。

11、可选地,所述第一充电电路包括第三晶体管,所述第三晶体管具有第一端、第二端和控制端,所述第三晶体管的第一端耦接高电平,所述第三晶体管的第二端耦接所述第一晶体管的控制端,所述第三晶体管的控制端耦接所述输入信号。

12、可选地,所述第一放电电路包括第四晶体管,所述第四晶体管具有第一端、第二端和控制端,所述第四晶体管的第一端耦接所述第一晶体管的控制端,所述第四晶体管的第二端耦接参考地,所述第四晶体管的控制端耦接所述延时信号。

13、可选地,所述第二充电电路包括第五晶体管,所述第五晶体管具有第一端、第二端和控制端,所述第五晶体管的第一端耦接高电平,所述第五晶体管的第二端耦接所述第二晶体管的控制端,所述第五晶体管的控制端耦接所述延时信号。

14、可选地,所述第二放电电路包括第六晶体管,所述第六晶体管具有第一端、第二端和控制端,所述第六晶体管的第一端耦接所述第二晶体管的控制端,所述第六晶体管的第二端耦接参考地,所述第六晶体管的控制端耦接所述输入信号。

15、可选地,所述延时电路包括:第七晶体管,具有第一端、第二端和控制端,其第一端耦接高电平,其第二端耦接第八晶体管的第一端,其控制端耦接所述输入信号,所述第七晶体管用于在所述输入信号处于低电平状态时导通;第八晶体管,具有第一端、第二端和控制端,其第一端耦接所述第七晶体管的第二端,其第二端耦接参考地,其控制端耦接所述输入信号,所述第八晶体管用于在所述输入信号处于高电平状态时导通;第九晶体管,具有第一端、第二端和控制端,其第一端耦接高电平,其第二端耦接第十晶体管的第一端,其控制端耦接所述第七晶体管的第二端,所述第九晶体管用于在其控制端处于低电平状态时导通;第十晶体管,具有第一端、第二端和控制端,其第一端耦接所述第九晶体管的第二端,其第二端耦接参考地,其控制端耦接所述第七晶体管的第二端,所述第十晶体管用于在其控制端处于高电平状态时导通。

16、可选地,所述驱动电路还包括第十一晶体管,所述第十一晶体管具有第一端、第二端和控制端,所述第十一晶体管的第一端耦接高电平,所述第十一晶体管的第二端耦接所述第一放电电路的控制端,所述第十一晶体管的控制端耦接所述第一充电电路的输出端,所述第十一晶体管用于在其控制端处于低电平状态时导通,对所述第一放电电路的控制端充电。

17、可选地,所述驱动电路还包括第十二晶体管,所述第十二晶体管具有第一端、第二端和控制端,所述第十二晶体管的第一端耦接所述第二充电电路的控制端,所述第十二晶体管的第二端耦接参考地,所述第十二晶体管的控制端耦接所述第二放电电路的输入端,所述第十二晶体管用于在其控制端处于高电平状态时导通,对所述第二充电电路的控制端放电。

18、本发明提出的一种防止共通的驱动电路,包括第一晶体管、第二晶体管、延时电路、第一充电电路、第一放电电路、第二充电电路和第二放电电路。其中,第一充电电路和第一放电电路分别用于对第一晶体管的控制端进行充电和放电,以分别控制第一晶体管关断和导通,第二充电电路和第二放电电路分别用于对第二晶体管的控制端进行充电和放电,以分别控制第二晶体管关断和导通。延时电路用于对输入信号进行延时处理,当输入信号由低电平转高电平,或由高电平转低电平时,由于对输入信号进行了延时处理,因此第一晶体管和第二晶体管会延时导通,即第一晶体管、第二晶体管在输入信号电平转换阶段都处于关断状态,从而有效避免了共通现象的出现。

技术特征:1.一种防止共通的驱动电路,其特征在于,所述驱动电路包括:

2.如权利要求1所述的驱动电路,其特征在于,所述第一充电电路包括第三晶体管,所述第三晶体管具有第一端、第二端和控制端,所述第三晶体管的第一端耦接高电平,所述第三晶体管的第二端耦接所述第一晶体管的控制端,所述第三晶体管的控制端耦接所述输入信号。

3.如权利要求1所述的驱动电路,其特征在于,所述第一放电电路包括第四晶体管,所述第四晶体管具有第一端、第二端和控制端,所述第四晶体管的第一端耦接所述第一晶体管的控制端,所述第四晶体管的第二端耦接参考地,所述第四晶体管的控制端耦接所述延时信号。

4.如权利要求1所述的驱动电路,其特征在于,所述第二充电电路包括第五晶体管,所述第五晶体管具有第一端、第二端和控制端,所述第五晶体管的第一端耦接高电平,所述第五晶体管的第二端耦接所述第二晶体管的控制端,所述第五晶体管的控制端耦接所述延时信号。

5.如权利要求1所述的驱动电路,其特征在于,所述第二放电电路包括第六晶体管,所述第六晶体管具有第一端、第二端和控制端,所述第六晶体管的第一端耦接所述第二晶体管的控制端,所述第六晶体管的第二端耦接参考地,所述第六晶体管的控制端耦接所述输入信号。

6.如权利要求1所述的驱动电路,其特征在于,所述延时电路包括:

7.如权利要求1至6任一所述的驱动电路,其特征在于,所述驱动电路还包括第十一晶体管,所述第十一晶体管具有第一端、第二端和控制端,所述第十一晶体管的第一端耦接高电平,所述第十一晶体管的第二端耦接所述第一放电电路的控制端,所述第十一晶体管的控制端耦接所述第一充电电路的输出端,所述第十一晶体管用于在其控制端处于低电平状态时导通,对所述第一放电电路的控制端充电。

8.如权利要求7所述的驱动电路,其特征在于,所述驱动电路还包括第十二晶体管,所述第十二晶体管具有第一端、第二端和控制端,所述第十二晶体管的第一端耦接所述第二充电电路的控制端,所述第十二晶体管的第二端耦接参考地,所述第十二晶体管的控制端耦接所述第二放电电路的输入端,所述第十二晶体管用于在其控制端处于高电平状态时导通,对所述第二充电电路的控制端放电。

技术总结本发明提供了一种防止共通的驱动电路,包括第一晶体管、第二晶体管、延时电路、第一充电电路、第一放电电路、第二充电电路和第二放电电路。其中,第一充电电路和第一放电电路分别用于对第一晶体管的控制端进行充电和放电,以分别控制第一晶体管关断和导通,第二充电电路和第二放电电路分别用于对第二晶体管的控制端进行充电和放电,以分别控制第二晶体管关断和导通。延时电路用于对输入信号进行延时处理,当输入信号由低电平转高电平,或由高电平转低电平时,由于对输入信号进行了延时处理,因此第一晶体管和第二晶体管会延时导通,即第一晶体管、第二晶体管在输入信号电平转换阶段都处于关断状态,从而有效避免了共通现象的出现。技术研发人员:廖建平,李征洋,叶俊受保护的技术使用者:厦门市必易微电子技术有限公司技术研发日:技术公布日:2024/8/1本文地址:https://www.jishuxx.com/zhuanli/20240802/238342.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 YYfuon@163.com 举报,一经查实,本站将立刻删除。

下一篇

返回列表