一种铪基铁电存储器及其制造方法

- 国知局

- 2024-08-02 12:59:25

本发明涉及铁电存储器,尤其是涉及一种铪基铁电存储器及其制造方法。

背景技术:

1、随着电子信息产业的飞速发展,信息数据大量迭代增加,现有存储技术难以满足人们对高密度、高速度、低功耗存储的需求。为了达到上述需求,人们将研究方向集中于四种新型存储器,即相变存储器、磁存储器、阻变存储器和铁电存储器。相比于其它存储器,铁电存储器具有速度快、功耗低、可靠性高等优点。

2、目前,铁电存储器包括feram(ferroelectronic random access memory)、fefet(ferroelectric field effect transistor)和ftj(ferroelectric tunnel junction)三种类型。铪基铁电存储器可以微缩到纳米量级,同时与cmos工艺技术兼容。然而,与传统的钙钛矿基铁电存储器相比,铪基铁电存储器的击穿电压和耐久性显得不足,因此需要开发新的技术方法来提高铪基铁电存储器的击穿电压和耐久性。

3、鉴于此,特提出本发明。

技术实现思路

1、本发明的目的在于提供一种铪基铁电存储器及其制造方法,该制造方法提高了铪基铁电存储器的击穿电压和耐久性,使铪基铁电存储器具有更高的擦写次数。

2、本发明提供一种铪基铁电存储器的制造方法,包括如下步骤:

3、s1:在衬底上沉积下电极;

4、s2:在下电极上沉积铁电层;

5、s3:在铁电层沉积二氧化钛中间层;

6、s4:在二氧化钛中间层上沉积铁电层;

7、s5:在铁电层上淀积上电极;

8、s6:退火。

9、步骤s1中,衬底可以采用二氧化硅衬底,二氧化硅衬底的厚度为200-400nm,例如300nm。

10、下电极(be)的材质可以采用导电材料,例如tin、w、ru等导电材料,下电极的厚度可以为5-100nm,优选为30-50nm,更优选为40nm。此外,可以采用离子束溅射沉积法沉积下电极。

11、步骤s2、s4中,铁电层(fl)的材质为hf0.5zr0.5o2(hzo),铁电层的厚度为1-5nm,例如4.5nm。此外,可以采用原子层沉积法沉积铁电层,沉积温度可以为150-350℃,例如280℃。

12、步骤s3中,二氧化钛中间层(il)的厚度为0.1-0.9nm,例如0.5nm。此外,可以采用原子层沉积法沉积二氧化钛中间层,沉积温度可以为150-350℃,例如280℃。

13、步骤s5中,上电极(te)的材质可以采用导电材料,例如tin、w或ru,上电极的厚度为5-100nm,优选为30-50nm,更优选为40nm。此外,可以采用离子束溅射沉积法沉积下电极。

14、步骤s6中,对退火方式不作严格限制,任意可用于使铪基铁电具备铁电性的退火方式均可,包括但不限于在氮气氛围下进行快速热退火;具体地,可以在氮气氛围下进行退火,退火温度可以为300-700℃,退火时间可以为10-60s。

15、本发明还提供一种铪基铁电存储器,按照上述制造方法制得。

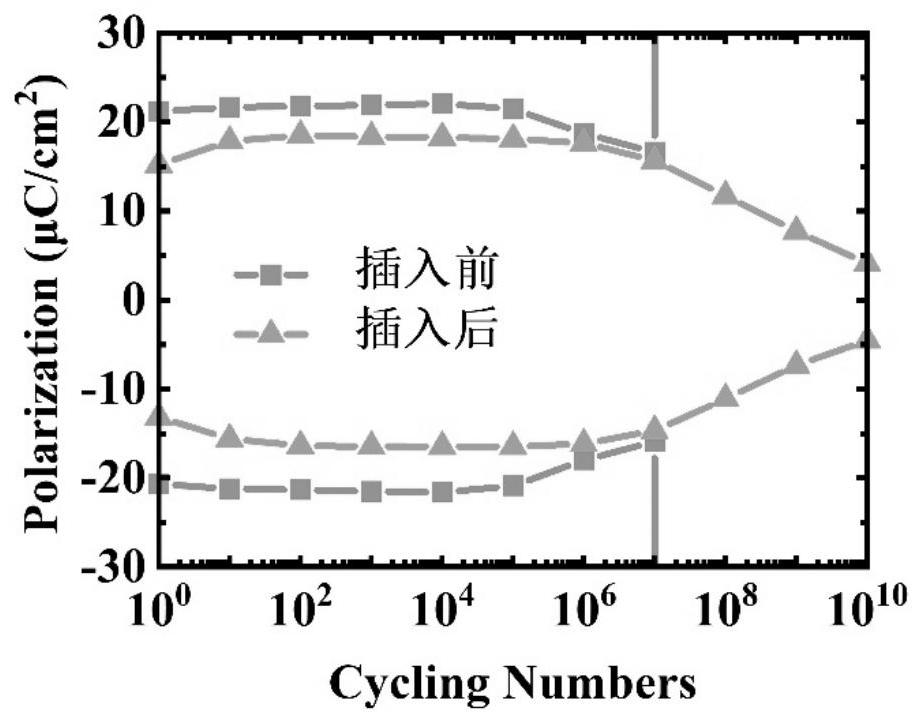

16、本发明提供了一种通过插入二氧化钛中间层来提高铪基铁电电容击穿电压及耐久性的方法,在插入二氧化钛中间层后,存储窗口2pr没有明显下降,而击穿电压提高了1v以上,特别是耐久性提高3个数量级,铪基铁电存储器的击穿电压和耐久性明显提高,从而使铪基铁电存储器具有更高的擦写次数。

技术特征:1.一种铪基铁电存储器的制造方法,其特征在于,包括如下步骤:

2.根据权利要求1所述的制造方法,其特征在于,衬底为二氧化硅衬底,二氧化硅衬底的厚度为200-400nm。

3.根据权利要求1所述的制造方法,其特征在于,下电极的材质为tin、w或ru,下电极的厚度为5-100nm。

4.根据权利要求1所述的制造方法,其特征在于,铁电层的材质为hf0.5zr0.5o2,铁电层的厚度为1-5nm。

5.根据权利要求1所述的制造方法,其特征在于,二氧化钛中间层的厚度为0.1-0.9nm。

6.根据权利要求1所述的制造方法,其特征在于,上电极的材质为tin、w或ru,上电极的厚度为5-100nm。

7.根据权利要求1所述的制造方法,其特征在于,采用离子束溅射沉积法沉积下电极和上电极。

8.根据权利要求1所述的制造方法,其特征在于,采用原子层沉积法沉积二氧化钛中间层和铁电层,沉积温度为150-350℃。

9.根据权利要求1所述的制造方法,其特征在于,在氮气氛围下进行退火,退火温度为300-700℃,退火时间为10-60s。

10.一种铪基铁电存储器,其特征在于,按照权利要求1-9任一所述的制造方法制得。

技术总结本发明提供了一种铪基铁电存储器及其制造方法。本发明的铪基铁电存储器的制造方法,包括如下步骤:S1:在衬底上沉积下电极;S2:在下电极上沉积铁电层;S3:在铁电层沉积二氧化钛中间层;S4:在二氧化钛中间层上沉积铁电层;S5:在铁电层上淀积上电极;S6:退火。本发明的制造方法提高了铪基铁电存储器的击穿电压和耐久性,使铪基铁电存储器具有更高的擦写次数。技术研发人员:王艳,陈远翔,罗庆,谢宏受保护的技术使用者:中国科学院微电子研究所技术研发日:技术公布日:2024/8/1本文地址:https://www.jishuxx.com/zhuanli/20240802/238365.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 YYfuon@163.com 举报,一经查实,本站将立刻删除。