存储装置、半导体器件及存储器系统的制作方法

- 国知局

- 2024-08-08 17:04:21

本发明涉及一种计算机存储装置,特别是涉及一种存储装置、半导体器件及存储器系统,其结构及连接技术被有利且非显而易见地应用于存储器测试和存储装置之间的连接,以及实现存储器系统。

背景技术:

1、动态随机存取存储器(dram)和闪存(flash memory)技术的发展已有多年历史。其基础技术基本保持不变,但接口会随着时间的推移及技术的进步而发生变化,例如快速页面模式(fpm)、扩展数据输出(edo)、同步dram(sdram)、双倍数据速率-1至4(ddr-1、ddr-2、ddr-3、ddr-4)等。

2、在存储器与存储器之间,或存储器模块与存储器模块之间,通常通过接线和/或焊接的方式连接。图1显示现有技术的一存储器组件的示意图,所述存储器组件例如是一dram组件。芯片11通过第一键合线12连接到第一基板13上。图5显示现有技术的另一存储器组件的示意图,图3显示现有技术的另一存储器组件的示意图。如图5及图3所示,当连接多个芯片11时,除了如图1所示的连接方式之外,芯片11也可以通过布线在芯片11边缘通过第一键合线12连接到第一基板13上。

3、图4显示现有技术的另一存储器组件的示意图。如图4所示,存储器组件包括第一芯片14及第二芯片15,其中第一芯片14上形成有金属柱16,例如是一铜柱。所述金属柱16上可具有一焊头161,所述焊头161可以被焊接到第二芯片15上,并通过第二芯片15上的布线在第二芯片15的边缘通过第二键合线17连接到第二基板18上,或者所述焊头161也可以被直接焊接到第二基板18。

4、请参考图5,图5显示现有技术的一存储器模块的示意图。如图5所示,数个存储器组件1通过焊球19连接到客户应用的印刷电路板(pcb)或模块基板上。

5、在上述应用中,焊球和铜柱连接的焊接工艺均属于热工艺,会使存储单元降解,从而降低成品率和产量,并给客户应用带来可靠性风险。

6、故此,有必要提供一种存储装置、半导体器件及存储器系统,以解决先前技术所存在的问题。

技术实现思路

1、本发明的动机在于提供一种存储装置、半导体器件及存储器系统,旨在解决并改善前述现有技术的问题与缺点。

2、本发明的主要目的在于提供一种存储装置、半导体器件及存储器系统,通过垂直形成于金属层上的多个纳米导电线进行连接,可避免热工艺造成的成品率降低及可靠性风险,同时因其优越的电气性能实现更好的产品性能和产量。

3、进一步地,通过应用垂直纳米导电线及其连接技术,可实现用于探测目的的临时、非永久性连接,同时可以直接在基板上安装芯片,从而处理未经测试的设备并提供新的功能。

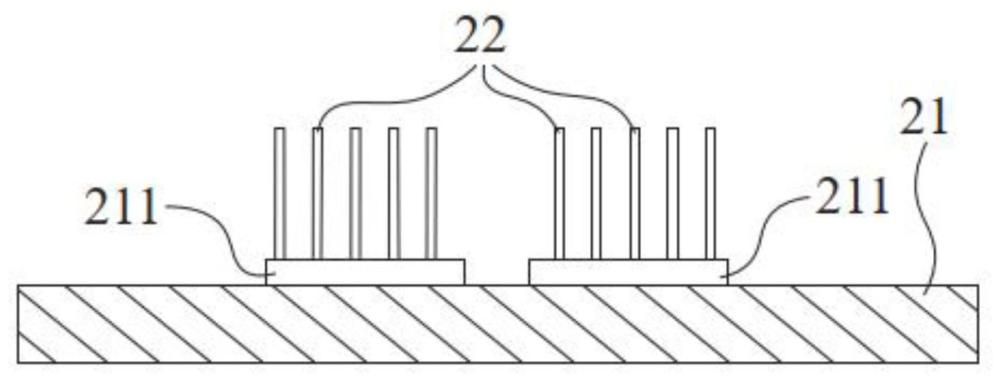

4、根据本发明的一个方面,旨在提供一种存储装置,包括:一芯片,包括一金属层,其中所述金属层为一金属垫或一金属再分布层;以及多个导电线,垂直形成于所述金属层上,其中所述多个导电线的数量为至少三个,所述多个导电线的长度为5纳米至200纳米,且每一个所述导电线与相邻的一个所述导电线之间的距离为0.1纳米至20纳米。

5、在本发明的一实施例中,所述芯片临时地压在一电路板上,其中所述多个导电线中的至少一个所述导电线与所述电路板上的一金属表面接触并电连接。

6、在本发明的一实施例中,所述存储装置还包括一夹具及一弹性元件,所述夹具安装在所述电路板上,所述弹性元件设置于所述夹具及所述芯片之间,以提供一弹力将所述芯片推向所述电路板,使所述多个导电线与所述电路板电连接。

7、在本发明的一实施例中,所述多个导电线中的至少一个所述导电线与安装在所述金属表面的至少一导线接触并电连接。

8、根据本发明的一个方面,旨在提供一种半导体器件,包括至少两个如前所述的存储装置,其中所述至少两个存储装置中的一第一存储装置的所述芯片的所述金属层与所述至少两个存储装置中的一第二存储装置的所述芯片的所述金属层在一垂直方向上相对设置,且所述第一存储装置的所述多个导电线与所述第二存储装置的所述多个导电线在一交叉区域内沿一水平方向彼此平行排列并相互电连接。

9、在本发明的一实施例中,所述至少两个存储装置的所述多个导电线在所述水平方向上的一重叠面积至少为所述多个导电线的总长度的百分之五。

10、在本发明的一实施例中,所述至少两个存储装置至少包括一双倍数据速率-3存储装置、一双倍数据速率-4存储装置、一双倍数据速率-5存储装置、一低功耗双倍数据速率-3存储装置、一低功耗双倍数据速率-4存储装置、一低功耗双倍数据速率-5存储装置、一同步图形随机储存器-5存储装置或一同步图形随机储存器-6存储装置。

11、在本发明的一实施例中,所述第一存储装置的所述芯片的所述金属层为所述金属再分布层,所述第二存储装置的所述芯片的所述金属层为所述金属再分布层,且所述第一存储装置的所述芯片的所述金属再分布层与所述第二存储装置的所述芯片的所述金属再分布层在最高级别的金属布线彼此相异。

12、根据本发明的一个方面,旨在提供一种存储器系统,所述存储器系统由多个基板载体组成,每一个所述基板载体上安装有不同的至少两个芯片,且每一个所述基板载体包括垂直形成于所述基板载体的至少一导电线,其中所述至少两个芯片中的至少一个所述芯片是一存储芯片,至少一个所述芯片是一逻辑芯片,所述逻辑芯片实现存储器读写功能,至少一个所述存储芯片或所述逻辑芯片通过所述至少一导电线与所述基板载体相连接,且所述至少一导电线的长度为5纳米至200纳米。

13、在本发明的一实施例中,所述导电线的数量为至少三个,且每一个所述导电线与相邻的一个所述导电线之间的距离为0.1纳米至20纳米。

14、在本发明的一实施例中,每一个所述芯片包括一金属层及至少三个导电线,其中所述金属层为一金属垫或一金属再分布层,且所述至少三个导电线垂直形成于所述金属层上。

15、在本发明的一实施例中,所述基板载体的所述至少三个导电线以及所述芯片的所述至少三个导电线沿一水平方向彼此平行排列并相互电连接。

16、在本发明的一实施例中,所述基板载体的所述至少三个导电线以及所述芯片的所述至少三个导电线在所述水平方向上的一重叠面积至少为总长度的百分之五。

17、在本发明的一实施例中,至少一个所述存储芯片具有至少一故障单元,所述故障单元不能用于客户应用且不能再所述存储芯片上修复。

18、在本发明的一实施例中,所述至少一故障单元被所述逻辑芯片重新映射到同一个所述存储芯片或另一个所述存储芯片的一非故障单元上。

19、在本发明的一实施例中,所述至少一故障单元被所述逻辑芯片替换为所述逻辑芯片上的一非故障存储单元或一寄存器单元。

20、在本发明的一实施例中,所述至少一故障单元的一地址信息通过一闪存、一电气保险丝、一机械保险丝或一动态随机存取存储器存储在所述逻辑芯片上。

21、在本发明的一实施例中,所述地址信息从安装在同一个所述基板载体上的一个所述芯片下载到所述逻辑芯片。

22、根据本发明的所述多个方面,本发明提供的存储装置、半导体器件及存储器系统相较于现有技术至少具有以下有益效果:

23、一、由于上述导电线连接技术的电感和电容极低,因此存储装置将达到更高的速度;

24、二、与现有技术相比,由于导电线可在低温及低机械应力下生长,因此可减少存储器的降解,从而提高产量;

25、三、与铜柱或微凸块等技术相比,成本更低。

本文地址:https://www.jishuxx.com/zhuanli/20240808/272185.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 YYfuon@163.com 举报,一经查实,本站将立刻删除。

下一篇

返回列表