一种多通道同步采集的超声导波结构健康监测系统及方法与流程

- 国知局

- 2024-08-19 14:21:00

本发明属于超声导波检测系统领域,具体涉及一种多通道同步采集的超声导波结构健康监测系统及方法。

背景技术:

1、航空航天飞行器在服役的过程中容易受到撞、飞石等异物撞击而在复合材料内部形成各种几乎不可见的损伤,导致结构的承载性能发生退化,严重威胁航空航天装备的在役安全。

2、超声导波在板壳类结构中具有传播距离远、能量集中,对复合材料脱粘、分层、裂纹等损伤敏感。超声导波损伤监测技术是目前大面积范围内复合材料结构损伤监测最有效的技术手段,采用激励传感器将能量导入监测结构,与此同时接收传感器在结构上的其他位置接收响应信号,对信号进行分析来监测结构的健康状况。

3、现有技术中,如cn 108885194 b中公开的一种超声波检查系统、超声波检查方法及航空器结构体,使用第一超声波振子及第一超声波传感器取得结构体的第一检查区域的第一超声波检测信号;使用第二超声波振子及第二超声波传感器取得结构体的第二检查区域的第二超声波检测信号;以及基于所述第一超声波检测信号及所述第二超声波检测信号,求出表示所述第一检查区域及所述第二检查区域的至少一方的检查信息的指标值。但是现有技术中为一发一收的工作模式,数据采集效率较低,难以满足大型飞行器对结构健康监测实时性和监测效率的需求。

技术实现思路

1、本发明的目的是提出一种多通道同步采集的超声导波结构健康监测系统及方法,解决现有技术中不能保证任务被分配到最合适的开发人员的问题。

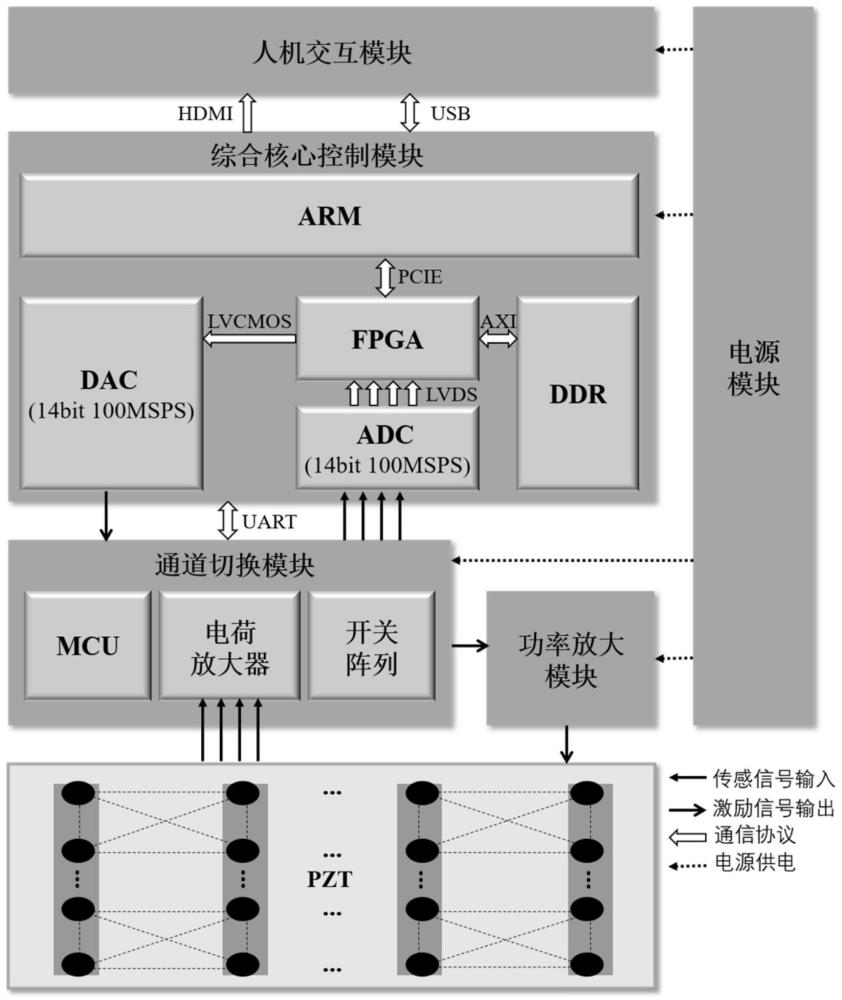

2、为此,本发明提供一种多通道同步采集的超声导波结构健康监测系统,包括,

3、人机交互模块,所述人机交互模块用于用户对系统进行控制;

4、综合核心控制模块,所述综合核心控制模块用于控制管理各个模块,实现信号激励与数据采集;

5、通道切换模块,所述通道切换模块用于切换不同的通道;

6、功率放大模块,所述功率放大模块用于将电信号放大;

7、电源模块,所述电源模块用于为系统提供电源;

8、压电传感器网络,所述压电传感器网络用于发出超声导波信号和接收超声导波信号;

9、所述人机交互模块与综合核心控制模块电性连接,所述综合核心控制模块与通道切换模块电性连接,所述通道切换模块与功率放大模块和压电传感器网络电性连接,所述功率放大模块与压电传感器网络电性连接,所述电源模块与人际交互模块、综合核心控制模块、通道切换模块和功率放大模块电性连接。

10、优选的,所述综合核心控制模块包括数据采集模块、数据缓存模块、信号发生模块、中心处理模块和核心电源模块,所述数据采集模块与数据缓存模块电性连接,所述数据缓存模块与信号发生模块电性连接,所述中心处理模块与数据采集模块、数据缓存模块、信号发生模块电性连接,所述核心电源模块与数据采集模块、数据缓存模块、信号发生模块电性连接。数据采集模块用于采集数据,数据缓存模块用于缓存数据,信号发生模块用于产生信号,中心处理模块用于对数据采集模块、数据缓存模块和信号发生模块的控制,核心电源模块用于对对数据采集模块、数据缓存模块和信号发生模块的供电。数据采集模块中通过adc单元对数据进行采集,数据缓存模块通过内存模块ddr对数据进行缓存以及时钟管理模块fpga对时钟进行管理,信号发生模块通过dac电路产生信号,中心处理模块通过嵌入式arm架构的cpu对数据采集模块、数据缓存模块和信号发生模块进行控制。

11、优选的,所述数据采集模块包括adc单元、模拟信号调理单元、数据串行化器、输入时钟调节单元,所述adc单元具有四个相互独立的输入通道,所述adc单元中的每个输入通道与一个模拟信号调理单元电性连接,所述模拟信号调理与与数据串行化器电性连接,所述输入时钟调节单元与数据串行化器电性连接。

12、优选的,所述数据缓存模块包括时钟管理模块fpga和内存模块ddr,所述时钟管理模块fpga与内存模块ddr电性连接,所述内存模块ddr内包括计算机内存条ddr3、ddr3控制单元、数据传输单元、数据缓存单元、数据拼接单元,所述数据拼接单元与数据采集模块和数据缓存单元连接,所述数据缓存单元与ddr3控制单元连接,所述数据传输单元与中心处理模块和ddr3控制单元连接,所述ddr3控制单元与计算机内存条ddr3连接,所述时钟管理模块fpga与数据缓存单元连接。

13、进一步优选的,所述计算机内存条ddr3有四个。

14、进一步优选的,所述数据缓存模块内还设置有晶体振荡器,所述晶体振荡器与时钟管理模块fpga连接。

15、优选的,所述数据缓存模块还包括缓冲器ibufds、idelay ip核、iserdese ip核、时钟相位控制单元、bitslip控制单元、bufio、bufr、数据并行化单元。

16、优选的,所述数据缓存模块还包括三个时钟域,分别为adc_clk、ui_clk、xdma_clk,adc_clk与ui_clk通过异步fifo ip核连接,i_clk与xdma_clk通过axi互联器连接。

17、进一步优选的,数据缓存模块还包括三个时钟域,分别为adc_clk、ui_clk、xdma_clk,adc_clk与ui_clk通过异步fifo ip核连接,ui_clk与xdma_clk通过第一axi互联器连接和第二axi互联器连接,adc_clk中包括数据拼接单元;

18、ui_clk中包括fifo逻辑模块、dma、mig ip核;

19、xdma_clk中包括地址计数器、axi数据位宽转换器、xdma ip核;

20、其中adc_clk为adc四通道数据的同步时钟;ui_clk为mig ip核提供的用户时钟,即ddr3读写同步时钟;xdma_clk为xdma ip核提供的用户时钟。

21、优选的,所述信号发生模块包括信号生成单元、波形存储器bram、dac电路单元、低通滤波器、运算放大器,所述信号生产单元与波形存储器bram连接,所述波形存储器bram与dac电路单元连接,所述dac电路单元与低通滤波器连接,所述低通滤波器与运算放大器连接。

22、进一步优选的,所述信号生成单元为dds信号发生器。

23、优选的,所述中央处理模块包括嵌入式arm架构的cpu。

24、优选的,所述通道切换模块包括mcu微处理器、电荷放大器和开关阵列,所述mcu微处理器与电荷放大器和开关阵列电性连接。

25、还提供了一种多通道同步采集的超声导波结构健康监测方法,包括以下步骤:

26、s1、用户通过人机交互模块控制系统,中心处理模块通过串口给矩阵切换开关发出命令,根据扫描路径同时选择压电传感网络中的一个传感器作为激励传感器,另外四个传感器为接收传感器;

27、s2、波形存储器bram与dac电路单元通过dds信号发生器产生激励信号,通过功率放大模块放大,再经矩阵切换开关以驱动指定的激励传感器,在结构上激励出超声导波;

28、s3、所选的四个接受传感器收到导波信号后感应出能力很小的电荷,进入电荷放大器转换成电压信号;

29、s4、通过adc单元对电压信号进行模数转换得到数字量;

30、s5、时钟管理模块fpga将采集到的数据在ddr中进行缓存,同时产生中断通知中心处理模块读取数据,并保存到数据库;

31、s6、中心处理模块进行信号处理和通过定位算法评估定位损伤。

32、有益效果:

33、1.本发明提供了一种多通道同步采集的超声导波结构健康监测系统及方法,采用一发多收的工作形式取代一发一收的工作形式,中心处理模块采用嵌入式结构,设计了高集成化、轻质化、低功耗的超声导波结构健康监测系统,可以满足机载需求,提高复合材料结构损伤的高效主动诊断。

34、2.现有技术中通常采用一发一收的工作模式,数据采集效率较低,难以满足大型飞行器对结构健康监测实时性和监测效率的需求。本发明中通过一个激励传感器对应四个接收传感器的方式,进行一发多收的工作形式,同时采集多个导波信号进行数据分析,提升数据采集效率。

35、3.对于一发多收工作形式的多通道采集系统,需要满足系统数据同步的要求,否则无法保证数据的准确性。在系统数据同步过程中,高速adc通常采用源同步技术输出ad数据,在发送数据的同时给出数据的同步时钟,有效稳定地传输高速ad数据。高速adc输出数据的速率高,往往因pcb布线带来的延迟或者时钟管理模块fpga内部逻辑的延迟造成时钟的相位偏移,如果同步时钟与四通道输出数据之间出现相移,造成时序错误,将会导致时钟管理模块fpga无法正确接收解析串行化数据。本发明通过缓冲器ibufds实现差分转单端信号,对于同一缓冲器,其对信号的延迟相当。iserdes可以对信号进行串并转换,通过增大数据位宽来降频以保证时钟管理模块fpga内部逻辑的稳定性,同时提供bitslip控制单元用于调整时钟信号解串的起始位置,配合fr来划分串行的输出数据,当采集到一个周期的fr序列时即表示成功接收一帧数据。当数据信号线数量较多时,在时钟管理模块fpga内对时钟进行延迟,使得时钟的采样边沿对齐数据眼的中心,可以减少idelay的使用,减小电路复杂度提高电路稳定性。

36、4.idelay由时钟相位控制单元和一个iserdes ip核来驱动,通过clk对单端源同步时钟dco_0进行采样,对idelay抽头步进累加,取第一次采集到全为高电平和最后一次采集到全为低电平的中间抽头值作为延迟时间,使clk定位到原来的dco_0边沿位置。同时,在设计时使adc的时钟与数据信号进入时钟管理模块fpga的同一个bank的io引脚,避免多个信号跨bank以减少延迟。

37、5.为了实现超声导波系统的快速扫查,系统需要及时且稳定地缓存adc产生的大量数据。本发明基于时钟管理模块fpga与ddr3构造一个高速大容量循环队列,即fifo逻辑模块用于缓存ad数据,以ddr3为存储介质结合fifo逻辑,把ddr3封装成一个大容量的跨时钟域fifo,实现系统快速、稳定的缓存adc产生的大量数据。

本文地址:https://www.jishuxx.com/zhuanli/20240819/274826.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 YYfuon@163.com 举报,一经查实,本站将立刻删除。

下一篇

返回列表