一种RISC-V指令加速运算方法、装置、电子设备及存储介质与流程

- 国知局

- 2024-08-22 14:42:07

本发明属于图像预处理,尤其涉及一种risc-v指令加速运算方法、装置、电子设备以及存储介质。

背景技术:

1、指令集架构(isa)作为软件与硬件交互的接口,扮演着连接两界的桥梁角色,对计算机系统的性能有着根本性的影响。它不仅定义了处理器执行操作的规则,还直接关系到算法效率和硬件资源的利用效率。特别是,通过定制特定应用指令集,能够针对如图像处理等专业领域优化运算流程,减少不必要的计算步骤,提升处理速度和效率。

2、risc-v,作为一种现代、开源的精简指令集架构,凭借其模块化和高度可扩展的设计,成为创新的理想平台。它不仅整合了以往isa的成功要素,还避开了历史遗留问题,提供基础指令集(如rv32i和rv64i服务于32位和64位环境)和多样化的扩展指令集(涵盖乘除、原子操作、浮点运算、压缩指令等),并且特意为自定义指令预留空间,极大增强了其适应不同应用场景的能力。

3、在图像预处理领域,gamma校正作为关键步骤,对于提升图像显示一致性至关重要。gamma校正通常用于调整图像的亮度和对比度,以改善图像的视觉质量和色彩表现。主要作用是校正显示设备的非线性响应,使图像在不同设备上呈现一致的视觉效果。在实现过程中,使用到幂函数运算。当前,在risc-v指令集架构中并没有支持幂函数的机器指令,编译器将使用标准的c语言库,需要多条机器代码来实现幂函数的运算,导致计算周期长。

4、因此为了加速gamma校正的函数运算或者满足其他使用场景对于运算的需求,有必要开发一种新的指令加速运算方法,能够根据使用场景对于运算的需求,实现函数的快速运算。

技术实现思路

1、本发明提供一种risc-v指令加速运算方法,通过自定义指令集的方法加速计算过程,能够有效的减少运算时间。

2、本发明还提供一种risc-v指令加速运算装置,能够完成指令加速运算的配置以及完成运算过程。

3、本发明的其他目的和优点可以从本发明所揭露的技术特征中得到进一步的了解。

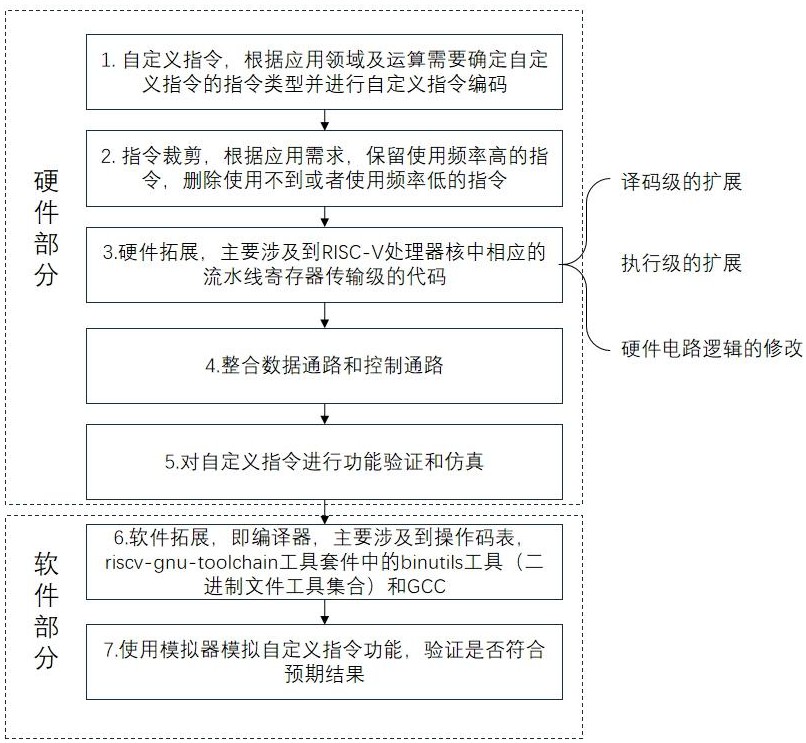

4、为达上述之一或部分或全部目的或其他目的,本发明一技术方案所提供的一种risc-v指令加速运算方法,risc-v指令加速运算方法包括:依据所需要完成的运算类型选择指令格式中指令类型作为自定义的指令类型,并根据所选的指令类型进行自定义指令编码;根据自定义指令编码,通过编译器生成自定义指令的汇编指令格式;根据自定义指令编码及所实现的功能,对risc-v处理器核的流水线寄存器传输级进行修改,同时建立自定义指令与risc-v处理器的数据通路;risc-v处理器核的译码级接收所述编译器生成的自定义指令,并生成相应的控制信号,所述控制信号用于控制所述risc-v处理器核的执行级对自定义指令进行计算并将结果输出至目的寄存器中,完成计算过程。该技术方案的有益效果在于,可以根据运算类型自定义指令集,通过risc-v处理器核执行自定义指令,可以完成复杂的函数运算,减少函数运算时间,进而缩短图像处理时间。

5、还包括指令裁剪,将自定义指令中未使用或者低使用率的指令集删除,并对risc-v所述执行级进行修改,将所述执行级中没有使用或者使用频率低的指令集处理单元删除。

6、还包括对自定义指令进行功能仿真和验证,通过工具链对自定义指令进行编译生成可执行的二进制文件,在测试平台架构内,将所述可执行的二进制文件载入至指令存储器单元以及生成仿真波形,完成功能仿真和验证。

7、所述risc-v指令加速运算方法还包括对所述自定义指令实现功能的验证,包括,使用内联汇编编写测试用例,运行模拟器并执行测试用例,监控模拟过程的状态变化,以评估自定义指令的执行效果是否符合预期设计目的。

8、在模拟器中添加自定义指令功能代码,所述功能代码用于记录,在模拟器中运行的自定义指令实现运算的过程行为。

9、对所述risc-v处理器核的流水线寄存器传输级进行修改,包括:当所述risc-v处理器核处理的指令为加载存储指令时,所述risc-v处理器核采用取值、译码、执行、访存以及写回的五级流水;当所述risc-v处理器核处理其他指令时,所述risc-v处理器核采用取值、译码、执行以及写回的四级流水。

10、根据自定义指令编码及实现的功能,对所述流水线寄存器传输级的译码级以及执行级进行修改;所述译码级的修改用于判断取出的指令是否为自定义指令;对所述执行级修改包括在所述执行级中定义一个自定义指令处理单元,所述自定义指令处理单元用于执行自定义指令相应的操作。

11、所述数据通路用于自定义指令所需的输入数据以及risc-v处理器核内的各个模块之间的数据传输。

12、所述自定义指令编码包括根据选择的指令类型以及实现运算所需的指令,对指令操作码以及功能字段进行编码。

13、所述编译器生成自定义指令的汇编指令格式前,对所述编译器进行配置修改,包括:根据自定义指令编码格式在编译器中更新操作码表;并在risc-v工具链中添加自定义指令的宏定义,同时对gun编译套件进行修改(这里主要涉及gnu编译套件的binutils工具(二进制文件工具集合)和gcc的修改),便于编译器识别自定义指令。

14、添加所述宏定义的方法为:在risc-v工具链的编译套件中的指令类别对应的操作数文件中添加自定义指令的宏定义,在所述操作数文件中添加的宏定义包括在头文件、操作数以及功能字段定义相应的宏文件。

15、在更新完操作码表以及添加自定义宏定义后,解析自定义指令得到编码值和掩码值,所述编码值记录自定义指令的寄存器和立即数以外的信息,所述掩码值记录自定义指令的指令类型。

16、本发明另一实施例提供一种risc-v指令加速运算装置,使用上述的一种risc-v指令加速运算方法进行指令加速运算,包括自定义指令模块,用于依据运算类型,选择risc-v指令集中的指令类型并进行自定义指令编码;指令裁剪模块,根据自定义指令操作的需求,将自定义指令中使用频率较低或者不使用的指令集删除,并删除risc-v处理器核执行级的相应指令集的处理单元;硬件拓展模块,对risc-v处理器核中相应的流水线寄存器传输级的代码进行修改,同时对risc-v处理器核的译码级以及执行级进行拓展,使得risc-v处理器核可正确识别自定义指令;软件拓展模块,所述软件拓展模块根据自定义指令编码,在编译器中更新操作码表,并添加自定义指令的宏定义,同时对gun编译套件进行修改(这里主要涉及gnu编译套件的binutils工具(二进制文件工具集合)和gcc的修改),使得编译器可以识别自定义指令;编译器,依据自定义指令编码,生成自定义指令的汇编指令格式;risc-v处理器核,自定义指令的汇编指令格式送入risc-v处理器核的译码级对自定义指令进行译码,生成控制信号送入执行级;所述risc-v处理器核的执行级将译码后生成的控制信号送入执行级的计算装置中,对自定义指令进行计算并输出结果。

17、所述risc-v指令加速运算装置还包括,指令验证单元,用于对自定义指令功能仿真和验证;指令模拟单元,根据自定义指令功能,在模拟器中添加功能代码,编写测试代码,运行模拟器,根据模拟器的运行结果验证自定义指令是否符合预期。

18、本发明另一实施例提供一种电子设备,包括:一个或多个处理器;存储器;一个或多个应用程序,其中所述一个或多个应用程序被存储在所述存储器中并被配置为由所述一个或多个处理器执行,所述一个或多个程序配置用于执行上述risc-v指令加速运算方法。

19、本发明另一实施例提供一种计算机可读存储介质,所述计算机可读存储介质中存储有程序代码,所述程序代码被处理器调用执行上述risc-v指令加速运算方法。

20、与现有技术相比,本发明的有益效果主要包括:本发明基于risc-v架构自定义用于复杂运算的自定义指令集,通过自定义指令集实现加速运算,减少函数计算时间。

21、为让本发明的上述和其他目的、特征和优点能更明显易懂,下文特举优选实施例,并配合附图,作详细说明如下。

本文地址:https://www.jishuxx.com/zhuanli/20240822/279547.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 YYfuon@163.com 举报,一经查实,本站将立刻删除。

下一篇

返回列表