一种叠栅介质氧化物异质结结构隧道场效应晶体管的制作方法

- 国知局

- 2024-08-30 14:27:26

本发明属于微电子,具体涉及一种叠栅介质氧化物异质结结构隧道场效应晶体管。

背景技术:

1、随着芯片集成度和应用需求的不断提高,静态功耗与器件性能之间的矛盾已成为一个严重的问题,其中,降低电子设备的功耗是未来节能应用的主要挑战之一。如果要解决功耗问题,就需要在提高开态电流的同时保持较小的关态电流,即较高的电流开关比与陡峭的亚阈值摆幅。齐纳在1934年首次提出粒子可以通过隧穿来克服经典约束的能量势垒的概念,隧穿场效应晶体管(tfet)是高性能低功耗集成电路领域的一个新成员,tfet受带间隧穿导通机制的影响,打破了其ss不能小于60mv/dec的束缚,可以大大降低器件的功耗。

2、tfet的主要缺点是开态电流低,一般比mosfet少两到三个数量级左右,这是tfet目前最大的问题。因此,双栅tfet被提出,如图1所示,图1是现有技术中的双栅tfet的一种结构示意图,设置有漏区1、源区2、沟道区3、左侧氧化层4-1和右侧氧化层4-2,双栅tfet对沟道表现出双倍强的栅控能力,能够提高器件的开态电流。然而,由于隧穿几率的提高,双栅tfet的双极电流也会增加,在实际应用中,器件在工作时会受双极性影响导致性能下降,栅功率工程、掺杂工程、栅介质工程和减少漏掺杂是降低tfet双极性电流最常用的技术,但这些技术均存在其自身的局限性。因此,亟需提供一种隧道场效应晶体管,既能提升器件开态电流,又能够降低双极电流和亚阈值摆幅。

技术实现思路

1、为了解决现有技术中存在的上述问题,本发明提供了一种叠栅介质氧化物异质结结构隧道场效应晶体管。本发明要解决的技术问题通过以下技术方案实现:

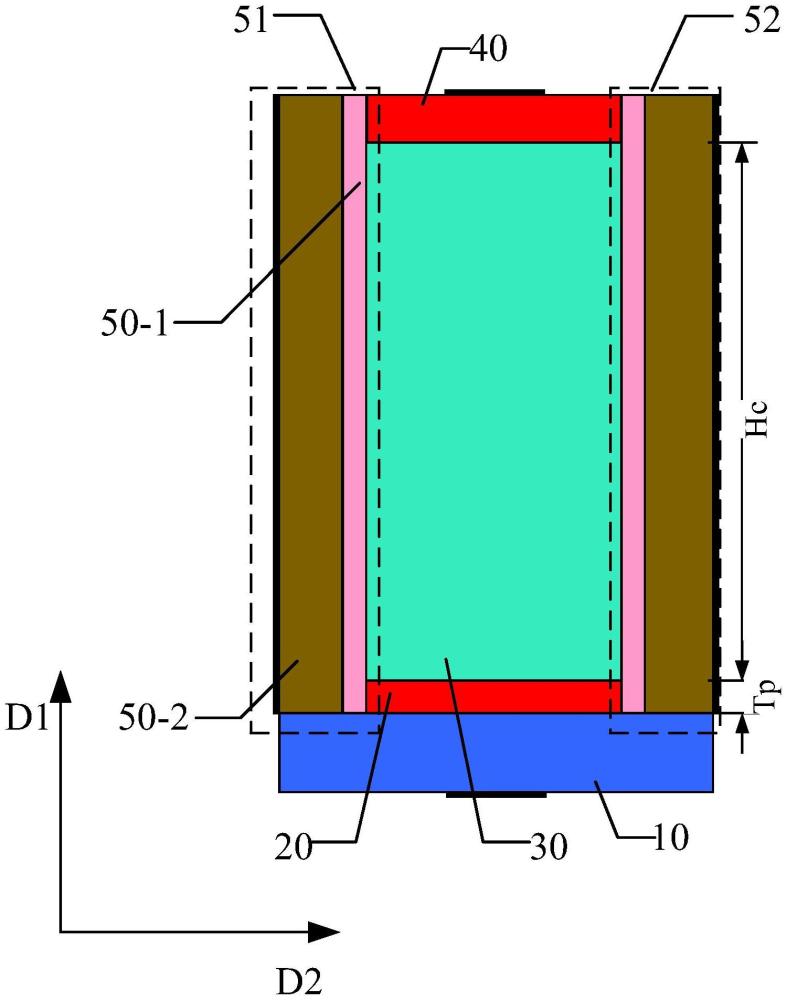

2、第一方面,本发明提供一种叠栅介质氧化物异质结结构隧道场效应晶体管,包括:沿第一方向依次层叠设置的源区、辅助势垒层、沟道区和漏区;

3、第一栅氧化层和第二栅氧化层,分别位于辅助势垒层、沟道区和漏区沿第二方向的两侧,且第一栅氧化层和第二栅氧化层沿第一方向的正投影位于源区沿第一方向的正投影的两侧;其中,

4、第一栅氧化层和第二栅氧化层均包括第一材料层和第二材料层,第一材料层位于第二材料层靠近辅助势垒层、沟道区和漏区的一侧,第一栅氧化层和第二栅氧化层均为高介电材料;

5、其中,第一方向与第二方向相交。

6、本发明的有益效果:

7、本发明提供的一种叠栅介质氧化物异质结结构隧道场效应晶体管,包括层叠设置的源区、辅助势垒层、沟道区和漏区,层叠设置的辅助势垒层、沟道区和漏区两侧分别设置第一栅氧化层和第二栅氧化层,且第一栅氧化层和第二栅氧化层沿第一方向的正投影位于源区沿第一方向的正投影的两侧,即第一栅氧化层和第二栅氧化层位于源区上方,位于源区上方两侧;其中,第一栅氧化层和第二栅氧化层均包括第一材料层和第二材料层,第一材料层紧邻辅助势垒层、沟道区和漏区,第二材料层位于第一材料层的外侧;如此,本发明采用双材料异质结构,第一材料层和第二材料层均为高介电材料。针对现有技术中使用单一高介电材料的隧道场效应晶体管,其在开态电流提高的同时,自身的双极电流也会被动提高,此外,较薄的高介电材料可能会导致栅极漏电,并且高介电材料与器件的半导体材料间存在大量的界面态,使得器件的可靠性受到了严重影响;本发明中,通过叠栅介质结构增加了栅氧化层厚度,从而降低漏区侧的栅氧电容,最终使得双极电流下降。同时,栅氧化层厚度的增加也防止了栅极漏电;此外,由于本发明选用的第一材料层与半导体材料的界面性相比于第二材料层更佳,器件的可靠性得到了提高。

8、以下将结合附图及实施例对本发明做进一步详细说明。

技术特征:1.一种叠栅介质氧化物异质结结构隧道场效应晶体管,其特征在于,包括:沿第一方向依次层叠设置的源区、辅助势垒层、沟道区和漏区;

2.根据权利要求1所述的叠栅介质氧化物异质结结构隧道场效应晶体管,其特征在于,所述源区和所述漏区的掺杂类型相反。

3.根据权利要求2所述的叠栅介质氧化物异质结结构隧道场效应晶体管,其特征在于,所述源区为p型重掺杂,所述漏区为n型重掺杂,或者;所述源区为n型重掺杂,所述漏区为p型重掺杂。

4.根据权利要求1所述的叠栅介质氧化物异质结结构隧道场效应晶体管,其特征在于,所述第一材料层包括al2o3,所述第二材料层包括hfo2。

5.根据权利要求1所述的叠栅介质氧化物异质结结构隧道场效应晶体管,其特征在于,沿第二方向,所述第一栅氧化层和所述第二栅氧化层的厚度相同,且所述第一栅氧化层包括的第一材料层的厚度为0.4~0.6nm,所述第一栅氧化层包括的第二材料层的厚度为1.5~2.5nm,所述第二栅氧化层包括的第一材料层的厚度为0.4~0.6nm,所述第二栅氧化层包括的第二材料层的厚度为1.5~2.5nm。

6.根据权利要求1所述的叠栅介质氧化物异质结结构隧道场效应晶体管,其特征在于,所述源区的材料包括si1-xgex材料,且所述源区的掺杂浓度为5×1019cm-3。

7.根据权利要求1所述的叠栅介质氧化物异质结结构隧道场效应晶体管,其特征在于,所述si1-xgex材料中x为0.9。

8.根据权利要求1所述的叠栅介质氧化物异质结结构隧道场效应晶体管,其特征在于,所述辅助势垒层的材料包括si材料,且所述辅助势垒层的掺杂浓度为5×1018cm-3,所述辅助势垒层的掺杂类型与所述源区的掺杂类型相反,所述辅助势垒层与所述源区之间形成si1-xgex/si隧穿异质结;

9.根据权利要求1所述的叠栅介质氧化物异质结结构隧道场效应晶体管,其特征在于,所述漏区的材料包括si。

10.根据权利要求1所述的叠栅介质氧化物异质结结构隧道场效应晶体管,其特征在于,所述沟道区的材料包括si。

技术总结本发明公开了一种叠栅介质氧化物异质结结构隧道场效应晶体管,涉及微电子技术领域,包括:沿第一方向依次层叠设置的源区、辅助势垒层、沟道区和漏区;第一栅氧化层和第二栅氧化层,分别位于辅助势垒层、沟道区和漏区沿第二方向的两侧,且第一栅氧化层和第二栅氧化层沿第一方向的正投影位于源区沿第一方向的正投影的两侧;其中,第一栅氧化层和第二栅氧化层包括第一材料层和第二材料层,第一材料层位于第二材料层靠近辅助势垒层、沟道区和漏区的一侧,第一栅氧化层和第二栅氧化层均为高介电材料。本发明能够抑制器件双极性行为并且提升器件的栅介质可靠性。技术研发人员:孙鹏,王敏受保护的技术使用者:世恩半导体科技(苏州)有限公司技术研发日:技术公布日:2024/8/27本文地址:https://www.jishuxx.com/zhuanli/20240830/282115.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 YYfuon@163.com 举报,一经查实,本站将立刻删除。

上一篇

一种数字电芯的制作方法

下一篇

返回列表