一种低导通电阻的SiCMOSFET器件及制备方法与流程

- 国知局

- 2024-08-30 14:57:43

本发明涉及半导体器件,特别涉及一种低导通电阻的sic mosfet器件及制备方法。

背景技术:

1、碳化硅(sic)材料作为第三代半导体具有优良的物理、电学性质,较大的禁带宽度、较高的击穿场强、良好的热导率,以sic材料为基础的电力电子器件能够在高温、高压、高频及高密度功率领域有很大的发展潜力。 随着sic mosfet在大功率设备中的广泛应用,市场对大功率应用设备的性能的要求逐步提高,如何进一步降低sic mosfet的导通电阻依然刻不容缓,迫在眉睫。

2、为此,需要一种能够有效降低总导通电阻,提升综合性能的低导通电阻的sicmosfet器件及制备方法。

技术实现思路

1、本发明的目的之一在于,提供了一种低导通电阻的sic mosfet器件,能够有效降低总导通电阻,提升综合性能。

2、为了解决上述技术问题,本申请提供如下技术方案:

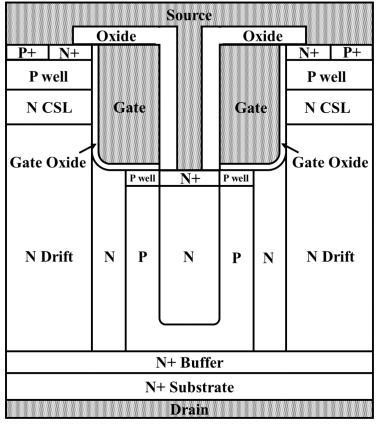

3、一种低导通电阻的sic mosfet器件,包括:

4、金属漏极;

5、位于金属漏极之上的n+型衬底;

6、位于n+型衬底之上的n+型缓冲层;

7、分别位于n+型缓冲层之上两侧的两个n型漂移区;

8、分别位于两个n型漂移区之上的n型载流子存储层;

9、分别位于两个n型载流子存储层之上的p阱;

10、分别位于两个p阱之上的p+型掺杂区以及n+型掺杂区;

11、位于两个n+型掺杂区、p阱、n型载流子存储层、n型漂移区之间的沟槽;

12、位于沟槽内的栅极;

13、位于栅极的外侧和底部栅极氧化层;

14、位于栅极下方的横向交替排列的n型掺杂区和p型掺杂区;

15、位于中间n型掺杂区顶部的又一n+型掺杂区;

16、位于p型掺杂区顶部的又一p阱;

17、位于沟槽内以及沟槽顶部的金属源极;

18、位于沟槽内以及沟槽顶部,将多晶硅栅极和金属源极隔离开的氧化层。

19、进一步,所述p阱之上的p+型掺杂区以及n+型掺杂区,p+型掺杂区位于n+型掺杂区的外侧。

20、进一步,所述横向交替排列的n型掺杂区和p型掺杂区,包括分别位于沟槽两侧和沟槽中间的三个n型掺杂区,以及位于n型掺杂区之间,呈u字形的一个p型掺杂区。

21、进一步,所述交替排列的n型掺杂区、p型掺杂区形成的n柱和p柱构成超结结构。

22、进一步,所述栅极为多晶硅栅极。

23、本发明的目的之二在于,提供一种低导通电阻的sic mosfet器件制备方法,包括如下步骤:

24、s1、选定一片n+型衬底;

25、s2、在n+型衬底上通过外延生长形成n+型缓冲层;

26、s3、在n+型缓冲层上继续外延生长形成n型漂移区;

27、s4、 在n型漂移区顶部进行刻蚀形成沟槽结构;

28、s5、 对沟槽下方的n型漂移区进行刻蚀到n+缓冲层表面,并进行n柱的外延生长到沟槽底部;

29、s6、对沟槽下方的n柱进行刻蚀到n+缓冲层表面,并进行p柱的外延生长到沟槽底部;

30、s7、对沟槽下方的p柱进行刻蚀,并进行n柱的外延生长到沟槽底部;

31、s8、在n型漂移区表面进行n离子注入形成n型载流子存储层;

32、s9、在n型漂移区表面和沟槽底部p柱表面进行al离子注入形成p阱;

33、s10、在n型载流子存储层之上的p阱表面进行al离子注入形成p+型掺杂区;

34、s11、 在n型载流子存储层之上的p阱表面,和沟槽底部中间的n柱表面进行n离子注入形成n+型掺杂区;

35、s12、在沟槽内热氧化生长sio2形成栅极氧化层;

36、s13、在沟槽内栅极氧化层上面淀积多晶硅;

37、s14、对多晶硅进行刻蚀到n+型掺杂区表面,并淀积sio2形成芯片表面到沟槽底部的氧化层;

38、s15、在芯片顶部和底部淀积al金属形成栅极、源极和漏极。

39、进一步,所述n+型衬底为sic n+型衬底。

40、进一步,所述s4中,在n型漂移区顶部进行干法刻蚀形成沟槽结构;

41、s5中,对沟槽下方的n型漂移区进行干法刻蚀到n+缓冲层表面;

42、s6中,对沟槽下方的n柱进行干法刻蚀到n+缓冲层表面;

43、s7中,对沟槽下方的p柱进行干法刻蚀;

44、s14中,对多晶硅进行干法刻蚀到n+型掺杂区表面。

45、本方案的sic mosfet具备两个导电沟道,分别位于沟槽侧壁和沟槽底部的p型掺杂区表面。此外,本发明在沟槽下方集成了超结结构,由交替排列的n型和p型掺杂区构成的n柱和p柱组成。超结结构的p柱表面也形成了第二导电沟道。

46、在sic mosfet的基础上,本方案在沟槽底部增加了第二个导电沟道,进一步提高了沟道密度,从而降低了导通电阻。同时,集成的超结结构通过提高漂移区的掺杂浓度,显著降低了漂移区的导通电阻。通过双导电沟道和超结结构的结合,本发明大幅降低了sicmosfet的总导通电阻,提升了其综合性能。

47、综上,本方案能够提升sic mosfet的沟道密度,降低sic mosfet的导通电阻,提升sic mosfet的综合性能。

技术特征:1. 一种低导通电阻的sic mosfet器件,其特征在于,包括:

2. 根据权利要求1所述的低导通电阻的sic mosfet器件,其特征在于:所述p阱之上的p+型掺杂区以及n+型掺杂区,p+型掺杂区位于n+型掺杂区的外侧。

3. 根据权利要求2所述的低导通电阻的sic mosfet器件,其特征在于:所述横向交替排列的n型掺杂区和p型掺杂区,包括分别位于沟槽两侧和沟槽中间的三个n型掺杂区,以及位于n型掺杂区之间,呈u字形的一个p型掺杂区。

4. 根据权利要求3所述的低导通电阻的sic mosfet器件,其特征在于:所述交替排列的n型掺杂区、p型掺杂区形成的n柱和p柱构成超结结构。

5. 根据权利要求4所述的低导通电阻的sic mosfet器件,其特征在于:所述栅极为多晶硅栅极。

6. 一种低导通电阻的sic mosfet器件制备方法,其特征在于,包括如下步骤:

7. 根据权利要求6所述的低导通电阻的sic mosfet器件制备方法,其特征在于:所述n+型衬底为sic n+型衬底。

8. 根据权利要求7所述的低导通电阻的sic mosfet器件制备方法,其特征在于:所述s4中,在n型漂移区顶部进行干法刻蚀形成沟槽结构;

技术总结本发明涉及半导体器件技术领域,具体公开了一种SiC MOSFET器件及制备方法,其中器件,包括:金属漏极,N+型衬底;N+型缓冲层,两个N型漂移区,两个N型载流子存储层,两个P阱;分别位于两个P阱之上的P+型掺杂区以及N+型掺杂区;位于两个N+型掺杂区、P阱、N型载流子存储层、N型漂移区之间的沟槽;位于沟槽内的栅极;位于栅极的外侧和底部栅极氧化层;位于栅极下方的横向交替排列的N型掺杂区和P型掺杂区;位于中间N型掺杂区顶部的又一N+型掺杂区;位于P型掺杂区顶部的又一P阱;位于沟槽内以及沟槽顶部的金属源极;位于沟槽内以及沟槽顶部,将多晶硅栅极和金属源极隔离开的氧化层。采用本发明的技术方案能够有效降低总导通电阻,提升综合性能。技术研发人员:任真伟,王晓受保护的技术使用者:深圳平创半导体有限公司技术研发日:技术公布日:2024/8/27本文地址:https://www.jishuxx.com/zhuanli/20240830/284809.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 YYfuon@163.com 举报,一经查实,本站将立刻删除。

下一篇

返回列表