一种碳化硅功率器件及其制备方法与流程

- 国知局

- 2024-08-30 14:57:36

本发明涉及半导体,特别涉及一种碳化硅功率器件及其制备方法。

背景技术:

1、sic mosfet(metal oxide semiconductor field effect transistor,金属氧化物半导体场效应晶体管)功率器件以耐高压高温、高频率、低功率损耗以及高开关速度等优势被广泛的应用于新能源汽车、交通轨道以及光伏等产业。sic mosfet功率器件根据其栅极结构可分为平面型 (dmosfet)与沟槽型 (trench mosfet)。

2、以n型平面mosfet功率器件为例,在相关技术中,其体区(p阱)通常采用p型离子(例如al离子)注入而形成。由于碳化硅材材料的特性(al离子在碳化硅材材料的扩散较弱),在离子注入时只能通过高能离子注入,而且为了确保其离子注入深度分布,还需进行多次al离子注入以形成所需的p阱,并进而在p阱中形成沟道区。但上述多次高能离子注入,使得所形成p阱的表面较为粗糙,增加了沟道散射,严重影响沟道的载流子迁移率的提升。特别的,上述部分p阱位于栅极结构下方,即作为栅氧沟道区,栅氧沟道区的表面粗糙将严重影响器件的性能及可靠性(栅氧的可靠性)。

技术实现思路

1、本发明的目的在于提供一种碳化硅功率器件及其制备方法,用于通过降低体区表面的粗糙度以提高碳化硅功率器件的性能及可靠性。

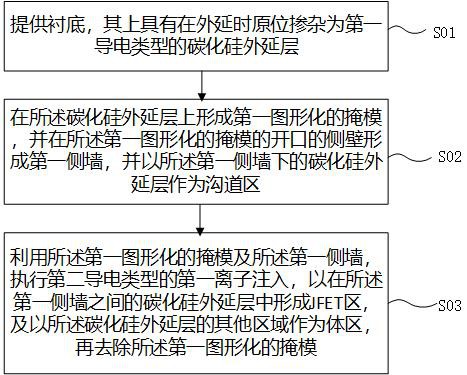

2、为解决上述技术问题,本发明提供的碳化硅功率器件的制备方法,包括:

3、提供衬底,其上具有在外延时原位掺杂为第一导电类型的碳化硅外延层;

4、在所述碳化硅外延层上形成第一图形化的掩模,并在所述第一图形化的掩模的开口的侧壁形成第一侧墙,并以所述第一侧墙下的碳化硅外延层作为沟道区;

5、利用所述第一图形化的掩模及所述第一侧墙,执行第二导电类型的第一离子注入,以在所述第一侧墙之间的碳化硅外延层中形成jfet区,及以所述碳化硅外延层的其他区域作为体区,再去除所述第一图形化的掩模。

6、可选的,所述碳化硅功率器件包括nmos器件,所述第一导电类型为p型,所述第二导电类型为n型。

7、可选的,在所述碳化硅外延层与所述第一图形化的掩模之间还设有离子注入保护层,所述第一图形化的掩模的开口暴露对应离子注入保护层的表面。

8、可选的,在去除所述第一图形化的掩模后,还在所述第一侧墙之间形成第二侧墙,所述第二侧墙覆盖所述jfet区,且暴露所述第一侧墙之外的碳化硅外延层;

9、利用所述第一侧墙及所述第二侧墙执行所述第二导电类型的第二离子注入,以在所述碳化硅外延层中形成源区,所述源区的注入深度小于所述碳化硅外延层的厚度。

10、可选的,去除所述第一侧墙及所述第二侧墙;

11、形成第二图形化的掩模,所述第二图形化的掩模的开口暴露所述源区远离所述jfet区的区域;

12、利用所述第二图形化的掩模,执行所述第一导电类型的第三离子注入,以在所述源区中形成体二级管区;

13、在所述碳化硅外延层的外围区域形成终端结构。

14、可选的,

15、在形成第一图形化的掩模之前,形成第三图形化的掩模暴露所述碳化硅外延层的部分表面;

16、执行所述第二导电类型的第二离子注入,以在所述碳化硅外延层中形成源区;

17、去除所述第三图形化的掩模,依次形成所述第一图形化的掩模、所述第一侧墙及所述jfet区。

18、可选的,还包括在所述jfet区、所述沟道区及部分所述源区的表面上形成栅极结构。

19、可选的,所述第一图形化的掩模的开口除暴露用于形成jfet区的区域之外,还暴露用于形成终端结构的区域,并在执行所述第二导电类型的第一离子注入时,在所述碳化硅外延层中同步形成所述jfet区及终端结构。

20、基于本发明的另一方面,还提供一种碳化硅功率器件,包括衬底;

21、设于所述衬底表面的碳化硅外延层,具有第一导电类型且其由外延时原位掺杂而形成;

22、设于所述碳化硅外延层中的体区、jfet区及沟道区,所述jfet区具有第二导电类型,所述沟道区设于所述体区中并与所述jfet区连接,所述体区及所述沟道区由部分所述碳化硅外延层构成。

23、可选的,所述碳化硅功率器件包括nmos器件,所述第一导电类型为p型,所述第二导电类型为n型,且所述沟道区的表面粗糙度小于或等于10纳米。

24、综上所述,本发明提供的碳化硅功率器件的制备方法包括提供衬底,其上具有在外延时原位掺杂为第一导电类型的碳化硅外延层;在所述碳化硅外延层上形成第一图形化的掩模,并在所述第一图形化的掩模的开口的侧壁形成第一侧墙,并以所述第一侧墙下的碳化硅外延层作为沟道区;利用所述第一图形化的掩模及所述第一侧墙,执行第二导电类型的第一离子注入,以在所述第一侧墙之间的碳化硅外延层中形成jfet区,及以所述碳化硅外延层的其他区域作为体区,再去除所述第一图形化的掩模。相对于采用外延后再离子注入形成的碳化硅层,本发明采用在外延时原位掺杂形成的碳化硅外延层,使其具有较低的表面粗糙度,在采用第一图形化的掩模侧壁的第一侧墙在上述碳化硅外延层自对准定义出沟道区,使沟道区具有较佳的尺寸(长度、宽度及厚度)及掺杂浓度上的均匀性。因此,沟道区作为碳化硅外延层的一部分(由一部分碳化硅外延层直接构成)也具有上述各种优势,较低表面粗糙度的沟道区可提高位于沟道区上的栅极介质层的可靠性以提高功率器件的性能及可靠性,具有较佳尺寸及掺杂浓度均匀性的沟道区可减小不同功率器件之间的性能差异。此外,本发明中较低的表面粗糙度碳化硅外延层,还有利于曝光设备识别设于碳化硅外延层的光刻标记,以提高对位精度并降低曝光设备因对位异常导致报警的风险。

技术特征:1.一种碳化硅功率器件的制备方法,其特征在于,包括:

2.根据权利要求1所述的碳化硅功率器件的制备方法,其特征在于,所述碳化硅功率器件包括nmos器件,所述第一导电类型为p型,所述第二导电类型为n型。

3.根据权利要求1所述的碳化硅功率器件的制备方法,其特征在于,在所述碳化硅外延层与所述第一图形化的掩模之间还设有离子注入保护层,所述第一图形化的掩模的开口暴露对应离子注入保护层的表面。

4.根据权利要求1所述的碳化硅功率器件的制备方法,其特征在于,在去除所述第一图形化的掩模后,还在所述第一侧墙之间形成第二侧墙,所述第二侧墙覆盖所述jfet区,且暴露所述第一侧墙之外的碳化硅外延层;

5.根据权利要求4所述的碳化硅功率器件的制备方法,其特征在于,

6.根据权利要求1所述的碳化硅功率器件的制备方法,其特征在于,

7.根据权利要求4至6中任一项所述的碳化硅功率器件的制备方法,其特征在于,还包括在所述jfet区、所述沟道区及部分所述源区的表面上形成栅极结构。

8.根据权利要求4或6所述的碳化硅功率器件的制备方法,其特征在于,

9.一种碳化硅功率器件,其特征在于,包括衬底;

10.根据权利要求9所述的碳化硅功率器件,其特征在于,所述碳化硅功率器件包括nmos器件,所述第一导电类型为p型,所述第二导电类型为n型,且所述沟道区的表面粗糙度小于或等于10纳米。

技术总结本发明提供了一种碳化硅功率器件及其制备方法,碳化硅功率器件的制备方法包括:提供衬底,其上具有在外延时原位掺杂为第一导电类型的碳化硅外延层;在所述碳化硅外延层上形成第一图形化的掩模,并在所述第一图形化的掩模的开口的侧壁形成第一侧墙,并以所述第一侧墙下的碳化硅外延层作为沟道区;利用所述第一图形化的掩模及所述第一侧墙,执行第二导电类型的第一离子注入,以在所述第一侧墙之间的碳化硅外延层中形成JFET区,及以所述碳化硅外延层的其他区域作为体区,再去除所述第一图形化的掩模。本发明中,用于通过外延原位掺杂形成体区以降低沟道表面的粗糙度以提高碳化硅功率器件的性能及可靠性。技术研发人员:李翔受保护的技术使用者:芯联越州集成电路制造(绍兴)有限公司技术研发日:技术公布日:2024/8/27本文地址:https://www.jishuxx.com/zhuanli/20240830/284796.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 YYfuon@163.com 举报,一经查实,本站将立刻删除。