放大器电路及芯片的制作方法

- 国知局

- 2024-09-05 14:22:38

本公开涉及集成电路领域,特别是涉及一种放大器电路及芯片。

背景技术:

1、在集成电路领域中,采用放大器可以将微弱信号转换为电信号或者其他所需形式的信息输出,再经过数据处理,即可得到所需的信息。考虑到微弱信号幅度小,因此必须保证被放大的信号有良好的线性度,这对放大器电路的增益提出了要求。随着物联网的兴起,对放大器电路的功耗有了更高的要求。当负载工作时,经过放大器传输的电信号不能变化太大,否则这将减少电信号包含的有效信息,这对放大器电路的驱动能力有了更高的要求。

2、因此,如何获得高增益、低功耗且强驱动能力的放大器电路是亟需解决的问题。

技术实现思路

1、基于此,有必要提供一种放大器电路及芯片,以有效提高放大器电路的增益、降低放大器电路的功耗,以及增强放大器电路的驱动能力。

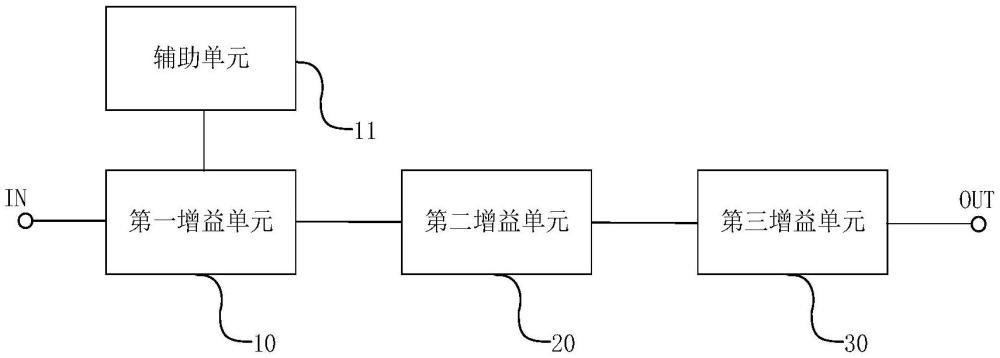

2、本公开实施例提供了一种放大器电路,包括第一增益单元、辅助单元、第二增益单元和第三增益单元。第一增益单元与信号输入端连接,被配置为:接收输入信号,对输入信号进行第一级增益处理,输出第一增益信号。辅助单元与第一增益单元连接,被配置为:辅助第一增益单元对输入信号进行第一级增益处理。第二增益单元与第一增益单元连接,被配置为:对第一增益信号进行第二级增益处理,输出第二增益信号。第三增益单元与信号输出端和第二增益单元均相连接,被配置为:对第二增益信号进行第三级增益处理,输出第三增益信号;第三增益信号用于驱动外部负载。

3、本公开实施例中,第一增益单元、第二增益单元和第三增益单元组成三级放大器电路。其中,通过辅助单元确保第一增益单元正常工作。也即,第一增益单元在辅助单元的辅助下,采用增益提升技术提高放大器电路的开环增益,从而对输入信号进行第一级增益处理,输出第一增益信号。第二增益单元对第一增益信号进行第二级增益处理,输出第二增益信号。第三增益单元对第二增益信号进行第三级增益处理,输出第三增益信号。如此,本公开可以有效提高放大器电路的增益,实现高增益的放大器电路。

4、在本公开一些实施例中,放大器电路还包括:跨导线性环单元。跨导线性环单元与第二增益单元和第三增益单元连接,被配置为:降低第三增益单元的功耗。

5、在本公开一些实施例中,第一增益单元包括共源共栅放大器和运算放大器。共源共栅放大器包括:第一晶体管,第二一晶体管、第二二晶体管、第三一晶体管、第三二晶体管、第四一晶体管、第四二晶体管、第五一晶体管、第五二晶体管、第六一晶体管和第六二晶体管。运算放大器包括:第一正运算放大器、第二正运算放大器、第一负运算放大器和第二负运算放大器。第一晶体管的栅极与第一偏置电压连接。第一偏置电压为pmos管的偏置电压。第一晶体管的源极与第六一晶体管的源极、第六二晶体管的源极和正电源均相连接。第一晶体管的漏极与第二一晶体管的衬底、第二一晶体管的源极、第二二晶体管的衬底、第二二晶体管的源极、第二输入信号和第一输入信号均相连接。第二一晶体管的漏极与第三一晶体管的漏极、第四一晶体管的源极和第一正运算放大器的负输入端均相连接。第二二晶体管的漏极与第三二晶体管的漏极、第四二晶体管的源极和第二正运算放大器的负输入端均相连接。第三一晶体管的栅极与第三二晶体管的栅极、第四一晶体管的漏极和第五一晶体管的漏极均相连接。第三一晶体管的源极与第三二晶体管的源极和负电源均相连接。第四一晶体管的栅极与第一正运算放大器的输出端连接;第四二晶体管的栅极与第二正运算放大器的输出端连接;第四二晶体管的漏极为第一增益单元的第一输出端,与第二增益单元连接。第五一晶体管的栅极与第一负运算放大器的输出端连接。第五一晶体管的源极与第六一晶体管的漏极连接。第五二晶体管的栅极与第二负运算放大器的输出端连接。第五二晶体管的源极与第六二晶体管的漏极连接,共同作为第一增益单元的第一输入端,与辅助单元连接。第五二晶体管的漏极为第一增益单元的第二输出端,与第二增益单元连接。第六一晶体管的栅极与第六二晶体管的栅极和第一偏置电压均相连接。第一正运算放大器的正输入端与第二正运算放大器的正输入端连接,共同作为第一增益单元的第二输入端,与辅助单元均相连接。第一负运算放大器的正输入端与第二负运算放大器的正输入端连接,共同作为第一增益单元的第三输入端,与辅助单元均相连接。第二负运算放大器的负输入端为第一增益单元的第四输入端,与辅助单元连接。

6、在本公开一些实施例中,第一增益单元包括:第一增益模块、第二增益模块、第三增益模块和第四增益模块。第一增益模块包括:第一正运算放大器和第四一晶体管。第二增益模块包括:第二正运算放大器和第四二晶体管。第三增益模块包括:第一负运算放大器和第五一晶体管。第四增益模块包括:第二负运算放大器和第五二晶体管。

7、在本公开一些实施例中,第一增益单元还包括:第九晶体管和第十晶体管。

8、第九晶体管的栅极作为第一增益单元的第五输入端;第九晶体管的源极、第十晶体管的漏极和第四二晶体管的漏极均相连接,共同作为第一增益单元的第一输出端,与第二增益单元均相连接;第九晶体管的漏极与第十晶体管的源极和第五二晶体管的漏极均相连接,共同作为第一增益单元的第二输出端。第十晶体管的栅极作为第一增益单元的第六输入端。

9、在本公开一些实施例中,辅助单元包括:第七晶体管、第八晶体管、第十一晶体管、第十二晶体管。第七晶体管、第八晶体管、第十一晶体管和第十二晶体管用于辅助第一增益模块、第二增益模块、第三增益模块和第四增益模块。

10、第七晶体管的栅极与第五一晶体管的源极和第六一晶体管的漏极均相连接;第七晶体管的源极与第一负运算放大器的负输入端和第八晶体管的漏极均相连接;第七晶体管的漏极与正电源连接。第八晶体管的栅极与第二偏置电压连接;第八晶体管的源极与负电源连接;第二偏置电压为nmos管的偏置电压。第十一晶体管的栅极与第五二晶体管的漏极和第六二晶体管的漏极均相连接;第十一晶体管的源极与第二负运算放大器的负输入端和第十二晶体管的漏极均相连接;第十一晶体管的漏极与正电源连接。第十二晶体管的栅极与第二偏置电压连接;第十二晶体管的源极与负电源连接;第十二晶体管的漏极与第一增益单元的第四输入端连接。

11、在本公开一些实施例中,跨导线性环单元包括第一跨导线性环和第二跨导线性环。第一跨导线性环包括:第九晶体管、第二十二晶体管、第二十三晶体管、第二十四晶体管、第三十一晶体管、第三十四晶体管。第二跨导线性环包括:第十晶体管、第二十五晶体管、第二十六晶体管、第二十七晶体管、第三十晶体管和第三十三晶体管。第九晶体管的栅极与第二十二晶体管的栅极和第二十二晶体管的漏极均相连接。第九晶体管的源极与第十晶体管的漏极、第一增益单元的第一输出端、第三十一晶体管的栅极和第三十四晶体管的栅极均连接;第九晶体管的漏极与第十晶体管的源极、第一增益单元的第二输出端、第三十晶体管的栅极和第三十三晶体管的栅极均连接。第十晶体管的栅极与第二十七晶体管的栅极和第二十七晶体管的漏极均相连接。第二十二晶体管的源极与第二十三晶体管的栅极和第二十三晶体管的漏极均相连接。第二十三晶体管的源极与第二十四晶体管的栅极和第二十四晶体管的漏极均相连接;第二十四晶体管的源极与负电源连接。第二十五晶体管的源极与正电源连接。第二十六晶体管的源极与第二十五晶体管的栅极和第二十五晶体管的漏极均相连接。第二十七晶体管的源极与第二十六晶体管的栅极和第二十六晶体管的漏极均相连接。第三十晶体管的源极与第三十三晶体管的栅极相连接。第三十晶体管的漏极与第三十四晶体管的源极和负电源均相连接。第三十一晶体管的源极与第三十四晶体管的栅极相连接。第三十一晶体管的漏极与第三十三晶体管的源极和正电源均相连接。第三十三晶体管的漏极与第三十四晶体管的漏极连接。其中,第三十三晶体管和第三十四晶体管构成第三增益单元。

12、本公开实施例中,跨导线性环单元分别与第二增益单元和第三增益单元均相连接,通过跨导线性环单元来控制第三增益单元的静态功耗。其中,第十晶体管、第三十晶体管、第三十三晶体管分别镜像第二十七晶体管、第二十六晶体管、第二十五晶体管的电流,第九晶体管、第三十一晶体管、第三十四晶体管分别镜像第二十二晶体管、第二十三晶体管、第二十四晶体管的电流。第三十三晶体管和第三十四晶体管的静态功耗与第二十七晶体管、第二十四晶体管的宽长比有关,从而解决了第三增益单元静态功耗高的缺陷,同时保留了第三增益单元的强驱动能力。

13、在本公开一些实施例中,第二增益单元包括:第一源极跟随器、第二源极跟随器、第一密勒电容、第二密勒电容和消零电阻。第一源极跟随器包括:第二十九晶体管和第三十晶体管。第二源极跟随器包括:第三十一晶体管和第三十二晶体管。第二十九晶体管的栅极连接第一偏置电压。第二十九晶体管的源极连接正电源。第二十九晶体管的漏极与第三增益单元的第一输入端、第三十晶体管的源极、第三十晶体管的栅极、第一密勒电容的第一端和第一增益单元的第二输出端均相连接。第三十二晶体管的栅极连接第二偏置电压。第三十二晶体管的源极连接负电源。第三十二晶体管的漏极与第三增益单元的第二输入端、第三十一晶体管的源极、第三十一晶体管的栅极、第二密勒电容的第一端和第一增益单元的第一输出端均相连接。第一密勒电容的第二端与第二密勒电容的第二端和消零电阻的第一端均相连接。消零电阻的第二端与第三增益单元的第三输入端相连接。

14、本公开实施例中,第二增益单元的输出阻抗小,通过将第一密勒电容、第二密勒电容以及消零电阻将主极点往原点推,次极点往高频推,同时抵消零点,从而实现放大器电路的稳定。

15、在本公开一些实施例中,第一晶体管,第二一晶体管、第二二晶体管、第五一晶体管、第五二晶体管、第六一晶体管、第六二晶体管、第十晶体管、第二十五晶体管、第二十六晶体管、第二十七晶体管、第二十九晶体管、第三十晶体管、第三十三晶体管、第十八晶体管和第二十一晶体管均为pmos晶体管;第三一晶体管、第三二晶体管、第四一晶体管、第四二晶体管、第七晶体管、第八晶体管、第九晶体管、第二十二晶体管、第二十三晶体管、第二十四晶体管、第三十一晶体管、第三十二晶体管、第三十四晶体管、第十二晶体管、第十五晶体管和第十七晶体管均为nmos晶体管。

16、本公开实施例还提供了一种芯片,芯片包括如前述实施例中所述的放大器电路。

17、本公开实施例中,芯片采用如上结构,该芯片所能实现的技术效果与前述实施例中放大器电路所能具有的技术效果相同,此处不再详述。

本文地址:https://www.jishuxx.com/zhuanli/20240905/286106.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 YYfuon@163.com 举报,一经查实,本站将立刻删除。

下一篇

返回列表