适用于功率放大器芯片的控制电路、功率放大器芯片的制作方法

- 国知局

- 2024-08-30 15:08:21

本技术涉及功率放大器,具体地,涉及一种适用于功率放大器芯片的控制电路、功率放大器芯片。

背景技术:

1、射频功率放大器(功放,power amplifier,pa)在现代无线通信系统中发挥着重要的作用。它的主要作用是对通讯信号进行放大并传输,从而提高信号传输的功率和距离。手机、基站、卫星通信、电视广播等系统都使用功率放大器来扩展信号传输范围和覆盖范围,以保证信号的稳定性和可靠性。

2、在手机领域,由于功放的发射功率小,更容易集成,目前消费类的功放模块已集成开关、滤波器,电源控制等模块。但在基站功放领域,应用场景不同,要求功放功率大,效率高等,功放集成化一直是一个难点和痛点。近些年来,随着制造工艺和封装技术的发展,针对基站峰值功率为10~200w的功放应用中(如 mimo 和 small-cell 应用),集成功率放大器设计成为一种趋势和主流。

3、由于基站功放对效率的指标要求很高,目前业内主要采用doherty pa 架构,通过负载牵引方式来提高工作点的效率;其中,pa(power amplifier,功率放大器)。doherty pa通常由一个主路pa和一个辅路pa 构成。主路pa工作在class ab 或class b 的线性状态,辅路pa 工作在class c 工作状态。基站doherty pa 从实现方式上可以分为两种,一种是分立器件方案,一种是集成方案。

4、分立pa方案的架构框图如图1,主路和辅路放大晶体管被集成在一个封装内,功分器(即功率分配器)、移相器,输入匹配电路,功率合成器和输出匹配电路都在放大晶体管外面实现,通常是由 pcb走线和一些贴片电容电感电阻组成。这种方案的集成度低,整个模块占用的面积大。

5、集成pa方案的架构框图如图2,区别于分立pa方案。集成pa架构将功分器(即功率分配器)、移相器,输入匹配电路,功率合成器和输出匹配电路的全部或部分模块和放大晶体管集成到一个封装内,可以单芯片或多芯片实现,也可集成无源表贴器件增加集成度。

6、如图2所示,是一个典型的两路doherty集成pa架构,其中vbiasm为主路放大管偏置引脚,为主路放大管提供偏置通路。vbiasp为辅路放大管偏置引脚,为辅路放大管提供偏置通路。vdd为主路和辅路放大管的漏级偏置电压源。在实际应用中,vbiasm 和vbiasp 由片外的pa控制电路(也称pa开关电路)提供。

7、如图3所示,pa控制电路主要由开关电路组成。paen 是pa控制电路总的使能信号,一般paen的输入信号为高低电平的方波信号。通过paen信号控制pa的开启或关闭。当paen为高电平时,开关闭合导通,vcm被传输到vbiasm,vcp被传输到vbiasp,vbiasm和vbiasp给pa提供偏置,此时pa正常工作。反之,当paen为低电平时,开关断开,vcm无法传递到vbiasm,vcp也无法传递到vbiasp,vbiasm和vbiasp被开关电路下拉到低电平,此时pa无法工作。目前pa控制电路外置是主流方案,相对来说集成度低,成本较高。

8、随着技术的发展,近年来也出现了集成pa控制电路到pa模块的架构设计。如图4所示,区别于图2架构,图4架构就是将片外的pa开关模块集成到整个pa模块里面。这种集成架构应用中,就省去了片外的开关模块,集成度高,节约成本。

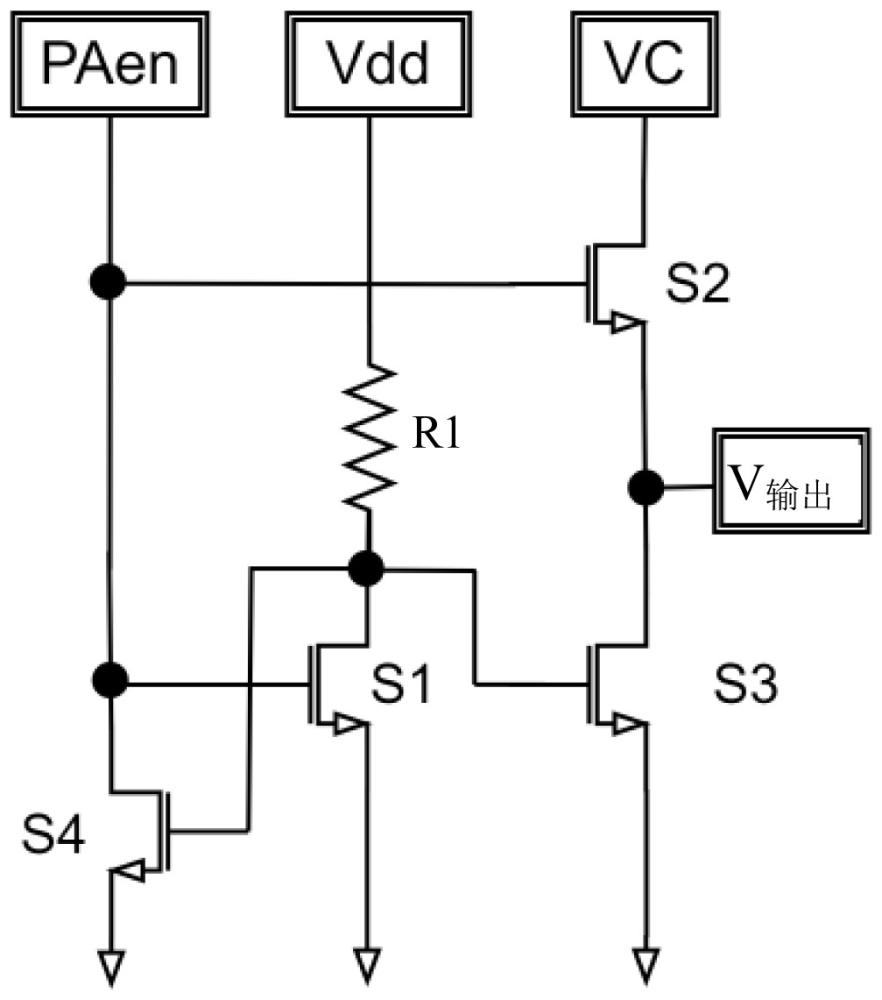

9、图5为现有技术pa开关电路架构,paen是pa控制信号引脚,通常输入由高低电平组成的方波信号。vdd为开关的电源电压,vc是pa工作的参考偏置电压,由片外电源提供,vgs是连接放大管栅极的偏置电压,给片内放大管提供偏置电压。

10、整个开关的电路的工作模式如下,假设高电平用“1”表示,低电平用“0”表示。当paen为高电平“1”时,管子s1的栅极为高电平“1”,s1开启导通,此时s1的漏级被拉到低电平为“0”,于是s3的栅极也为“0”,s3断开。此时,s2的栅极为高电平“1”,s2开启导通,于是vc电压传送给vgs,vgs和vc电压相等,vgs给放大管进行偏置,整个pa模块开始工作,整个逻辑见图6-1。

11、相反的,当paen为低电平“0”时,管子s1的栅极为低电平“0”,s1断开,此时s1的漏级被拉到高电平为“1”,于是s3的栅极也为“1”,s3开启导通,s3将vgs的电压下拉到低电平“0”。此时,s2的栅极为低电平“0”,s2断开。此时vgs电位被导通的s3拉到低电平“0”,无法给pa提供正常偏置,pa模块不工作。整个逻辑见图6-2。图6展示了开关正常工作的两个状态,通过paen信号控制vgs是否正常偏置pa,从而控制整个pa工作状态。

12、在图5的电路中,开关电路工作逻辑没有问题,但是有一个缺点就是漏电大。paen串联一个电阻r1到地,r1的作用是给paen从高电平到低电平切换时提供一个泄流电路。但当paen为高电平时,r1上产生恒定的压降,进而导致r1上一直会有漏电流,漏电流的大小为i=vpaen/r,这个漏电流对pa模块来说会产生额外的热耗散,降低pa模块的整体效率。漏电流越大,pa模块的效率越低。

13、图7-1至图7-3为图5所示的pa开关电路的开关时序及漏电瞬态仿真图。

14、图7-1为图5所示pa开关电路的vgs跟随使能信号paen的工作状态的示意图。横坐标time代表时序仿真时间,单位是μs(微秒)。 纵坐标tran.ven_up.v表示加在paen支路上的方波(即虚线方波为使能信号paen)上的方波随着时间的电压波形图,单位为v(伏特),纵坐标tran.vbias.v表示vgs随着时间的电压波形图,单位为v(伏特)。

15、图7-2为paen支路上随时间的瞬态漏电的示意图。横坐标time是时间,单位是μs(微秒)。纵坐标tran.paen.i是paen支路上随着电路不同工作状态下产生的漏电流,电流单位为ma(毫安)。

16、图7-3为图7-2中漏电mk1和漏电mk2的数值表。如图7-1、图7-2和图7-3所示,paen为高电平,vgs也为高电平,pa工作,此时漏电为1000ua(mk1标识),这个漏电越大,pa产生的额外的热耗也越大,对整体功率放大器效率的影响也越大。

17、现有技术doherty分立pa方案(图1),集成度低,应用占用面积大。

18、现有技术doherty集成pa方案中(图2),未集成pa开关控制模块在片内,需要片外提供,成本较高。

19、现有技术doherty集成pa方案中(图4),集成pa开关控制模块在片内,集成度较高,但使用开关架构存在漏电大的问题,降低整个pa模块的效率。

20、在背景技术中公开的上述信息仅用于加强对本技术的背景的理解,因此其可能包含没有形成为本领域普通技术人员所知晓的现有技术的信息。

技术实现思路

1、本技术实施例提供了一种适用于功率放大器芯片的控制电路、功率放大器芯片,以解决传统的控制电路存在的漏电较大的技术问题。

2、根据本技术实施例的第一个方面,提供了一种适用于功率放大器芯片的控制电路,包括:

3、电源电压电路,连接电源电压vdd和接地;

4、偏置电压电路,连接偏置电压vc和接地,所述偏置电压电路的一个电压输出位置用于为功率放大器提供偏置电压;

5、具有泄流开关管的泄流电路,连接使能信号paen和接地;

6、所述使能信号paen为高电平,控制所述电源电压电路导通且所述电压输出位置为功率放大器供电时,所述泄流开关管断开。

7、根据本技术实施例的第二个方面,提供了一种功率放大器芯片,包括:

8、功率放大器芯片本体;

9、上述控制电路,所述控制电路的电压输出位置和所述功率放大器芯片本体连接用于所述功率放大器芯片本体提供偏置电压。

10、本技术实施例由于采用以上技术方案,具有以下技术效果:

11、本技术实施例的适用于功率放大器芯片的控制电路,使能信号paen为高电平,控制所述电源电压电路导通且所述电压输出位置为功率放大器供电时,所述泄流开关管断开,使得泄流电路漏电极小,进而使得控制电路本身的漏电极小,基本可以忽略漏电,控制电路的效率较高。

本文地址:https://www.jishuxx.com/zhuanli/20240830/285619.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 YYfuon@163.com 举报,一经查实,本站将立刻删除。