具有管芯安装的稳压器的3D半导体封装的制作方法

- 国知局

- 2024-09-11 14:36:48

背景技术:

1、电子系统采用稳压器来向系统的各种部件提供调节的供电电压。传统上,稳压器被实现为电路板处的分立部件,在该电路板上安装有一个或多个半导体封装和其他部件。然而,由于从板到封装的相对较长的布线路径会引入电感和/或电容负载,因此板级稳压器会经历相对较大的寄生损耗,特别是对于高性能系统的高功率递送要求而言。

2、为了解决板级电压调节器引起的寄生损耗问题,一些系统改为采用封装级电压调节,其中一个或多个电压调节器安装到半导体封装的封装基板上。虽然此类解决方案可以减小总传输路径长度并因此减少寄生损耗,但仍然需要将功率从安装在基板上的稳压器穿过封装基板递送到封装的一个或多个芯片,这会继续给功率分配网络引入阻抗,同时也会消耗有限的封装布线资源。鉴于这些限制,其他系统采用全集成稳压器(fivr),其中稳压器的电路与片上系统(soc)的其余部分或该管芯的其他电路直接在同一硅管芯中实现。虽然这可有效地最小化功率递送网络长度并因此呈现最小电感,但是硅管芯通常使用先进的制造工艺来制造,因此使用fivr增加了硅管芯相对昂贵的有源管芯面积或者以其他方式与其他电路功能的电路竞争,从而导致在面积、功率、性能和成本方面产生不期望的折衷。

技术实现思路

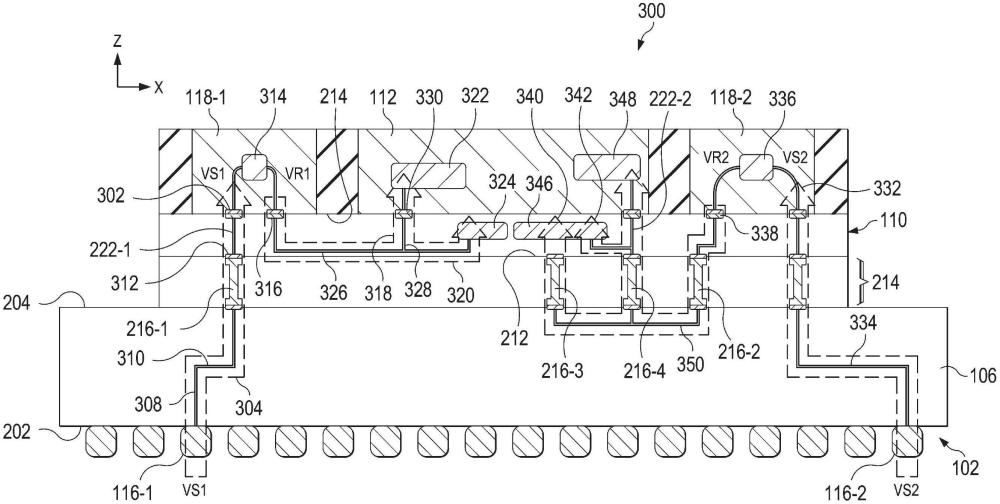

1、根据一个方面,一种半导体封装包括:封装基板,该封装基板具有第一表面和相对的第二表面;第一集成电路(ic)管芯,该第一集成电路(ic)管芯设置在该第二表面处并且具有面向该第二表面的第三表面和相对的第四表面,该第一ic管芯具有第一区域和第二区域,该第一区域包括用于该第一ic管芯的一个或多个功能的一个或多个金属层和电路部件,该第二区域在平行于该第三表面和该第四表面的方向上从该第一区域偏移;稳压器,该稳压器设置在该第二区域中的该第四表面处并且具有被配置为接收供电电压的输入端和被配置为提供调节电压的第一输出端;以及第一导电路径,该第一导电路径将该稳压器的该第一输出端耦合到该第一ic管芯的电路的电压输入端。

2、根据另一方面,一种半导体封装包括:封装基板,该封装基板具有第一表面和相对的第二表面;集成电路(ic)管芯的三维(3d)堆叠,该三维(3d)堆叠安装在该第二表面处,该3d堆叠包括ic管芯的多个管芯层;稳压器,该稳压器安装到该3d堆叠的第一管芯层的第一ic管芯并且在平行于该第二表面的方向上邻近于该3d堆叠的第二管芯层的第二ic管芯;以及一组第一导电路径,该组第一导电路径将该稳压器的一个或多个输出端导电地耦合到该第一ic管芯或该第二ic管芯中的一者或两者的电路;以及第二导电路径,该第二导电路径至少通过该第一ic管芯和该封装基板将该稳压器的输入端导电地耦合到设置在该封装基板的该第一表面处的封装互连件。

技术特征:1.一种半导体封装,所述半导体封装包括:

2.根据权利要求1所述的半导体封装,其中所述第一导电路径包括:

3.根据权利要求1所述的半导体封装,其中所述第一导电路径包括:

4.根据权利要求1所述的半导体封装,其中所述第一导电路径包括:

5.根据权利要求1至4中任一项所述的半导体封装,所述半导体封装还包括:

6.根据权利要求1至4中任一项所述的半导体封装,其中所述半导体封装是堆叠管芯封装,所述堆叠管芯封装还包括:

7.根据权利要求6所述的半导体封装,其中所述第一输入端和所述第二输入端是相同的输入端。

8.根据权利要求6或权利要求7所述的半导体封装,其中所述第二导电路径包括:

9.根据权利要求6或权利要求7所述的半导体封装,其中所述第二导电路径包括:

10.根据权利要求6或权利要求7所述的半导体封装,其中所述第二导电路径包括:

11.根据权利要求6或权利要求7所述的半导体封装,所述半导体封装还包括:

12.根据权利要求11所述的半导体封装,其中所述第一输出端、所述第二输出端和所述第三输出端中的至少两个是所述稳压器的相同输出端。

13.根据权利要求11所述的半导体封装,其中:

14.根据权利要求1所述的半导体封装,所述半导体封装还包括:

15.根据权利要求14所述的半导体封装,其中:

16.根据权利要求1所述的半导体封装,其中所述稳压器是安装在所述第一ic管芯的所述第四表面处的ic封装。

17.根据权利要求1所述的半导体封装,其中所述稳压器包括安装在所述第一管芯的所述第四表面处的ic封装和安装在所述第一ic管芯的所述第四表面处的一个或多个单独的分立电路部件。

18.根据权利要求1所述的半导体封装,其中所述稳压器是安装在所述第一ic管芯的所述第四表面处的一组分立电路部件。

19.一种半导体封装,所述半导体封装包括:

20.根据权利要求19所述的半导体封装,其中所述一组第一导电路径包括使用所述第一管芯的正面金属层的至少一个导电路径。

21.根据权利要求19所述的半导体封装,其中所述一组第一导电路径包括使用所述第一ic管芯的背面金属层的至少一个导电路径。

22.根据权利要求19所述的半导体封装,其中所述一组第一导电路径包括使用所述封装基板的金属层的至少一个导电路径,所述金属层在所述第一ic管芯与所述第二ic管芯之间横向延伸。

23.根据权利要求19所述的半导体封装,其中:

技术总结一种半导体封装包括封装基板,该封装基板具有第一表面和相对的第二表面;并且还包括集成电路(IC)管芯,该集成电路(IC)管芯设置在该第二表面处并且具有面向该第二表面的第三表面和相对的第四表面。该IC管芯具有第一区域和第二区域,该第一区域包括用于该IC管芯的一个或多个功能的一个或多个金属层和电路部件,该第二区域在平行于该第三表面和该第四表面的方向上从该第一区域偏移。该半导体封装还包括稳压器,该稳压器设置在该第二区域中的该第四表面处并且具有被配置为接收供电电压的输入端和被配置为提供调节电压的输出端;并且还包括导电路径,该导电路径将该稳压器的该输出端耦合到该IC管芯的电路的电压输入端。技术研发人员:加布里埃尔·H·洛,拉贾·斯瓦米纳坦,拉胡尔·阿加瓦尔,布雷特·P·威尔克森受保护的技术使用者:超威半导体公司技术研发日:技术公布日:2024/9/9本文地址:https://www.jishuxx.com/zhuanli/20240911/291578.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 YYfuon@163.com 举报,一经查实,本站将立刻删除。

上一篇

电子断路器的制作方法

下一篇

返回列表